最近幾年的芯片領域,RISC-V是一個絕對繞不過的關鍵詞。

和X86和Arm不一樣,指令集架構RISC-V因為擁有開放性,先進性,模塊化和可擴展等特點,尤其是本身的開源屬性,使得它不會受到任何單一公司的沉浮或者一時興起的決定的影響。在這些多種因素的推動下,這個指令集從2011年開始走熱,過去兩年更吸引了國內芯片創業者的狂熱追捧。

為了指導 RISC-V 指令集架構的未來發展并推動其應用,非營利性組織RISC-V 基金會于2015年成立,經過近四年的發展,目前成員數量已達到235家。日前,基金會首次在中國五座城市組織了路演,來自RISC-V領域的多個企業講述了他們在這個領域布局和想法。

RISC-V可以怎么玩?

據網上資料顯示,RISC-V是一個典型三操作數,加載-存儲形式的 RISC 架構,擁有 3 個基本指令集和 6 個擴展指令集。其中基本整數指令集體系結構 ISA 能夠通過添加一個或者多個可選的指令集擴展來進行功能的增強。這種靈活性就能給開發者帶來了太多的選擇和玩法。

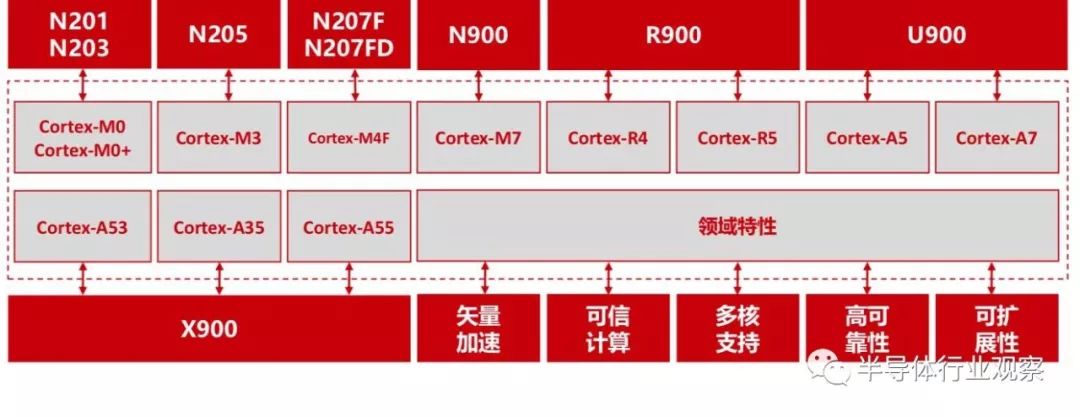

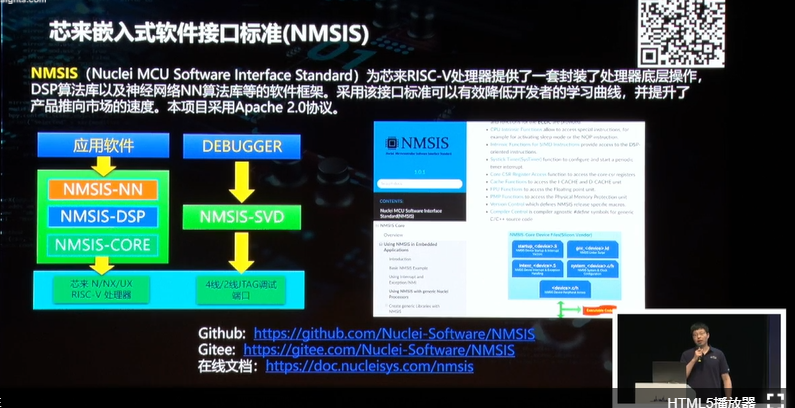

首先看專注于RISC-V處理器內核IP與解決方案的芯來科技,據該公司創始人胡振波先生介紹,他們已經目前已經發布了面向AIoT的超低功耗產品線N200系列,這系列32位超低功耗RISC-V處理器是他們專為物聯網IoT終端設備的感知,連接,控制以及輕量級智能應用而設計的,從性能上看,可以直接替代arm 的Cortex-M系列。

芯來科技的N200系列

與此同時,他們還在研發面向邊緣計算的嵌入式高性能產品線N900系列。其中N900系列32位處理器在功耗和性能上具有極佳的平衡性面向民用邊緣計算領域,R900系 列32位處理器面向高可靠性和實時控制領域,U900系列32位和X900系列64位處理器,配合多核支持,矢量加速,以及可擴展特性,以及對Linux的支持,主要面向5G和數據中心網絡通訊領域,以及多媒體,嵌入式AI等。這同樣可以找到arm領域內的匹配者。

芯來科技目前的產品線

胡振波指出,芯來的目標是以處理器為平臺,和客戶深度合作,從客戶業務需 求出發提供處理器定制服務。他們同事還推出了一項RISC-V處理器內核IP普惠計劃——一分錢計劃。據介紹,參與這個計劃的開發者,可以從芯來科技輕松免費獲取商用的RISC-V處理器內核N201,而在大規模量產時,芯來科技也僅向每顆芯片收取人民幣一分錢的版稅(Royalty),相對于開發者來說,這也是他們進入相關領域的一個捷徑。

其次看阿里巴巴旗下的平頭哥半導體。作為RISC-V基金會的鉑金會員,他們除了推出了世界上首個帶有TEE的嵌入式RISC-V內核902外,他們還規劃了903、905、907、910和960等多代RISC-V處理器。他們也針對不同的應用領域,規劃了多個系列的產品線。公司也正在積極參與RISC-V的生態建設中去。

平頭哥的RISC-V產品線

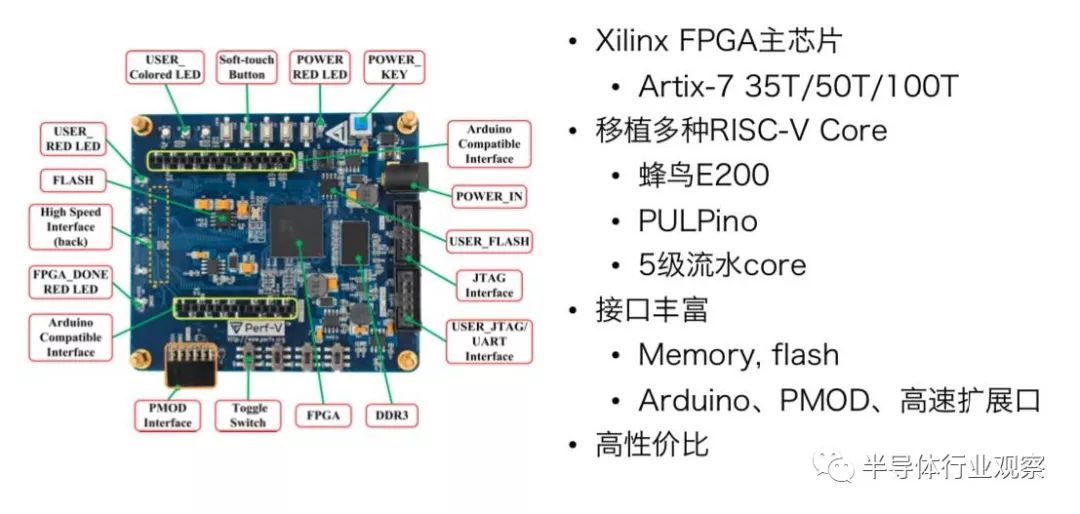

源自中科院、專注于嵌入式AI解決方案的團隊澎峰科技則推做了一個名為“Perf“的開發版。據該公司張先軼先生介紹,他們認為RISC-V是體系結構領域的“Linux”,而RISC-V+AI則能爆發出巨大的應用潛力。

澎峰科技的Perf-v開發板

按照他的設想,他們以FPGA為主芯片,加入多種RISC-V軟核的Perf-v開發板擁有配套工具成熟,外設借口豐富、性價比高,且還有醫用、案例豐富等特性,能夠為開發者提供多樣化的服務。

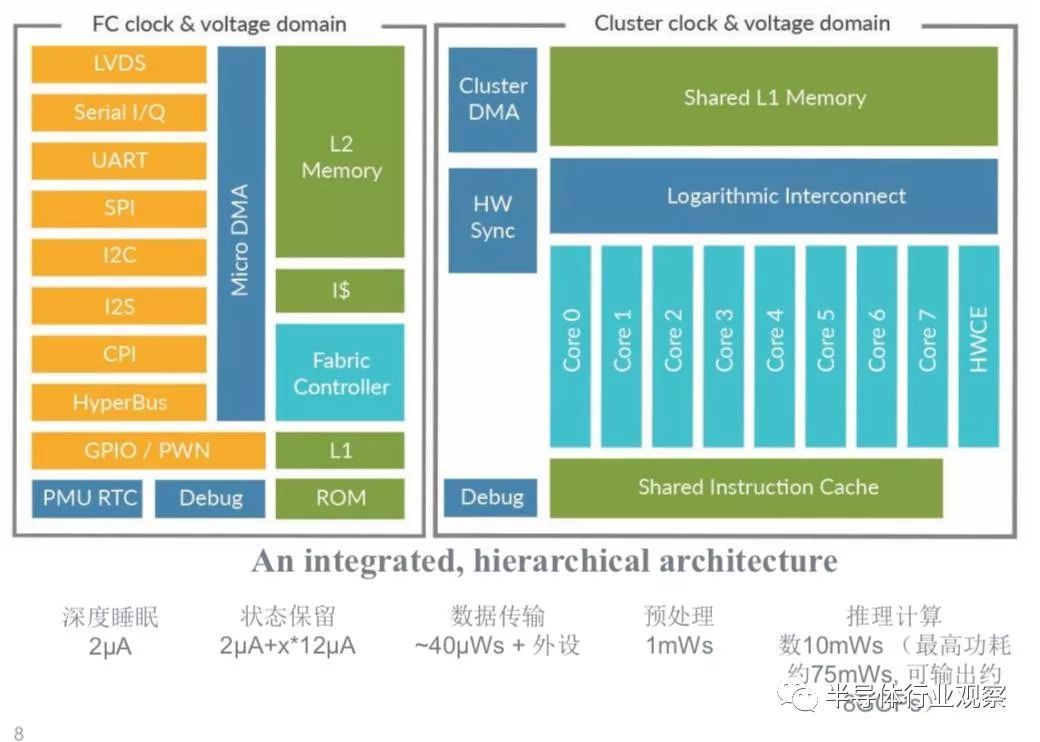

成立于2014年的法國GreenWaves Technologies則將RISC-V核心應用到其高集成度的新型智能MCU GAP8中。據GreenWaves 張垚先生介紹,他們的物聯網應用處理器可以分為兩部分。其中微控制器部分使用了一顆經擴展的RISC-V內核,而計算加速部分使用了8顆基于RISC-V的擴展內核。在這個基礎上加上各種外設、I/O,加上其高能效平衡的并行架構、共享指令集、硬件卷積加速引擎和快速的能源狀態切換支持,這就給GAP8帶來了極致的能耗,為使用電池的應用場景帶來高能耗的端側AI計算能力。

GreenWaves Technologies的GAP 8

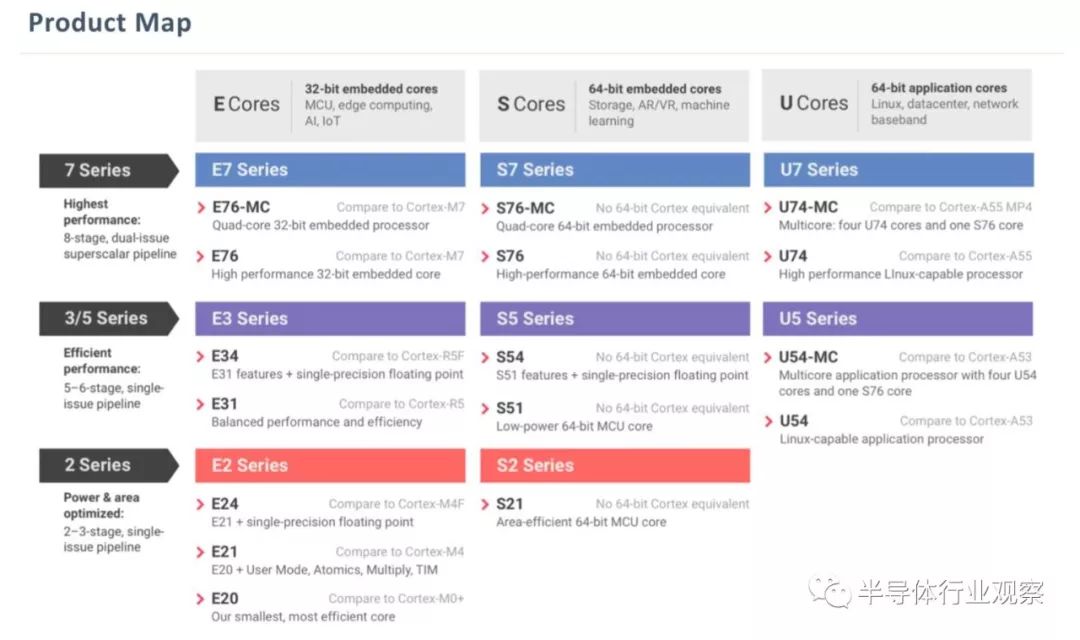

作為最早涉足RISC-V的廠商之一,SiFive則推出了2系列、3/5系列和7系列這幾個針對不同應用場景的RISC-V產品線。在他們看來,這些產品能夠為存儲、5G/網絡、AR/VR/傳感器融合、企業級SSD、邊緣人工智能、可穿戴AI等應用和市場提供支持。

SiFive的產品線

***IP供應傻晶心科技則憑借著超過14年的商用CPU開發經驗、全球累積超過160家客戶以及35億顆的量產紀錄,加上自家開發環境IDE(AndeSight)和既有的DSP & ACE所擁有的優勢讓Andes在RISC-V市場有一席之地。從2017年推出N25/NX25開始,到2018年發布A25/AX25,再到今年的N22 & D25和接下來即將推出的A25MP/AX25MP,RISC-V正在一步步完善其產品布局,未來甚至還會推出更多級流水線高性能RISC-V CPU,滿足市場的需求。

解決現有的問題方法?

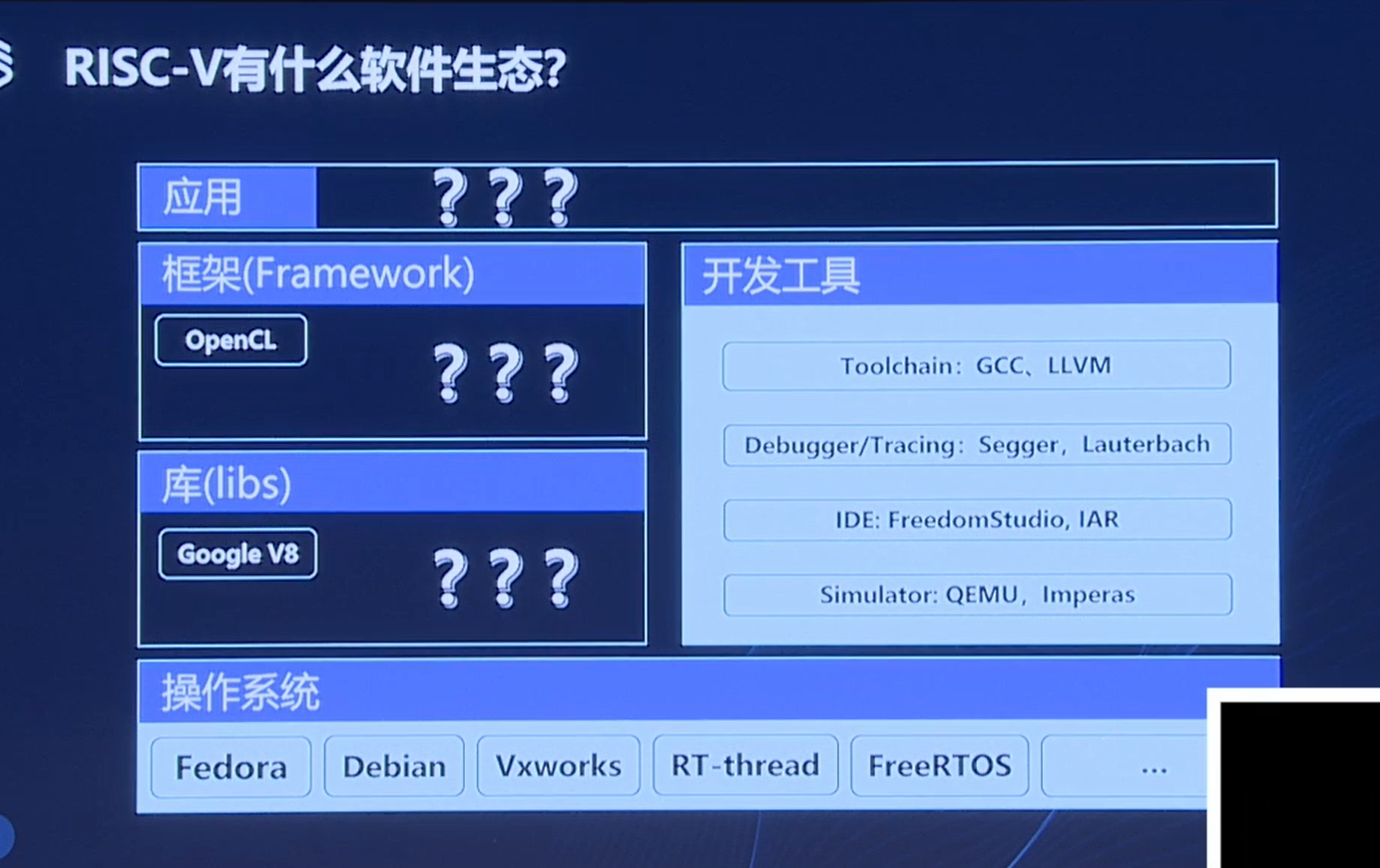

在和很多RISC-V從業者交流的時候,他們都無一例外的告訴半導體行業觀察記者,RISC-V面臨的一個最大挑戰就是生態問題或者工具問題,但其實也有很多廠商投入其中。

例如在RISC-V的一大特點指令客制方面化,過去這些操作需要開發者擁有豐富CPU專業知識及大量人力來修改既有的處理器硬件和相關軟件工具,并確認其功能無誤,因此加入客制化指令對許多SoC設計團隊來說并不容易。但透過晶心科技的ACE設計環境,即可大幅簡化加入客制化指令的步驟。

據介紹,ACE最強大的功能是能以高階語法來描述指令,并自動產生RTL電路。例如,向量語法讓開發者能像設計純量指令一樣輕鬆設計出向量指令,背景語法則能讓需較長時間執行的ACE指令持續在背景同步執行,工程師亦能利用自訂暫存器及自訂記憶體能設定任意位元寬度的特點,讓ACE指令執行寬位元的輸入和輸出,而這些ACE功能都有助處理器效能大幅提升。另外,COPILOT除了能容易地產生工具鏈,也能自動產生測試向量和交叉驗證環境,幫工程師驗證所設計的指令是否正確,讓設計驗證更為容易。

晶心科技方面強調,COPILOT設計環境是自動產生ACE指令的關鍵,能幫助SoC設計團隊省去許多底層RTL設計工作,例如運算碼選取、指令解碼、運算元參照、輸入運算元存取、資料相依性檢查及結果彙整。ACE相當易于使用,不需熟悉處理器管線設計也能快速上手,這讓工程師能專注于利用ACE強大的功能,而不是花費時間摸索CPU管線的運作方式。

那就意味著工程師只須建立一個ACE描述檔來定義輸入/輸出介面及以C語言描述的指令意涵,再加上一個相對應的精簡Verilog檔來描述其邏輯電路,即可利用Custom-OPtimized Instruction deveLOpment Tools (COPILOT) 工具于短短數分鐘內產生具擴充指令的CPU和相關軟件工具鏈。

為SoC提供部分析及監測技術的先鋒企業UltraSoC則為RISC-V設計帶來了更多的支持。

2018年初,該公司宣布推出業界第一款也是唯一一款專為RISC-V設計的商用追蹤編碼器IP,提供了一種實時監控CPU程序執行的機制。 它對指令執行和數據內存訪問進行編碼(可選),并輸出一種高度壓縮的追蹤格式。 外部軟件可以隨后獲取此數據并使用它來重建程序執行流程。 UltraSoC方面表示,他們的RISC-V追蹤編碼器是為符合RISC-V標準而開發的,同時提供許多強大的功能,如數據和指令追蹤、一系列計數器和定時器以及快速分析描繪工具,使其與實現基線RISC-V標準要求的開源代替產品明顯不同。

“RISC-VTrace Encoder追蹤編碼器支持32位和64位RISC-V設計,該IP塊可與UltraSoC產品組合的其他部分順利集成,支持開放式和行業標準架構,以將自分析功能置于SoC的核心”,Ultra SoC方面補充說。

在2019年嵌入式世界展上,Ultra SoC宣布,他們的UltraDevelop 2集成開發環境(IDE)可用于beta測試。據了解,這個發布于2018年10月的產品集成了調試、運行控制和性能調優功能,可為硬件、固件和軟件的運行提供集成化的視圖,以及高級異常檢測、可視化和數據科學等功能。利用UltraSoC系統級的片上監控和分析基礎架構的巨大潛力,為SoC設計人員在選擇開發平臺時提供功能和靈活性的最佳組合,并且有能力對來自RISC-V等供應商的20多種處理器架構進行實時運行控制,幫助芯片和系統開發人員提供可操作的洞察力,從而大幅降低開發成本和縮短產品上市時間,并改善最終產品的整體質量。

從整個處理器架構市場來看,RISC-V相對還是比較薄弱,但相信在RISC-V 基金會的推動、以及各大企業的支持下,我們很快就能看到這個全新的架構在各個領域大放異彩,這個產品屆時也必將給中國芯片產業帶來全新的局面。

-

芯片

+關注

關注

459文章

52465瀏覽量

440301 -

開發板

+關注

關注

25文章

5661瀏覽量

104458

發布評論請先 登錄

對于RISC-V的相關分析和介紹

對于RISC-V的相關分析和介紹

評論