摘 要: 討論了用偽隨機(jī)序列實(shí)現(xiàn)程序加密保護(hù)及其可編程邏輯器件實(shí)現(xiàn)的原理、方法和具體操作,給出了在微機(jī)軟件和單片機(jī)/DSP系統(tǒng)中程序加密的實(shí)際運(yùn)用舉例。

可編程邏輯器件(PLD)經(jīng)歷了PAL、GAL、CPLD 和FPGA幾個發(fā)展階段。使用PLD具有設(shè)計靈活、調(diào)試方便、系統(tǒng)可靠性高等眾多優(yōu)點(diǎn),并有利于硬件設(shè)計的保護(hù),防止他人對電路的分析、仿照,使其成為科研實(shí)驗(yàn)、樣機(jī)試制和小批量產(chǎn)品的首選方案。

隨著計算機(jī)、單片機(jī)技術(shù)的發(fā)展和廣泛應(yīng)用,軟件加密成為知識產(chǎn)權(quán)保護(hù)的重要手段。目前微機(jī)軟件加密的方法可分為兩大類:軟加密和硬加密。軟加密主要有密碼方式、軟件自校驗(yàn)方式、鑰匙盤方式等多種。隨著軟加密的發(fā)展,解密軟件也大量出現(xiàn)。硬加密由于具有加密強(qiáng)度大、可靠性高等特點(diǎn),已廣泛用于微機(jī)軟件保護(hù)。硬加密將硬件和軟件相結(jié)合來實(shí)現(xiàn)軟件的加密,軟件在運(yùn)行時需與硬件正確交換數(shù)據(jù),否則程序不運(yùn)行,或不能執(zhí)行主要功能,典型的產(chǎn)品有:插在計算機(jī)總線上的加密卡,接在計算機(jī)并口或USB口的軟件狗(加密鎖)、微狗等。軟件狗大多用E2PROM存儲密碼數(shù)據(jù),電路簡單,成本低,但用SOFT-ICE等軟件進(jìn)行軟件狗的解密和復(fù)制并不很困難。在這種情況下,軟件狗內(nèi)部增加了一個單片機(jī)稱為微狗,通過對數(shù)據(jù)的處理來提高軟件的加密強(qiáng)度;少數(shù)專業(yè)的硬加密生產(chǎn)商則采用獨(dú)自的ASIC芯片。加密卡的原理與軟件狗和微狗的相似,不同的是通過總線操作,使得設(shè)計更靈活、功能更強(qiáng),只是安裝不方便。

隨著某一加密產(chǎn)品加密操作方式的公開,其解密也就為期不遠(yuǎn)。新出現(xiàn)的解密軟件能模擬絕大部分軟件與加密狗間的數(shù)據(jù)交換過程,從而達(dá)到解密;國產(chǎn)的加密卡和微狗,大多外用E2ROM存儲配置數(shù)據(jù)和用戶密碼,獲取這些數(shù)據(jù)就可能解密、甚至復(fù)制微狗,因此加密方法的獨(dú)特性、手法的反常規(guī)性在加密應(yīng)用中非常重要。單片機(jī)/DSP系統(tǒng)的控制及外圍電路都相對簡單,對軟件的跟蹤比較容易分析硬件的設(shè)計思想和實(shí)現(xiàn)功能,而目前對其軟件的保護(hù)并不受重視,并且單片機(jī)/DSP系統(tǒng)沒有現(xiàn)成的加密產(chǎn)品,設(shè)計者應(yīng)結(jié)合系統(tǒng)軟、硬件的要求靈活決定。我們利用PLD器件本身的加密保護(hù)特性,由其產(chǎn)生的偽隨機(jī)序列實(shí)現(xiàn)單片機(jī)/DSP系統(tǒng)和計算機(jī)應(yīng)用程序的加密,具有簡單方便,解密難度大的特點(diǎn),同樣可用PLD器件實(shí)現(xiàn)更復(fù)雜的加密方法如 EDS。

1 硬件加密的PLD實(shí)現(xiàn)原理

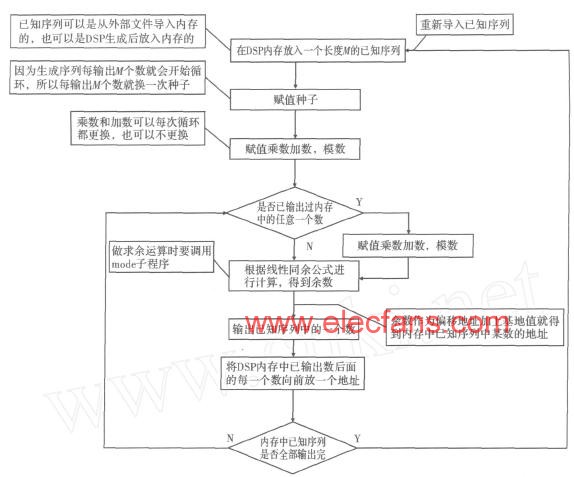

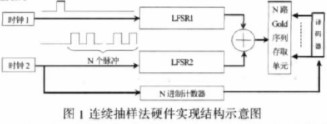

硬件加密必須綜合考慮加密方法的可行性、有效性、硬件復(fù)雜度等因素,由邏輯電路產(chǎn)生大量密碼的一種簡單有效的方法是使用線性反饋移位寄存器,其產(chǎn)生的偽隨機(jī)數(shù)據(jù)已廣泛用于數(shù)據(jù)通信中的加擾、擴(kuò)頻、跳頻和數(shù)據(jù)加密。圖1所示是具有防跟蹤、產(chǎn)生2N-1個N 位偽隨機(jī)數(shù)據(jù)的加密電路原理框圖,密碼生成所用觸發(fā)器和門電路少,并且密碼是加電后動態(tài)產(chǎn)生的,不同的預(yù)置產(chǎn)生的數(shù)據(jù)不同,因此密碼的強(qiáng)度、隱蔽性優(yōu)于加密狗和微狗(卡)。

N位移位寄存器產(chǎn)生的偽隨機(jī)碼作為讀取的密碼或輸入數(shù)據(jù)解密的密鑰,在移位時鐘的作用下,可輸出2N-1個N位的有效密碼或密鑰。對某一具體電路,移位寄存器初值不同時,這2N-1個隨機(jī)數(shù)有2N-1種排序,可預(yù)置偽隨機(jī)數(shù)產(chǎn)生器的原理電路如圖2所示。要使移位寄存器產(chǎn)生一確定的值,首先置其初值,然后置移位計數(shù)器初值并允許時鐘電路產(chǎn)生移位時鐘;當(dāng)移位計數(shù)器計滿時,產(chǎn)生一個數(shù)據(jù)準(zhǔn)備好狀態(tài)可供軟件讀取,該狀態(tài)同時阻斷時鐘電路,停止移位操作,并且啟動防跟蹤記數(shù)器的時鐘產(chǎn)生電路;若在規(guī)定的時間內(nèi)讀取密碼字或者寫入待解密數(shù)將清零防跟蹤記數(shù)器,否則超時使防跟蹤記數(shù)器滿導(dǎo)致觸發(fā)器翻轉(zhuǎn),打開三態(tài)門,擾亂輸出數(shù)據(jù),雖然這時讀/寫數(shù)據(jù)能清零防跟蹤記數(shù)器,阻斷其時鐘,但必須重加電或系統(tǒng)復(fù)位才能斷開三態(tài)門。

N位移位寄存器產(chǎn)生的偽隨機(jī)碼作為讀取的密碼或輸入數(shù)據(jù)解密的密鑰,在移位時鐘的作用下,可輸出2N-1個N位的有效密碼或密鑰。對某一具體電路,移位寄存器初值不同時,這2N-1個隨機(jī)數(shù)有2N-1種排序,可預(yù)置偽隨機(jī)數(shù)產(chǎn)生器的原理電路如圖2所示。要使移位寄存器產(chǎn)生一確定的值,首先置其初值,然后置移位計數(shù)器初值并允許時鐘電路產(chǎn)生移位時鐘;當(dāng)移位計數(shù)器計滿時,產(chǎn)生一個數(shù)據(jù)準(zhǔn)備好狀態(tài)可供軟件讀取,該狀態(tài)同時阻斷時鐘電路,停止移位操作,并且啟動防跟蹤記數(shù)器的時鐘產(chǎn)生電路;若在規(guī)定的時間內(nèi)讀取密碼字或者寫入待解密數(shù)將清零防跟蹤記數(shù)器,否則超時使防跟蹤記數(shù)器滿導(dǎo)致觸發(fā)器翻轉(zhuǎn),打開三態(tài)門,擾亂輸出數(shù)據(jù),雖然這時讀/寫數(shù)據(jù)能清零防跟蹤記數(shù)器,阻斷其時鐘,但必須重加電或系統(tǒng)復(fù)位才能斷開三態(tài)門。

對加密電路的正確操作步驟是:在主程序中預(yù)置移位計數(shù)器和移位寄存器初值,在子程序的一處判斷移位是否完成,另一處讀密碼或?qū)懘饷軘?shù),在另一子程序判斷或取解密數(shù)據(jù),以防止跟蹤。

為在使用較少觸發(fā)器情況下保證程序正常運(yùn)行并能有效地防止解密跟蹤,應(yīng)恰當(dāng)?shù)剡x擇防跟蹤計數(shù)器的時鐘,若用移位寄存器時鐘源,則需要較高的分頻才能滿足高速的數(shù)據(jù)產(chǎn)生、適當(dāng)?shù)难訒r時間;因此在實(shí)際使用中,應(yīng)根據(jù)需要,選擇系統(tǒng)可能提供的低頻持續(xù)脈沖信號作為防跟蹤計數(shù)器的時鐘。在微機(jī)系統(tǒng)中,尤其在WINDOWS操作系統(tǒng)的分時事件驅(qū)動運(yùn)行模式下,由于系統(tǒng)固有的存儲器刷新、時鐘中斷,以及運(yùn)行中硬件中斷、DMA操作、任務(wù)切換,必須有較長的防跟蹤延時才能保證合法程序正常運(yùn)行,要注意在軟硬盤操作時對密碼數(shù)據(jù)操作的影響。

2 應(yīng)用舉例

2.1 并行口加密電路

2.1 并行口加密電路

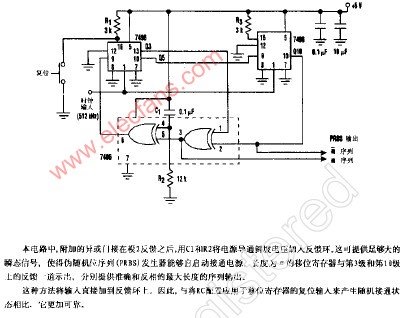

在PC機(jī)系統(tǒng)中,一般打印機(jī)并行接口包括單向輸出的8條數(shù)據(jù)線D0~D7和四條控制線、5條狀態(tài)輸入線,因此每次讀操作只讀取4bits密碼,其加密電路原理框圖如圖3所示。由于并行口不提供電源,將聯(lián)機(jī)控制信號SLCT置高提供的電流很小,因此直接掛在并行口上的電路必須選用規(guī)模不大的低功耗器件。

經(jīng)并行口控制移位寄存器產(chǎn)生密碼的基本操作步驟是:(1)SLCT置高加電;(2)STROBE觸發(fā)經(jīng)D0~D8寫入16位控制字,選通加密電路,否則打印口正常;(3)初始化信號INIT置低,STROBE選擇預(yù)置移位寄存器和移位計數(shù)器;(4)INIT置高選通移位時鐘;(5)檢測數(shù)據(jù)是否準(zhǔn)備好;(6)換行控制AUTO LF置高,在STROBE脈沖作用下數(shù)據(jù)按4bits輸出供CPU讀取;(7)SLCT置低斷電。

防跟蹤記數(shù)器由移位計數(shù)器滿狀態(tài)啟動,其溢出脈沖使觸發(fā)器翻轉(zhuǎn)選通三態(tài)門,擾亂輸出數(shù)據(jù)。防跟蹤記數(shù)器和移位寄存器時鐘可由門電路構(gòu)成的RC振蕩器產(chǎn)生。

2.2 ISA總線加密電路

與并行口方式相比,通過總線方式對加密電路的移位寄存器和移位記數(shù)器的預(yù)置、輸入數(shù)據(jù)的異或解密等操作更靈活、方便,并可與其它電路結(jié)合,其原理框圖與圖1相似。總線接口電路對端口地址和控制信號譯碼,產(chǎn)生移位寄存器和移位記數(shù)器輸入寫、移位寄存器及異或解密輸出讀信號,讀信號清零防跟蹤記數(shù)器并阻斷其時鐘。在ISA總線接口中,移位寄存器時鐘用OSC或總線時鐘BCLK,而防跟蹤記數(shù)器時鐘可采用移位時鐘或狀態(tài)持續(xù)變化的總線控制信號及狀態(tài)信號,如:地址鎖存信號BALE、刷新指示信號REFRESH、DMA操作允許信號AEN(因用于I/O地址譯碼,隱蔽性好)等,用REFRESH信號時計數(shù)器規(guī)模小、運(yùn)行可靠,但是切斷該信號防跟蹤功能不起作用,密碼數(shù)據(jù)仍正常產(chǎn)生。

2.3 單片機(jī)/ DSP系統(tǒng)程序加密電路

早期的單片機(jī)系統(tǒng)大都用擴(kuò)展EPROM作為程序存儲器,這種方式目前在高速單片機(jī)/DSP中仍然很常用。對于程序量小,不需外部程序?qū)ぶ返暮唵蜗到y(tǒng)(如微狗),采用內(nèi)置EPROM/FLASH RAM、帶加密控制字的MCU(如GMS97C2051)本身就能可靠地保護(hù)程序;因此我們的討論只限于用擴(kuò)展程序存儲器的系統(tǒng)。

早期的單片機(jī)系統(tǒng)大都用擴(kuò)展EPROM作為程序存儲器,這種方式目前在高速單片機(jī)/DSP中仍然很常用。對于程序量小,不需外部程序?qū)ぶ返暮唵蜗到y(tǒng)(如微狗),采用內(nèi)置EPROM/FLASH RAM、帶加密控制字的MCU(如GMS97C2051)本身就能可靠地保護(hù)程序;因此我們的討論只限于用擴(kuò)展程序存儲器的系統(tǒng)。

對擴(kuò)展程序存儲器的加密保護(hù)可通過對其數(shù)據(jù)和地址線的異或/取反擾亂來實(shí)現(xiàn),其目的都是不能直接獲取程序存儲器內(nèi)部保存的數(shù)據(jù)。由于X=X+K+K,X=X,因此在系統(tǒng)工作時由硬件實(shí)現(xiàn)代碼和密鑰的異或/取反操作可得到正確的程序(文獻(xiàn)[2]中用二級異或提高加密強(qiáng)度的觀點(diǎn)不正確,因?yàn)椋伲絏+K1+K2=X+K),其原理如圖4所示。通常單片機(jī)加密的方式是密鑰固定不變,或CPU讀取程序代碼的同時,從另一片EPROM讀取密碼,使每一代碼對應(yīng)一密鑰。這兩種方式的解密只需用簡單的組合邏輯電路,對前一種方式,用邏輯分析法很容易求解邏輯關(guān)系而解密,后一種方法進(jìn)行邏輯分析的工作量雖然大大提高,但密鑰本身容易被直接獲取。因此我們用m序列產(chǎn)生器動態(tài)產(chǎn)生密鑰,將解密的組合邏輯電路與時序邏輯相結(jié)合,而較復(fù)雜時序邏輯的分析是很困難的。

對8031、MC6085兼容系列的單片機(jī)系統(tǒng),編程使開始的一段初始化程序順序執(zhí)行,系統(tǒng)復(fù)位時自動對移位寄存器設(shè)初值,復(fù)位后程序存儲器的讀信號同時作為移位時鐘,使每條指令的密鑰不斷變化;在第一次執(zhí)行循環(huán)、跳轉(zhuǎn)指令前,程序發(fā)控制字阻斷移位時鐘,使以后的程序密鑰相同。在高速DSP系統(tǒng)中,一般上電后將低速EPROM中的程序加載到高速SRAM中運(yùn)行,可使EPROM的讀控制信號一直作為移位時鐘,使密鑰不斷變化;如果用串行口方式加載,程序解密操作與數(shù)據(jù)通信中的數(shù)據(jù)解擾相同,數(shù)據(jù)輸出時鐘直接作為移位時鐘。單片機(jī)/DSP作為微機(jī)系統(tǒng)的協(xié)處理器時,單片機(jī)/DSP的代碼一般經(jīng)總線裝載,可將加密代碼與移位寄存器輸出的密鑰異或解密,輸出到單片機(jī)/DSP的程序RAM。

系統(tǒng)運(yùn)行時,用于MCU/DSP程序保護(hù)的防跟蹤計數(shù)器時鐘一直有效,這樣可以防止仿真器的跟蹤。防跟蹤計數(shù)器要用程序讀或其相關(guān)信號清零,有的DSP從內(nèi)部RAM運(yùn)行程序時,程序讀無相應(yīng)輸出信號,這時可用定時器中斷或程序中及時插入的代碼來清零。

上述介紹應(yīng)用移位寄存器產(chǎn)生偽隨機(jī)數(shù)據(jù)對程序進(jìn)行加密的一些方法,曾在我們設(shè)計的系統(tǒng)中得到驗(yàn)證,整個電路的設(shè)計不復(fù)雜,占用PLD 器件的資源不多,完全可結(jié)合在系統(tǒng)的硬件邏輯設(shè)計中。使用8/16位的移位寄存器時,密鑰量有限,制約了加密的復(fù)雜度,使用者應(yīng)根據(jù)設(shè)計要求和自己的經(jīng)驗(yàn),引入各種非常規(guī)的操作方式,這樣就可以用簡單的硬件電路,很好地實(shí)現(xiàn)軟件和系統(tǒng)的保護(hù)。

- 偽隨機(jī)序(5146)

相關(guān)推薦

PLD/FPGA的分類和使用有哪些?

PLD/可編程邏輯器件的入門知識

PLD在消費(fèi)電子領(lǐng)域的應(yīng)用

PLD在消費(fèi)電子領(lǐng)域的應(yīng)用

PLD在消費(fèi)電子領(lǐng)域的挑戰(zhàn)

PLD的應(yīng)用

加密芯片

隨機(jī)函數(shù)不是很隨機(jī)

AES 256加密認(rèn)證芯片介紹 帶加密認(rèn)證功能的EEPROM

FPGA電路實(shí)現(xiàn):m序列及應(yīng)用

GPS數(shù)據(jù)加密系統(tǒng)的DES IP怎么實(shí)現(xiàn)?

M487芯片CRYPTO模塊中對稱加密AES功能測試方案

MATLAB中計算方式生成隨機(jī)序列

MM32 MCU加密方法

PIC16F628A中的隨機(jī)輸出

PSoC 3偽隨機(jī)序列PRC問題

PSoC 4 偽隨機(jī)序列 (PRS)

Quartus VHDL程序問題

[Mill]FPGA無線通信課程連載——擾碼的原理及實(shí)現(xiàn)

[求助] 將設(shè)計的偽隨機(jī)碼發(fā)生器組合成整體進(jìn)行調(diào)用

[求助]基于FPGA的偽隨機(jī)碼發(fā)生器的設(shè)計與實(shí)現(xiàn)

keil-O2優(yōu)化時系統(tǒng)自帶的偽隨機(jī)數(shù)會導(dǎo)致死機(jī)

stm32偽隨機(jī)的使用

【LinkIt 7687試用體驗(yàn)】8.加密算法中真隨機(jī)數(shù)的產(chǎn)生方法

【NUCLEO-F412ZG試用體驗(yàn)】之硬件隨機(jī)數(shù)。

【assingle分享】labview隨機(jī)數(shù)發(fā)生器

【原創(chuàng)】基于FPGA的M序列發(fā)生器設(shè)計

【總結(jié)】LabVIEW隨機(jī)數(shù)發(fā)生器

【鋯石A4 FPGA試用體驗(yàn)】——小炮與鋯石A4的故事(11)——基于FPGA的m序列發(fā)生器

一種基于FPGA的真隨機(jī)數(shù)發(fā)生器設(shè)計與實(shí)現(xiàn)

一種基于混沌和小波變換的大容量音頻信息隱藏算法

利用DSP系統(tǒng)實(shí)現(xiàn)多路測量信號擴(kuò)頻傳輸實(shí)現(xiàn)

基于FPGA技術(shù)的Logistic映射PN序列

基于FPGA的偽隨機(jī)序列有哪些應(yīng)用?

基于FPGA的擴(kuò)頻系統(tǒng)設(shè)計(附代碼)

如何實(shí)現(xiàn)FPGA滑動相關(guān)法偽碼捕獲?

如何利用DES加密算法對隨機(jī)數(shù)進(jìn)行加密呢

學(xué)習(xí)筆記 | 基于FPGA的偽隨機(jī)數(shù)發(fā)生器(附代碼)

定制化加密芯片優(yōu)勢和產(chǎn)品特點(diǎn)

定制型加密芯片這是一款采用隨機(jī)變量交換系統(tǒng)的認(rèn)證加密芯片,請問定制化加密芯片優(yōu)勢在哪里?

擴(kuò)頻通信系統(tǒng)的分類及原理

無線通信中的擾碼

有誰知道控制PRS偽隨機(jī)序列模塊嗎?

求教!!LabVIEW怎樣數(shù)據(jù)的隨機(jī)化

真隨機(jī)數(shù)發(fā)生器在信息安全系統(tǒng)中的應(yīng)用

通過USBN9603/P89C51平臺實(shí)現(xiàn)USB接口硬件加密

采用PLD實(shí)現(xiàn)視頻接口設(shè)計

高安全、高性能、高性價比 加密芯片 分享

高安全、高性能、高性價比 加密芯片 分享

偽隨機(jī)系列及編碼.ppt

0

0一種基于隨機(jī)序列的RFID安全協(xié)議

12

12用單片機(jī)實(shí)現(xiàn)SRAM工藝FPGA的加密應(yīng)用

24

24CDMA偽隨機(jī)碼

5

5基于隨機(jī)碼數(shù)列的文件加密算法的實(shí)現(xiàn)

28

28基于混沌序列密碼的網(wǎng)絡(luò)信息加密系統(tǒng)

22

22Galileo系統(tǒng)偽隨機(jī)序列生成及其FPGA實(shí)現(xiàn)

7

7基于PLD及FPGA的頻率與相位測量系統(tǒng)設(shè)計與實(shí)現(xiàn)

30

30基于過擬合神經(jīng)網(wǎng)絡(luò)的混沌偽隨機(jī)序列

6

6彩色圖像的雙隨機(jī)相位加密隱藏技術(shù)

28

28基于DSP的任意長度偽隨機(jī)序列產(chǎn)生方法

10

10一種混沌偽隨機(jī)序列發(fā)生器的FPGA實(shí)現(xiàn)

52

52M序列偽隨機(jī)碼在測距回答概率控制中的應(yīng)用

1529

1529

M序列偽隨機(jī)碼在測距回答概率控制中的應(yīng)用

1091

1091

偽隨機(jī)序列及PLD實(shí)現(xiàn)在程序和系統(tǒng)加密中的應(yīng)用

660

660

FPGA的偽隨機(jī)序列發(fā)生器設(shè)計

3332

3332

基于DSP的任意長度偽隨機(jī)序列產(chǎn)生方法

1997

1997

Lorenz系統(tǒng)混沌加密算法研究

30

30一類序列信號檢測器的實(shí)現(xiàn)方案

41

41基于TDERCS偽隨機(jī)序列發(fā)生器的FPGA設(shè)計與實(shí)現(xiàn)

27

27基于計算全息的菲涅爾雙隨機(jī)相位加密技術(shù)

37

37基于Altera的DSP Builder工具箱的偽隨機(jī)序列產(chǎn)生器設(shè)計方法

0

0用FPGA硬件實(shí)現(xiàn)多路偽隨機(jī)序列應(yīng)用適應(yīng)光學(xué)SPGD控制算法設(shè)計

1631

1631

混沌動態(tài)隨機(jī)分組與隨機(jī)調(diào)制FRFT旋轉(zhuǎn)因子

1

1Logistic方程混沌信號加密實(shí)現(xiàn)

1

1基于SPGD控制算法自適應(yīng)光學(xué)系統(tǒng)的偽隨機(jī)序列的設(shè)計與要求

2662

2662

如何設(shè)計一個用于數(shù)字圖像加密的序列密碼算法

0

0基于SRAM的可重配置電路PLD

675

675

基于偽隨機(jī)序列的噪音干擾FPGA實(shí)現(xiàn)

2102

2102如何使用FPGA實(shí)現(xiàn)偽隨機(jī)數(shù)發(fā)生器

24

24STM32F103C8T6讀取加密芯片SMEC98SP(SE98)隨機(jī)數(shù)范例程序源碼

10

10KUKA一套程序的建立(序列)

1082

1082 電子發(fā)燒友App

電子發(fā)燒友App

評論