集成運算放大電路

集成運算放大電

2009-12-14 11:48:12 2932

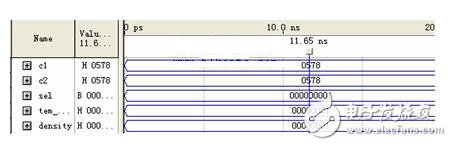

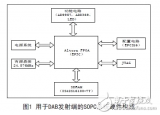

2932 基于FPGA 芯片EP3C16Q240C8N 的片上可編程系統(tǒng),該系統(tǒng)可用于實現(xiàn)IFFT運算和接口模塊,利用可嵌入到此FPGA 芯片的NiosII 軟核處理器來實現(xiàn)數(shù)據(jù)傳輸和控制。

2015-02-03 15:08:23 1185

1185

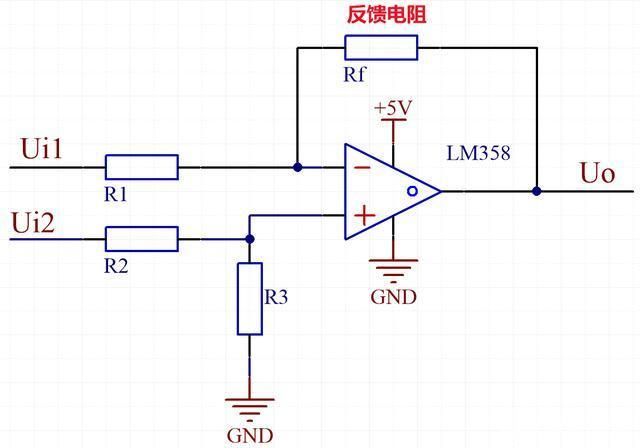

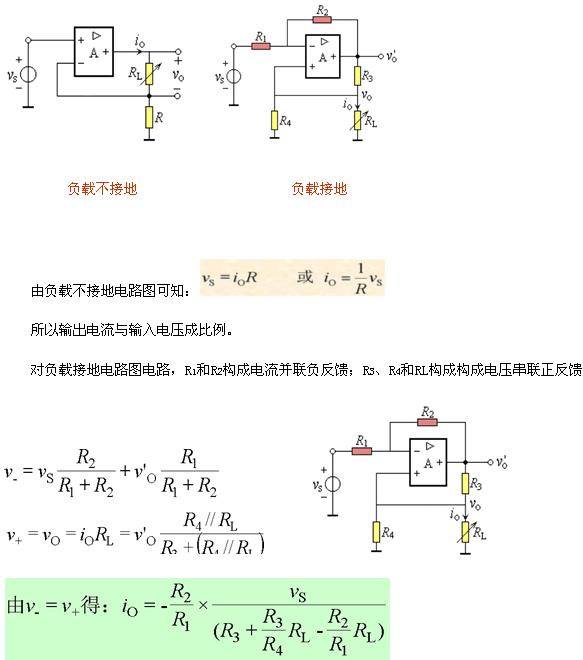

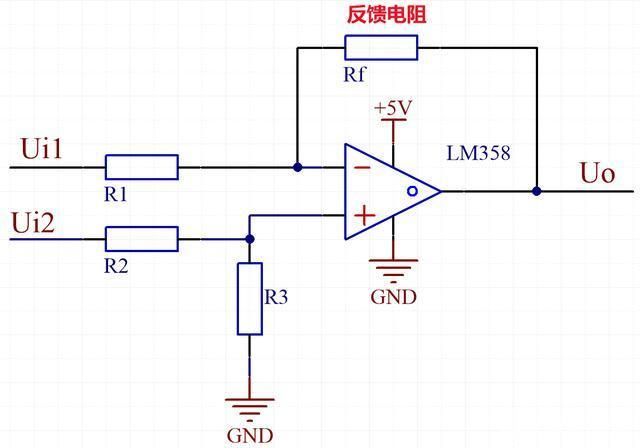

由于集成運放開環(huán)增益很高,所以構(gòu)成的基本運算電路均為深度負反饋電路,運算兩輸入端之間滿足“虛短”和“虛斷”,根據(jù)這二個特性可以很容易分析各種運算電路。

2022-09-05 16:05:13 4802

4802

基本運算電路分享

2023-02-03 16:02:28 651

651

FPGA 如何進行浮點運算

2015-09-26 09:31:37

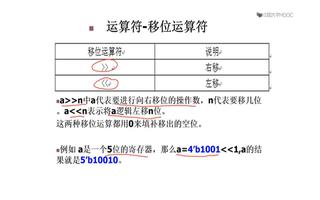

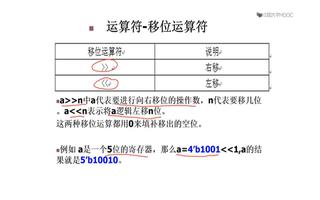

FPGA中的硬件邏輯與軟件程序的區(qū)別,相信大家在做除法運算時會有深入體會。若其中一個操作數(shù)為常數(shù),可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結(jié)構(gòu)復(fù)雜,且

2018-08-13 09:27:32

`FPGA基礎(chǔ)學(xué)習(xí)筆記--組合邏輯電路-算術(shù)運算電路+、-、*、/、%電路(1)加法電路:每1位大約消耗1個LE,示例代碼如下module arithmetic (input [7:0] iA

2012-02-23 16:45:35

設(shè)計的基礎(chǔ)知識,掌握FPGA最小系統(tǒng)硬件電路設(shè)計方法,學(xué)會操作QuartusII軟件來完成FPGA的設(shè)計和開發(fā)。1.1 可1.編程邏輯器件簡介2.可編程邏輯器件的發(fā)展歷史3. FPGA/CPLD的基本結(jié)構(gòu)

2014-04-23 15:28:29

=-*/在fpga中占用資源太大,怎么通過位運算實現(xiàn)這些,謝謝

2013-07-14 20:36:48

運算放大電路的設(shè)計實驗一 實驗?zāi)康?.加深對集成運放基本特性的理解。2.學(xué)習(xí)集成運放在基本運算電路中的設(shè)計、應(yīng)用及測試。二、實驗原理與設(shè)計方法集成運放是高增益

2008-09-22 13:09:28

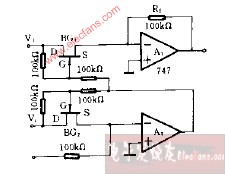

如圖所示運算放大電路,SW1為IO口控制信號,VREF電源電壓為2.495V,請問FB1處電壓范圍為多少,如何計算的?麻煩各位大神了

2022-03-09 12:00:58

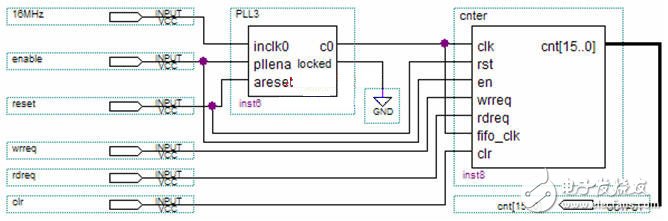

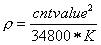

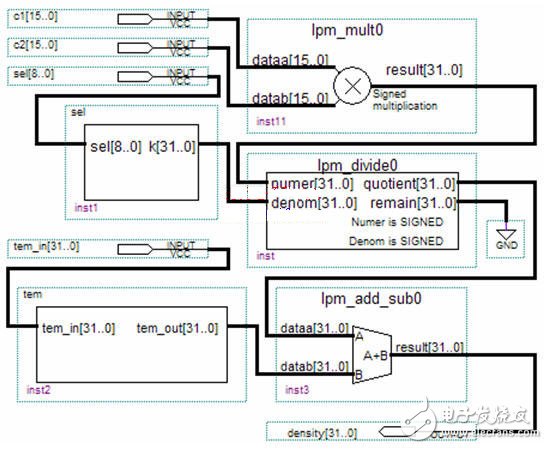

DSP:TMS320F28335FPGA:EP3C16Q240C8NFPGA同時采集16路模擬信號這里采集信號發(fā)生器的正弦信號 采集完傳輸至DSP進行處理DSP將運算玩的數(shù)據(jù)傳輸給FPGA 控制DA

2016-08-03 16:49:30

至FPGA 在傳至DSp進行運算。DSP也可根據(jù)運算做PWM輸出這就是個閉環(huán) 電機控制系統(tǒng),很靈活交流qq:***加我的時候請注明

2016-07-18 16:59:22

處理系統(tǒng)中最重要的部件之一。FPGA是當前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號

2019-07-05 06:21:42

的提升。運算速度或者數(shù)據(jù)路徑寬度都可以進一步提高,另外,時序操作可以在結(jié)構(gòu)上增加一些并行度。這些措施中,每一種都可以提高一定的性能。在利用了目標FPGA器件靈活性的結(jié)構(gòu)中實現(xiàn)算法,會獲得比較大的好處

2021-12-15 06:30:00

設(shè)計卷積運算模塊來加速卷積運算是 FPGA 加速電路的關(guān)鍵,卷積運算模塊由 3×3 逐 通道卷積運算模塊和 1×1 逐點卷積運算模塊組成。

首先為了讓設(shè)計的 3×3 逐通道卷積運算模塊能夠在不同的卷積層間

2023-06-20 19:45:12

,imshow(img_g);title('gradient2');圖7 梯度0 圖8 梯度1 圖9 梯度23 FPGA實現(xiàn)圖10 為整個設(shè)計的RTL級電路圖形態(tài)學(xué)開運算

2018-08-10 09:12:22

基于FPGA永磁無刷直流電機控制電路FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物

2016-02-01 14:44:30

本帖最后由 kandy286 于 2013-11-8 00:33 編輯

剛學(xué)FPGA,用FPGA+DAC設(shè)計的DDS,已實現(xiàn)調(diào)頻,調(diào)相功能。可是調(diào)幅該怎么控制呢?有種方案是改變DAC的參考電壓

2013-11-08 00:32:04

)和1路12位(包括實部和虛部)的數(shù)字信號送往SRAM中,再由控制模塊把SRAM所存的數(shù)據(jù)按照一定的邏輯送給互相關(guān)運算模塊(對FPGA編程實現(xiàn))做互相關(guān)運算。互相關(guān)運算模塊把每一時刻t0的所有互相關(guān)值,按

2009-09-19 09:25:42

本帖最后由 松山歸人 于 2021-6-28 09:57 編輯

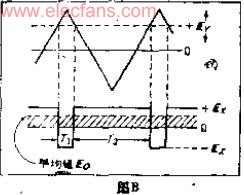

作者:郭嘉老師(張飛實戰(zhàn)電子高級工程師)積分運算和微分運算互為逆運算。在自控系統(tǒng)中,常用積分電路和微分電路作為調(diào)節(jié)環(huán)節(jié);此外

2021-06-28 09:56:07

控制方案,適用于高、中、低端電機控制;DSP數(shù)據(jù)處理能力較強、運算速度快,一般適用于高端復(fù)雜的電機系統(tǒng),但是依賴于軟件算法的成熟性和穩(wěn)定性;FPGA通過集成邏輯電路及專用電機驅(qū)動,能夠很好地適用于定制化

2014-05-21 16:08:35

FPGA如何實現(xiàn)32位減法運算

2019-02-28 04:59:09

定點數(shù)具有哪幾種表示的形式?FPGA是如何實現(xiàn)數(shù)字信號處理定點運算的?

2021-06-18 09:19:18

請問怎樣去實現(xiàn)一種基于FPGA的矩陣運算?

2021-06-22 07:00:19

自動白平衡的FPGA實現(xiàn)采用FPGA對自動白平衡進行運算有什么優(yōu)點?

2021-04-13 06:20:46

本文是在基于ARM+FPGA 的硬件平臺上進行嵌入式運動控制系統(tǒng)的設(shè)計,ARM實現(xiàn)應(yīng)用管理,FPGA 實現(xiàn)插補運算,發(fā)出脈沖到伺服驅(qū)動系統(tǒng),形成運動指令控制伺服電機運 轉(zhuǎn)等。文

2009-06-01 15:09:27 27

27 本文采用ALTERA 公司FPGA 作為算法處理器件,實現(xiàn)了互相關(guān)算法,取得了很好的效果。本文根據(jù)相關(guān)算法的運算原理并考慮了模塊與外部的交互性,在FPGA 中配置設(shè)計了互相關(guān)運算模塊

2009-09-01 09:48:25 13

13 根據(jù)傳統(tǒng)圓網(wǎng)印花機的結(jié)構(gòu)以及存在的問題。提出了基于ARNi和FPGA的嵌入式圓網(wǎng)印花機控制器的設(shè)計方案。并開發(fā)了試驗樣機系統(tǒng)。充分利用了ARM 微處理器高速運算能力和FPGA的快速

2009-11-30 15:12:39 18

18 本文采用ALTERA公司FPGA作為算法處理器件,實現(xiàn)了互相關(guān)算法,取得了很好的效果。本文根據(jù)相關(guān)算法的運算原理并考慮了模塊與外部的交互性,在FPGA中配置設(shè)計了互相關(guān)運算模塊、并串

2010-07-21 09:35:40 19

19 高精度的乘除法和開方等數(shù)學(xué)運算在FPGA實現(xiàn)中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應(yīng)用中,以處理時間換取資源的串行運算方法具有廣泛的應(yīng)

2010-07-28 18:05:14 37

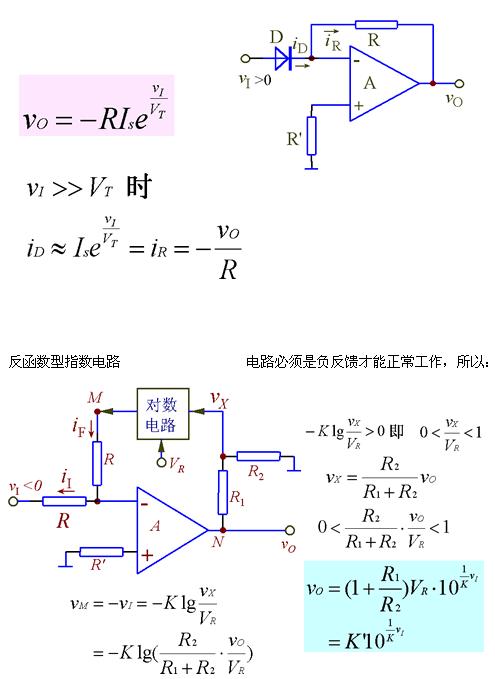

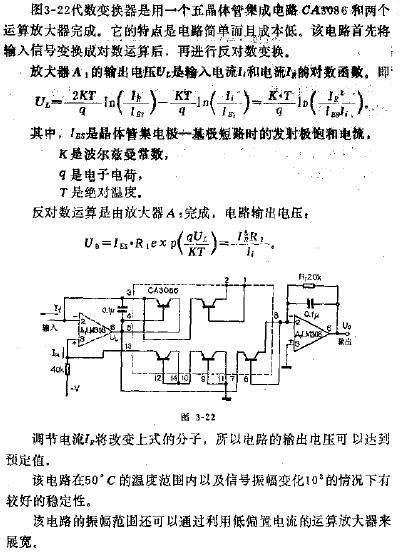

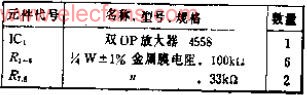

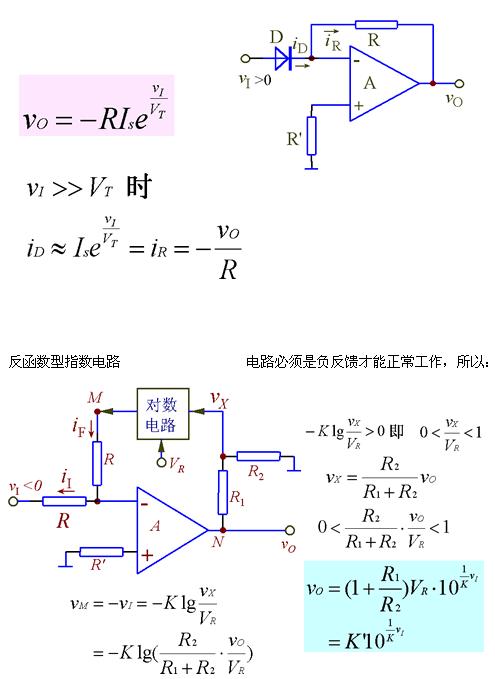

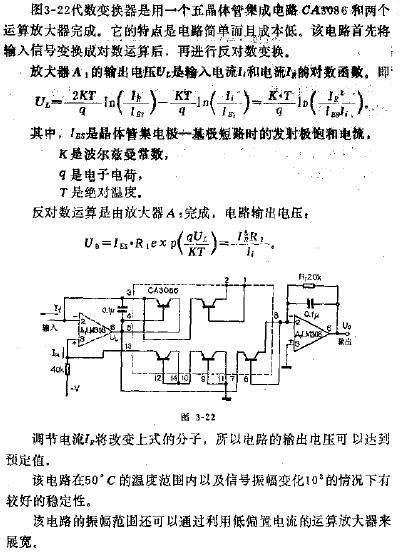

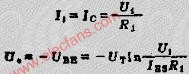

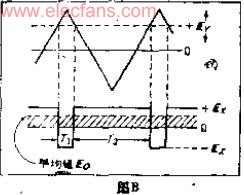

37 對數(shù)和指數(shù)運算電路:

對數(shù)運算電路

對數(shù)電路改進

2008-01-17 12:44:52 16483

16483

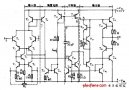

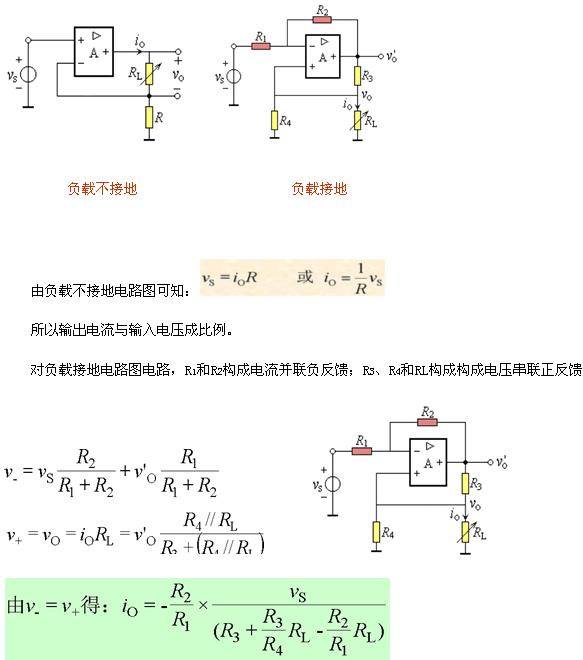

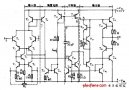

乘除運算電路

基本乘除運算電路,乘法電路

乘法器符號

2008-01-17 12:54:12 2705

2705

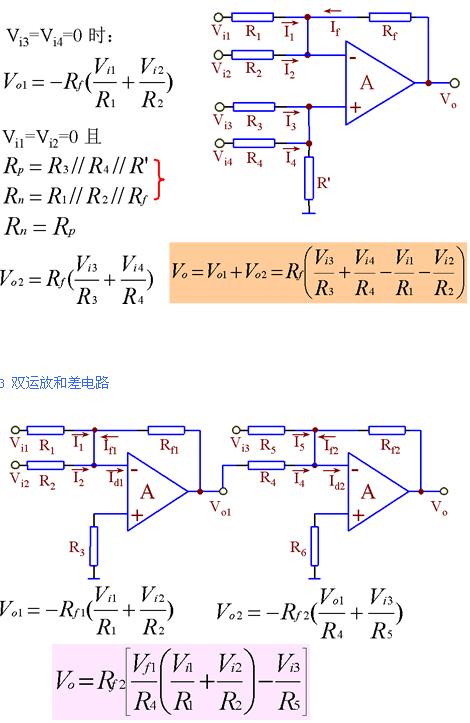

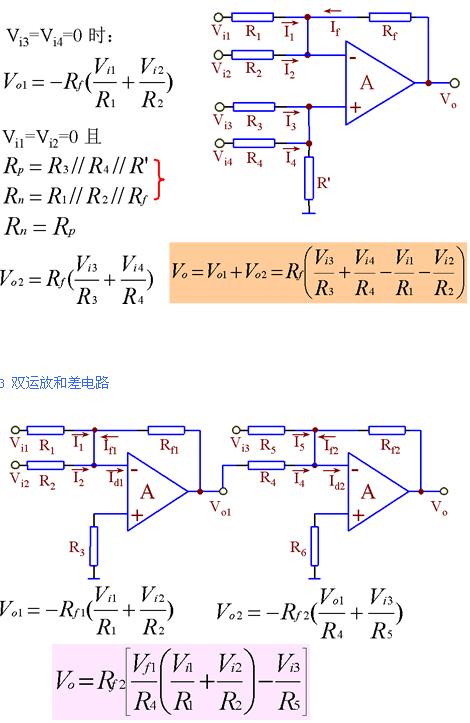

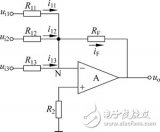

加減運算電路

求和電路

1. 反相求和電路

虛短、虛斷

2008-01-18 09:34:40 9699

9699

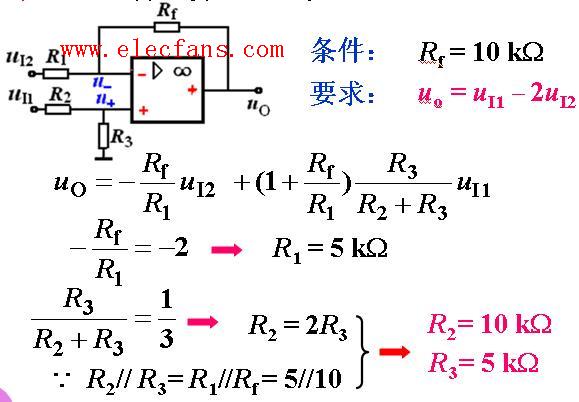

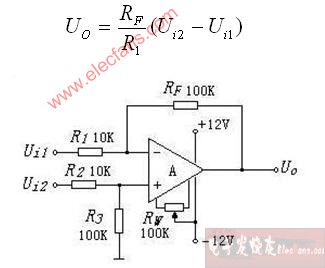

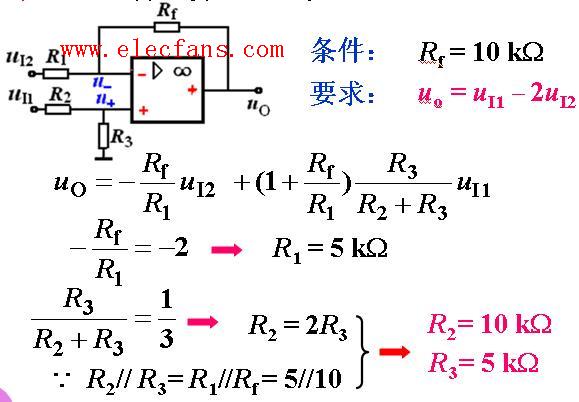

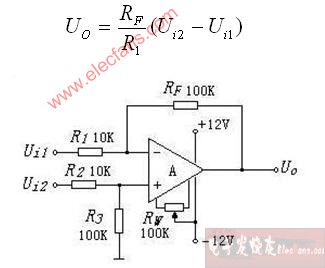

差分運算電路的設(shè)計

2008-08-04 15:11:37 1487

1487

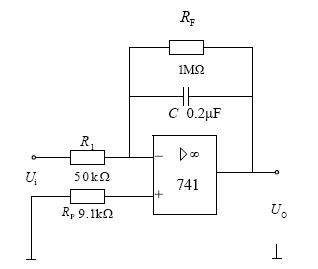

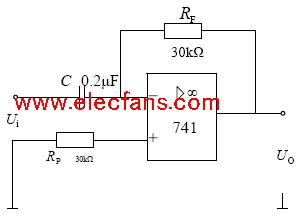

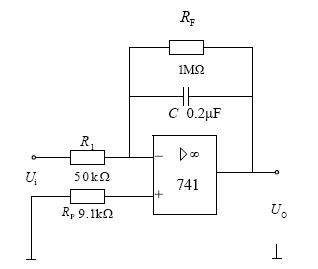

反相積分運算電路

反相積分器電路(圖3.8a.5)的輸出電壓與輸入電壓成積分關(guān)系,由運算放大器構(gòu)成的積分器電路的基本運算關(guān)系是

2008-09-22 11:50:10 33443

33443

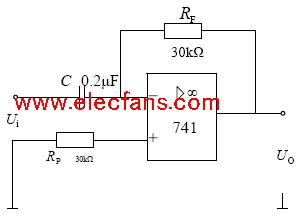

反相微分運算電路

微分是積分的逆運算。將積分運算電路中R1和C的位置互換,可組成基本微分運算電路(圖3.8a.6)。由

2008-09-22 12:17:47 2810

2810

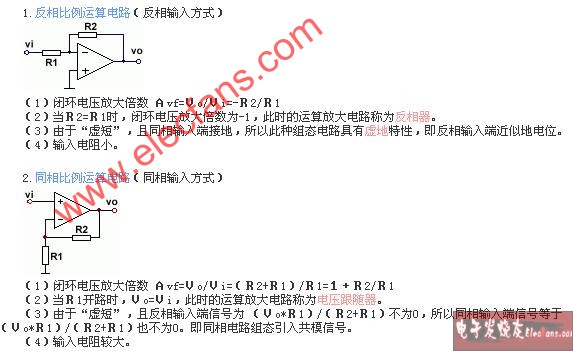

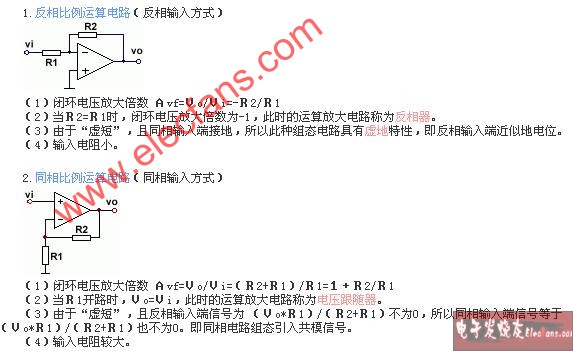

比例運算電路:有同相比例運算電路和反相比例運算電路

2009-02-11 09:28:11 988

988

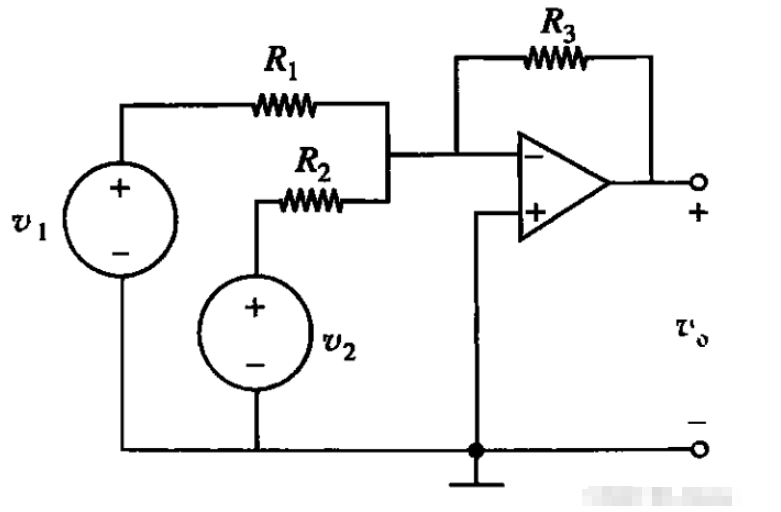

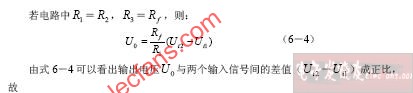

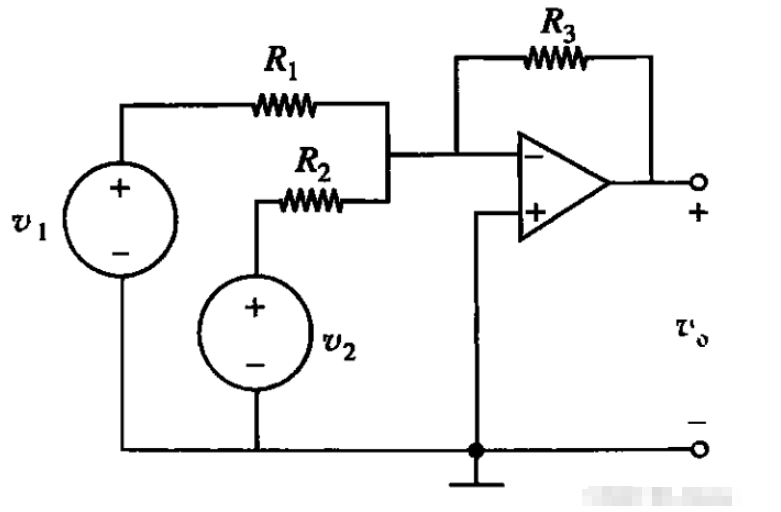

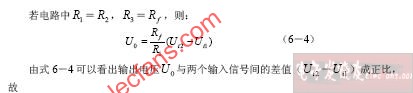

減法運算電路

圖6-4 減法運算電路

2009-03-09 10:11:43 5254

5254

差分比例運算電路(加減運算電路) 差分比例運算電路是加減運算電路的構(gòu)成特

2009-03-15 17:06:33 56194

56194

經(jīng)濟的代數(shù)運算電路

2009-04-09 10:19:27 516

516

指數(shù)運算電路

2009-04-09 10:35:32 740

740

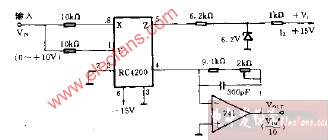

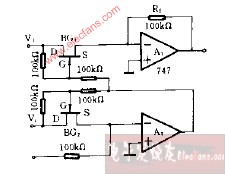

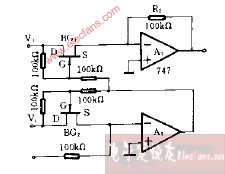

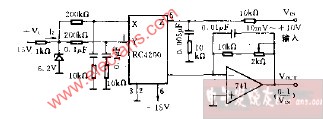

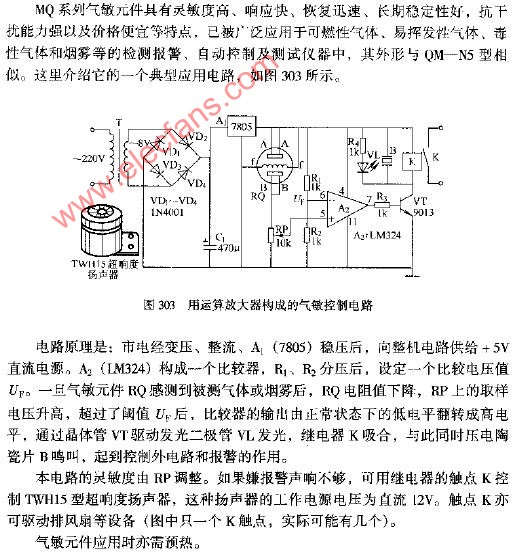

用運算放大器構(gòu)成的氣敏控制電路圖

2009-06-08 09:50:00 828

828

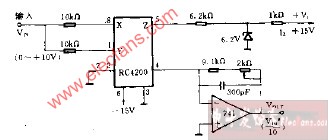

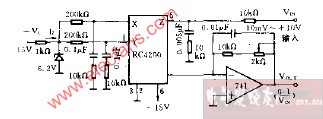

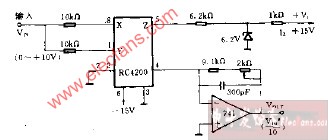

乘除運算電路圖

2009-07-17 11:26:22 445

445

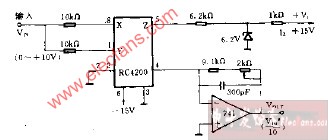

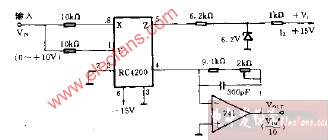

除法運算電路圖

2009-07-17 11:26:48 4079

4079

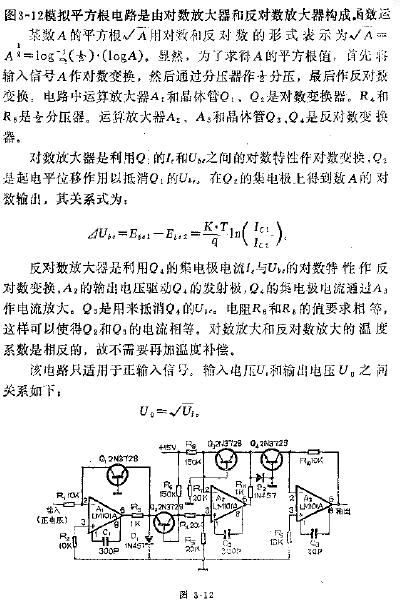

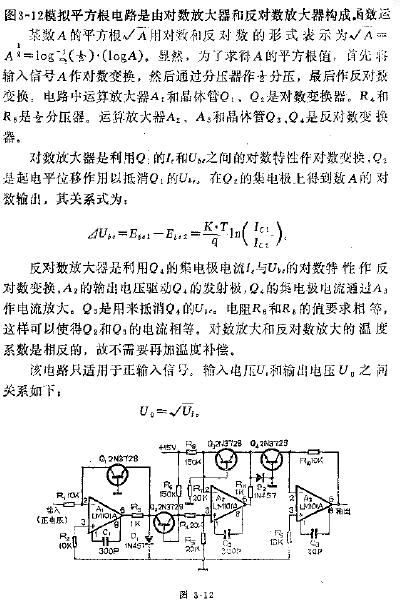

平方運算電路圖

2009-07-17 11:32:41 3169

3169

乘除運算電路圖

2009-07-20 12:09:43 531

531

除法運算電路圖

2009-07-20 12:10:07 734

734

平方運算電路圖

2009-07-20 12:16:02 3794

3794

平方運算電路圖

2009-07-20 12:18:34 2763

2763

用運算放大器構(gòu)成的氣敏控制電路圖

2010-04-02 18:12:27 540

540

基本對數(shù)運算電路

基本對數(shù)運算電路如圖5.4-14所示。

它具有反相結(jié)構(gòu),

2010-04-23 17:25:47 2430

2430

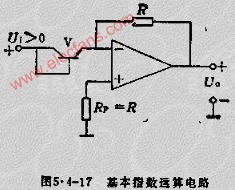

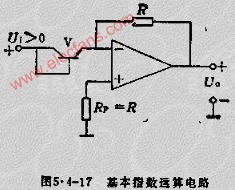

基本指數(shù)運算電路

將對數(shù)運算的三極管與反饋電阻位置互換一下,可得反對數(shù)運算電路,如圖5.4-17所示。

2010-04-24 15:51:37 1433

1433

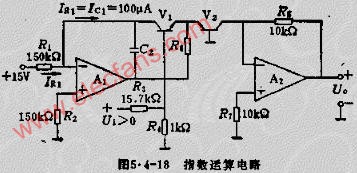

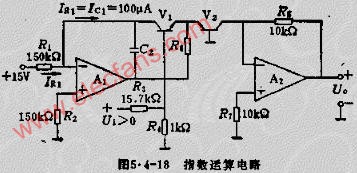

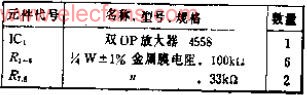

指數(shù)運算電路

圖5.4-18示出的是一個廣泛用的指數(shù)電路,圖中A2和V2組成基本指數(shù)運算電路,V2與V1是特性一致結(jié)溫相同的對管,是溫度補償元件。由于輔助放大

2010-04-24 15:55:06 5436

5436

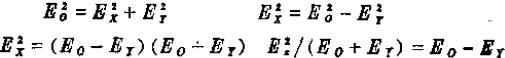

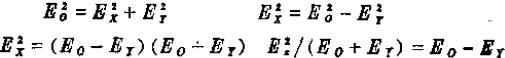

除法器對數(shù)運算電路的應(yīng)用

由對數(shù)電路實現(xiàn)除法運算的數(shù)學(xué)原理是:

2010-04-24 16:07:27 2520

2520

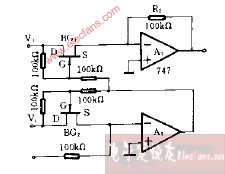

由輸入端選擇運算方式的加、減法運算電路

電路的功能

這是一種配

2010-05-08 11:32:23 1518

1518

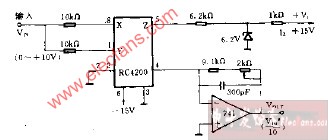

電路簡單的PWM乘法運算電路

電路的功能

脈沖寬度調(diào)制的乘法運算器

2010-05-08 14:23:16 3167

3167

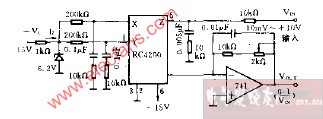

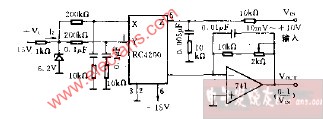

使用多功能運算IC的向量運算電路

電路的功能

若要在模擬電路中實

2010-05-10 12:01:22 1689

1689

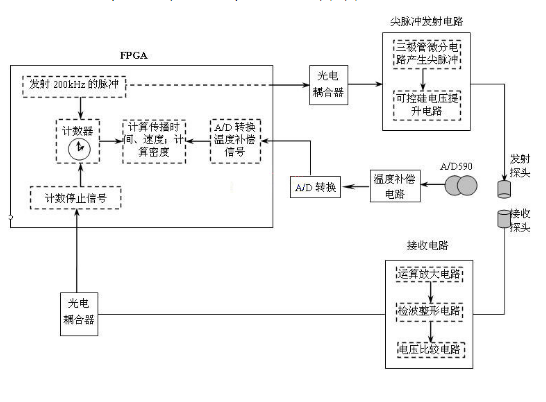

傳統(tǒng)的距離門控電路多采用分立元器件,工作頻率和控制精度均十分有限,難于滿足重復(fù)頻率高的測距需求.通過分析高重復(fù)率距離門控的時序,提出并實現(xiàn)了一種基于FPGA的高重復(fù)率距離門控電路方法.該方法充分發(fā)揮了FPGA在運算、存儲、時鐘管理等方面的優(yōu)勢:采

2011-03-15 15:05:00 24

24 介紹一種基于FPGA(Field Programmable Gate Array)現(xiàn)場可編程門陣列的可鍵盤控制的計數(shù),顯示電路的實現(xiàn)方法。應(yīng)用VHDL語言(高速集成電路硬件描述語言)完成了34矩陣開關(guān)的掃描電路,可

2011-05-03 18:02:14 97

97 通用運算放大電路

2011-05-07 10:00:42 1928

1928

針對復(fù)雜算法中矩陣運算量大, 計算復(fù)雜, 耗時多, 制約算法在線計算性能的問題, 從硬件實現(xiàn)角度, 研究基于FPGA/Nios-Ⅱ的矩陣運算硬件加速器設(shè)計, 實現(xiàn)矩陣并行計算。首先根據(jù)矩陣運算

2011-12-06 17:30:41 89

89 提出一種基2FFT的FPGA方法,完成了基于FPGA高精度浮點運算器的FFT的設(shè)計。利用VHDL語言描述了蝶形運算過程及地址產(chǎn)生單元,其仿真波形基本能正確的表示輸出結(jié)果。

2011-12-23 14:24:08 46

46 設(shè)計了一種基于DSP與FPGA的運動控制器。該控制器以DSP為控制核心,用FPGA構(gòu)建運動控制器與傳感器以及電機驅(qū)動器的接口電路。充分發(fā)揮了DSP強大的運算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93 介紹了一種基于FPGA的多軸控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外圍電路組成,用于同時控制多路電機的運動。利用Verilog HDL 硬件描述語言在FPGA中實現(xiàn)了電機控制邏

2013-04-27 16:23:11 82

82 基于FPGA的開方運算實現(xiàn) ,的技術(shù)論文

2015-10-30 10:59:01 5

5 基于FPGA的LED屏控制器設(shè)計基于FPGA的LED屏控制器設(shè)計

2016-06-21 17:56:39 50

50 信號運算電路

2016-12-11 23:29:39 0

0 集成運算放大電路

2016-12-15 15:27:05 0

0 比例求和運算電路

2016-12-15 15:27:05 0

0 比例運算電路的輸出電壓與輸入電壓之間存在比例關(guān)系,即電路可實現(xiàn)比例運算。比例電路是最基本的運算電路,是其他各種運算電路的基礎(chǔ),本章隨后將要介紹的求和電路、積分和微分電路、對數(shù)和指數(shù)電路等等,都是在比例電路的基礎(chǔ)上,加以擴展或演變以后得到的。

2017-05-14 09:18:23 78105

78105

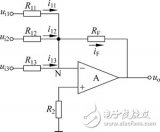

加法運算電路能實現(xiàn)多個模擬量的求和運算。圖1所示為一個3個輸入信號的反相加法運算電路。

2017-05-15 09:41:34 195021

195021

運算放大器16個基本運算電路運算放大器16個基本運算電路

2017-10-30 08:44:22 312

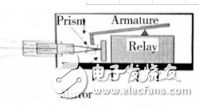

312 本文提出一種光開關(guān)模塊控制電路的FPGA設(shè)計方法。通過硬件設(shè)置通道,由FPGA 讀入通道信息后對其進行譯碼,并送到光開關(guān)的驅(qū)動電路。光開關(guān)通道切換成功標志信息由光開關(guān)反饋回的狀態(tài)信號與FPGA 所讀入的原始數(shù)據(jù)比較而得: 如果兩者相同,則通道切換正確,若兩者不同,則通道切換錯誤。

2017-11-18 12:15:29 3498

3498

運算電路是集成運算放大器的基本應(yīng)用電路,它是集成運放的線性應(yīng)用。討論的是模擬信號的加法、減法積分和微分、對數(shù)和反對數(shù)(指數(shù))、以及乘法和除法運算。

2017-11-27 15:55:10 0

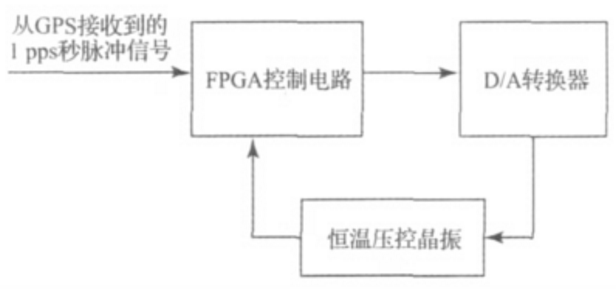

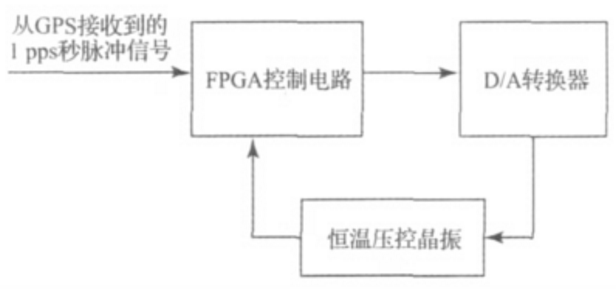

0 本文主要介紹了基于FPGA的壓控晶振同步頻率控制系統(tǒng)的研究與設(shè)計。利用GPS提供的1pps秒脈沖信號,為解決上述問題,在FPGA的基礎(chǔ)上利用干擾秒脈沖信號消除和偏差頻率平均運算等方法,減少外圍電路

2018-03-02 14:55:59 4473

4473

結(jié)構(gòu)復(fù)雜,采用DSP實現(xiàn)會增加系統(tǒng)負擔,降低系統(tǒng)速度。在某些對速度要求較高的情況,必須采用專門的浮點運算處理器。 EDA/FPGA技術(shù)不斷發(fā)展,其高速、應(yīng)用靈活、低成本的優(yōu)點使其廣泛應(yīng)用數(shù)字信號處理領(lǐng)域。在FPCA技術(shù)應(yīng)用的初期,

2018-04-10 14:25:53 17

17 FPGA中的硬件邏輯與軟件程序的區(qū)別,相信大家在做除法運算時會有深入體會。若其中一個操作數(shù)為常數(shù),可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結(jié)構(gòu)復(fù)雜

2018-05-18 01:15:00 4150

4150 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進階應(yīng)用。

2019-12-03 07:03:00 2868

2868

開方運算作為數(shù)字信號處理(DSP)領(lǐng)域內(nèi)的一種基本運算,其基于現(xiàn)場可編程門列(FPGA)的工程實現(xiàn)具有較高的難度。本文分析比較了實現(xiàn)開方運算的牛頓-萊福森算法,逐次逼近算法,非冗余開方算法3種算法

2020-08-06 17:58:15 6

6 有些FPGA中是不能直接對浮點數(shù)進行操作的,只能采用定點數(shù)進行數(shù)值運算。對于FPGA而言,參與數(shù)學(xué)運算的書就是16位的整型數(shù),但如果數(shù)學(xué)運算中出現(xiàn)小數(shù)怎么辦呢?要知道,FPGA對小數(shù)是無能為力

2021-08-12 09:53:39 4503

4503 FPGA中的硬件邏輯與軟件程序的區(qū)別,相信大家在做除法運算時會有深入體會。若其中一個操作數(shù)為常數(shù),可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結(jié)構(gòu)復(fù)雜,且通常無法在一個時鐘周期內(nèi)完成。因此FPGA實現(xiàn)除法運算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 6098

6098 給異步電動機供屯(電壓、頻率可調(diào))的主電路提供控制信號的回路,稱為控制電路。如下圖所示,控制電路由以下電路組成,順率、電壓的“運算電路”,主電路的“電壓/電流檢測電路”,電動機的“速度檢測電路”,將運算電路的控制信號進行放大的“驅(qū)動電路”,以及逆變器和電動機的“保護電路”。

2022-11-28 15:49:30 1597

1597 隨著 機器學(xué)習(xí) (Machine Learning)領(lǐng)域越來越多地使用現(xiàn)場可 編程 門陣列( FPGA )來進行推理(inference)加速,而傳統(tǒng)FPGA只支持定點運算的瓶頸越發(fā)凸顯

2023-03-11 13:05:07 351

351 由于FPGA可以對算法進行并行化,所以FPGA 非常適合在可編程邏輯中實現(xiàn)數(shù)學(xué)運算。

2023-05-15 11:29:15 2056

2056

本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關(guān)的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:17:12 888

888

本文是本系列的第四篇,本文主要介紹FPGA常用運算模塊-除法器,xilinx提供了相關(guān)的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:20:45 1840

1840

點擊上方 藍字 關(guān)注我們 一、前言 FPGA以擅長高速并行數(shù)據(jù)處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現(xiàn)今火爆的AI應(yīng)用,都離不開卷積、濾波、變換等基本的數(shù)學(xué)運算。但由于FPGA

2023-07-19 14:25:02 794

794

FPGA實現(xiàn)加法和減法運算非常簡單,實現(xiàn)乘法和除法可以用IP,那實現(xiàn)對數(shù)和指數(shù)運算該用什么呢?

2023-08-05 09:37:05 810

810

FPGA以擅長高速并行數(shù)據(jù)處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現(xiàn)今火爆的AI應(yīng)用,都離不開卷積、濾波、變換等基本的數(shù)學(xué)運算。但由于FPGA的硬件結(jié)構(gòu)和開發(fā)特性使得其對很多算法

2023-09-05 11:45:02 267

267 ,浮點加法器是現(xiàn)代信號處理系統(tǒng)中最重要的部件之一。FPGA是當前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。 但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號處理等方

2023-09-22 10:40:03 394

394

電子發(fā)燒友網(wǎng)站提供《基于FPGA的DMD驅(qū)動控制電路的研究設(shè)計.pdf》資料免費下載

2023-11-17 15:44:26 3

3

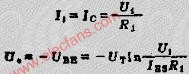

(1-1)

(1-1)

(2-1)

(2-1)

電子發(fā)燒友App

電子發(fā)燒友App

評論