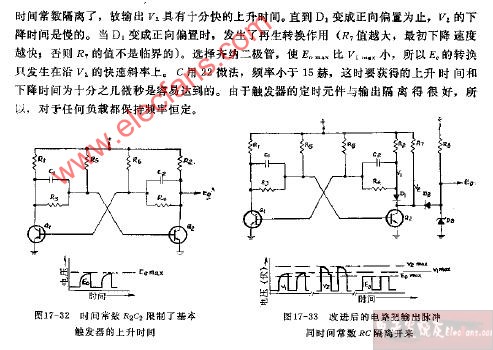

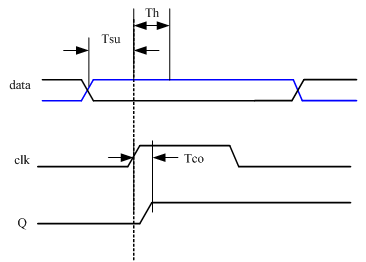

改進了上升時間和穩(wěn)定性是觸發(fā)器電路圖

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電子技術(shù)>電路圖>數(shù)字電路圖>改進了上升時間和穩(wěn)定性是觸發(fā)器電路圖

相關(guān)推薦

347

347 495

495 748

748

294

294

2572

2572 564

564

1874

1874 16964

16964

2453

2453 22623

22623

2073

2073

5729

5729

15895

15895 2809

2809

評論