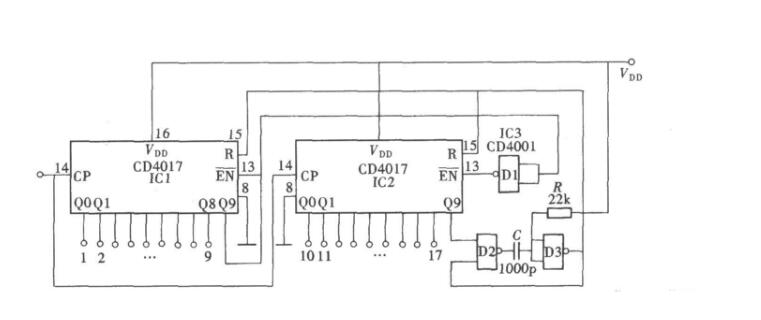

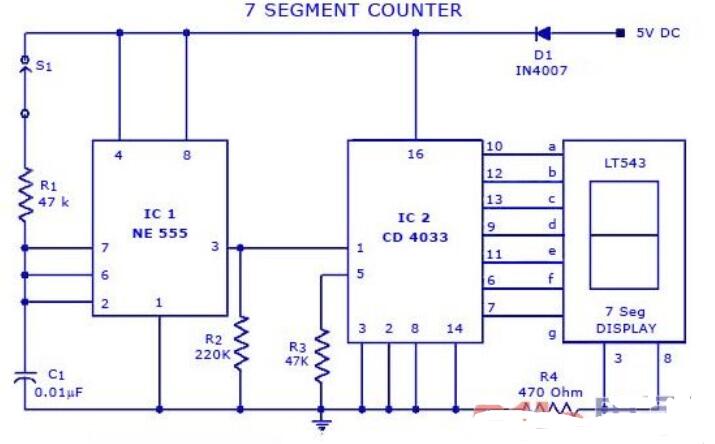

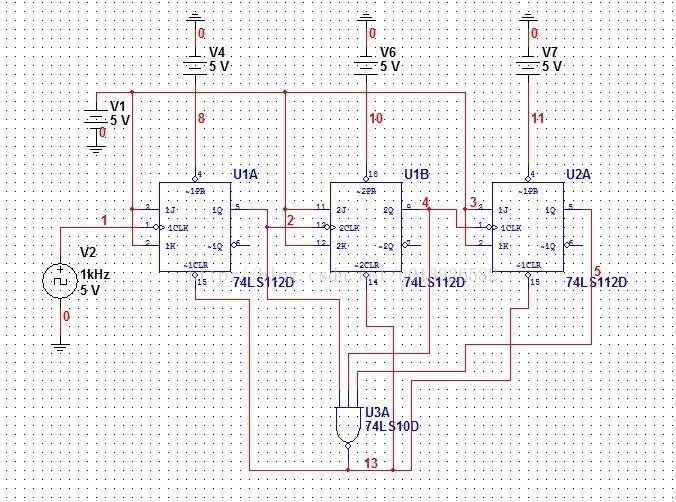

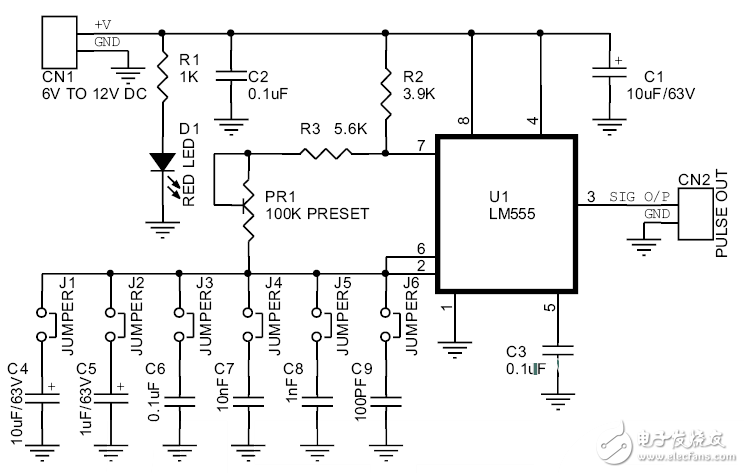

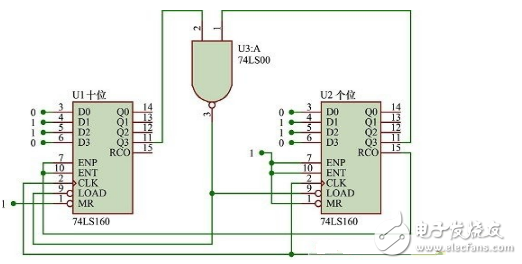

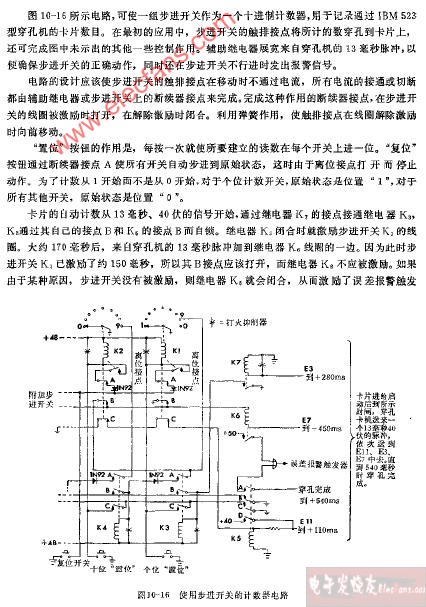

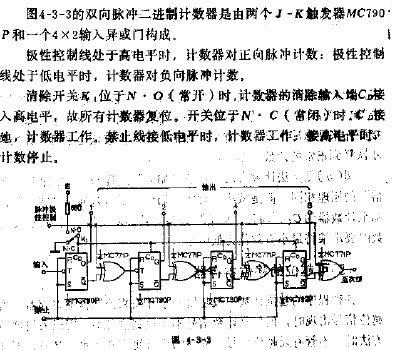

脈沖計數器電路圖設計(一)

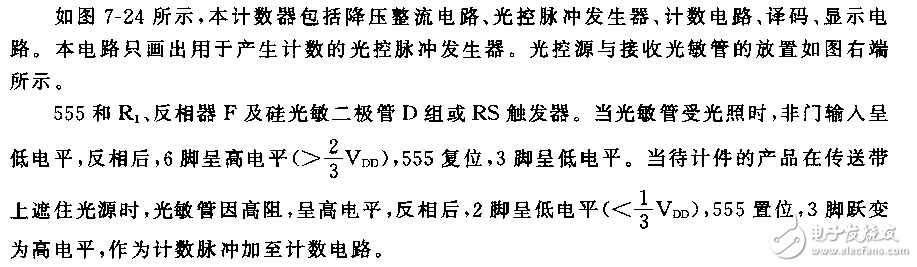

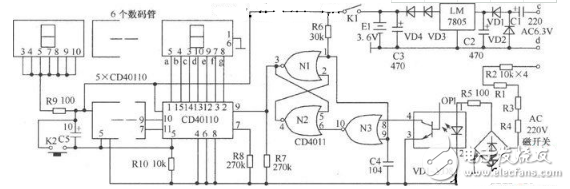

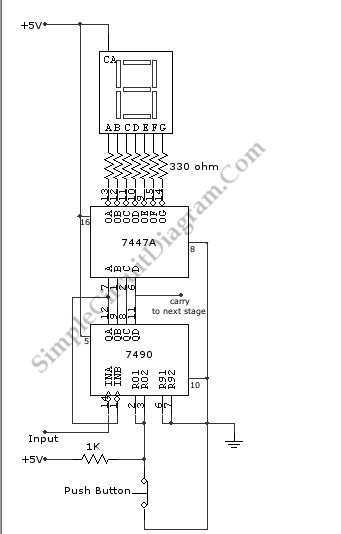

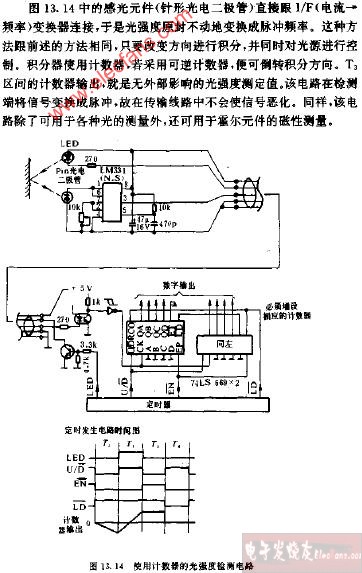

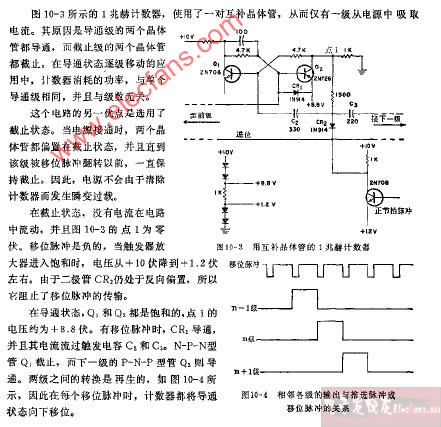

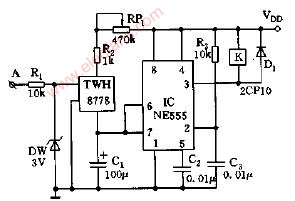

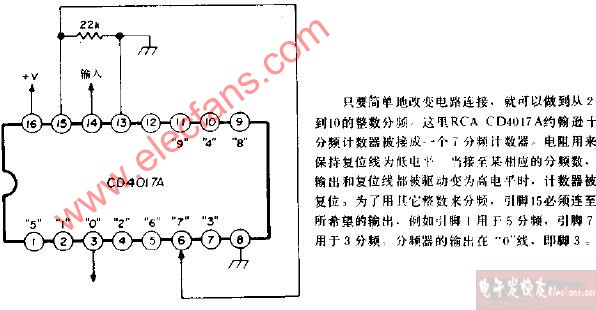

脈沖計數器電路圖,本計數器包括降整流電路,光控脈沖發生器,計數電路,譯碼,顯示電路。

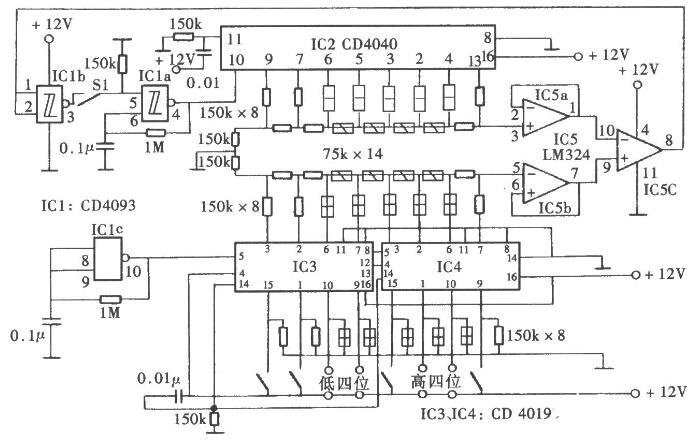

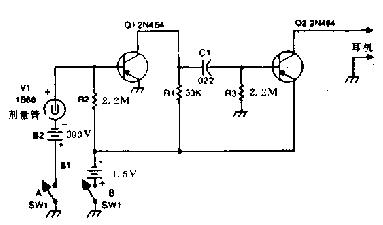

脈沖計數器電路圖設計(二)

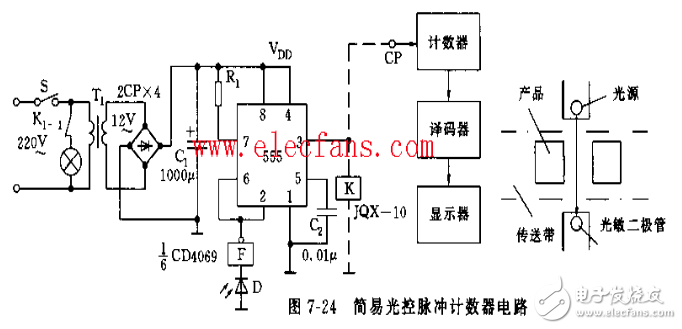

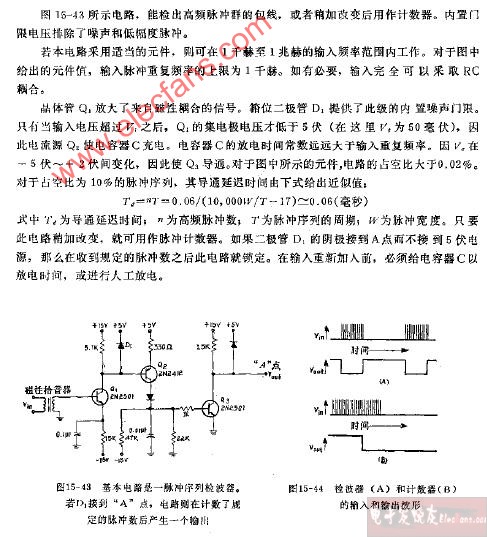

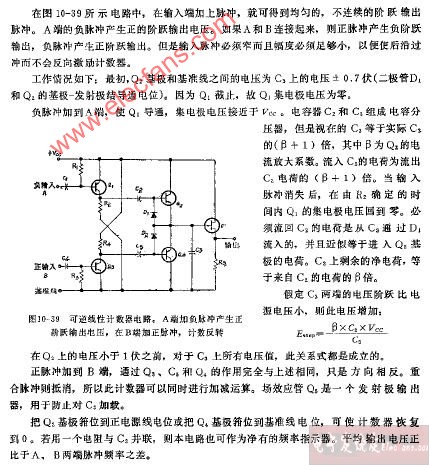

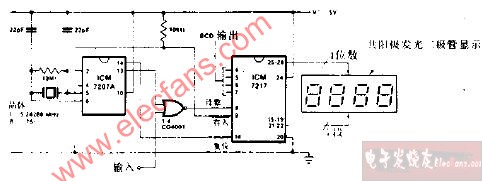

如圖所示,是計數器實例,它是對A端加的脈沖進行累積計數的電路,一般多用于輸入脈沖的計數。S1~S4為復位開關,用于計數數的設定。計數到設定的計數數時負載電路動作,相應的繼電器控制有關的電路動作。若在A端子施加圖5-12的時間脈沖,也可以構成以電源頻率為基準的數字定時電路。

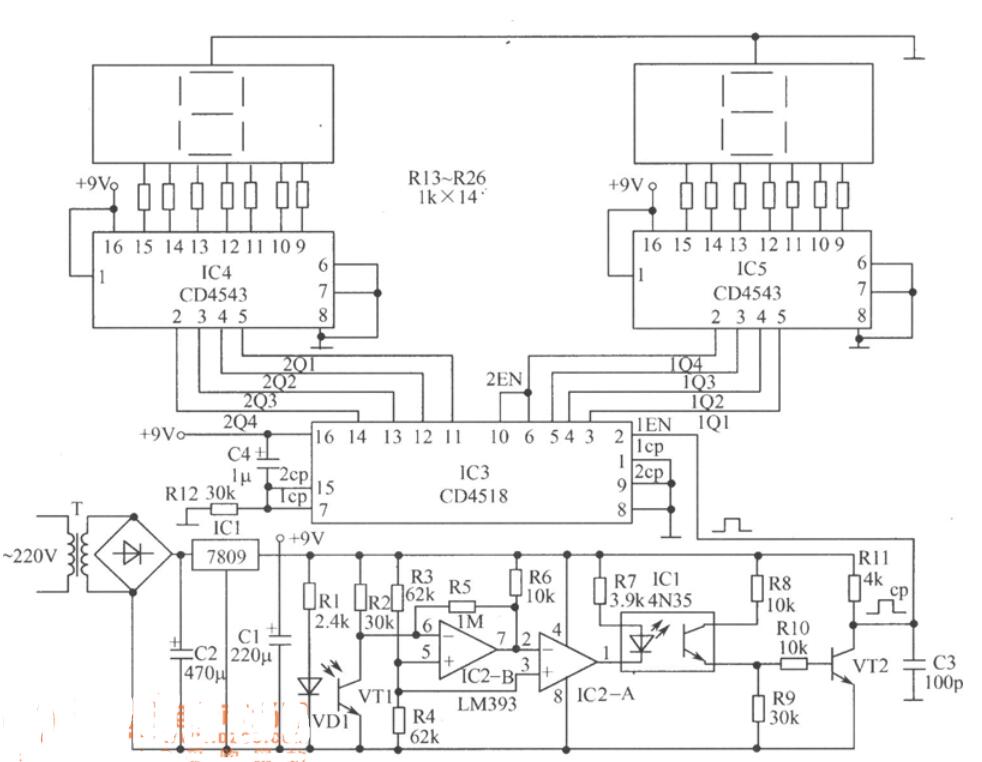

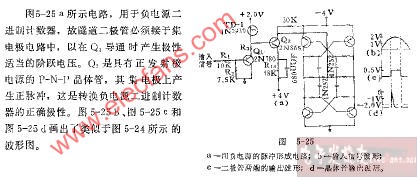

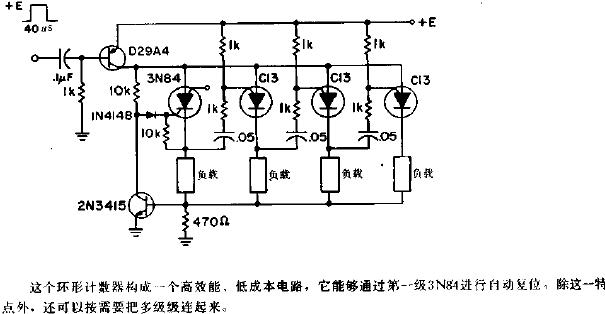

脈沖計數器電路圖設計(三)

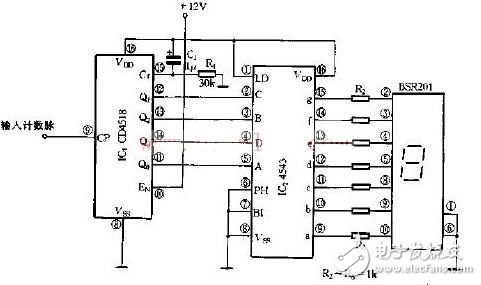

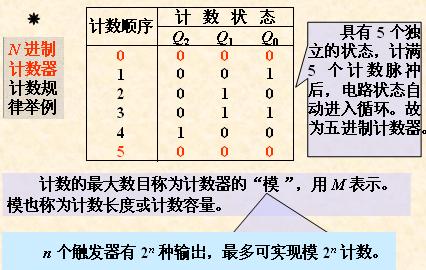

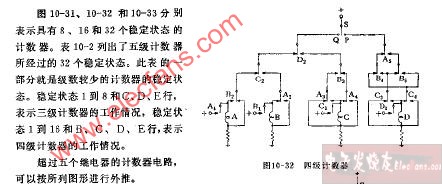

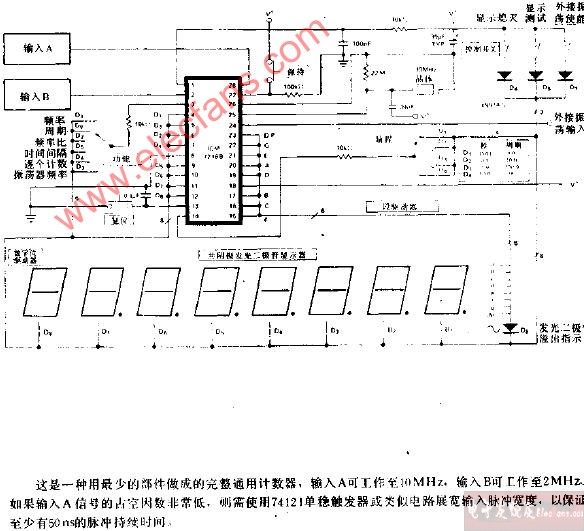

計數是一種最簡單基本的運算,計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。計數器在數字系統中應用廣泛,如在電子計算機的控制器中對指令地址進行計數,以便順序取出下一條指令,在運算器中作乘法、除法運算時記下加法、減法次數,又如在數字儀器中對脈沖的計數等等。計數器可以用來顯示產品的工作狀態,一般來說主要是用來表示產品已經完成了多少份的折頁配頁工作。它主要的指標在于計數器的位數,常見的有3位和4位的。

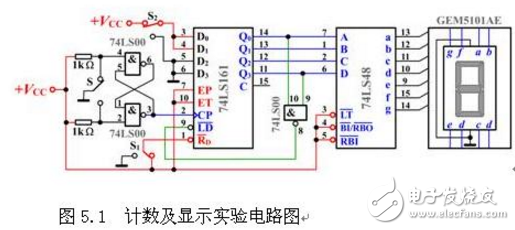

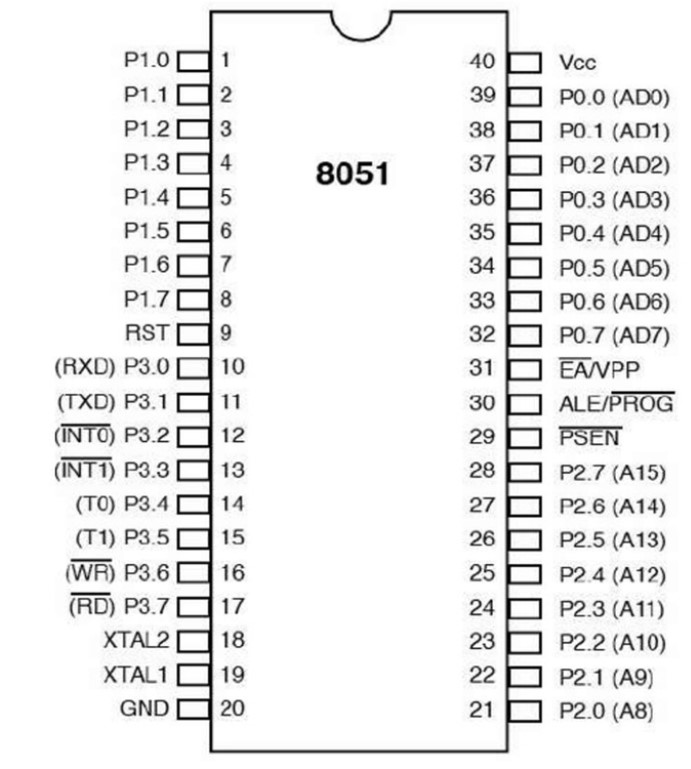

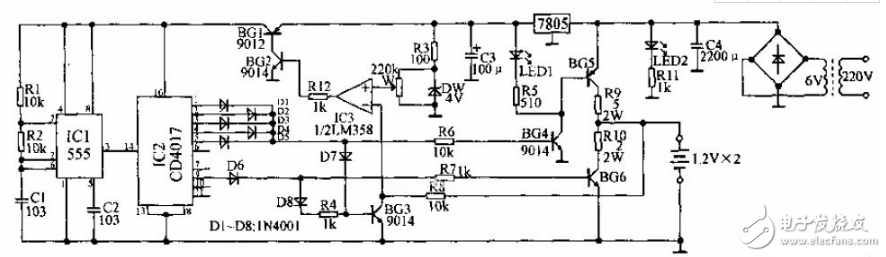

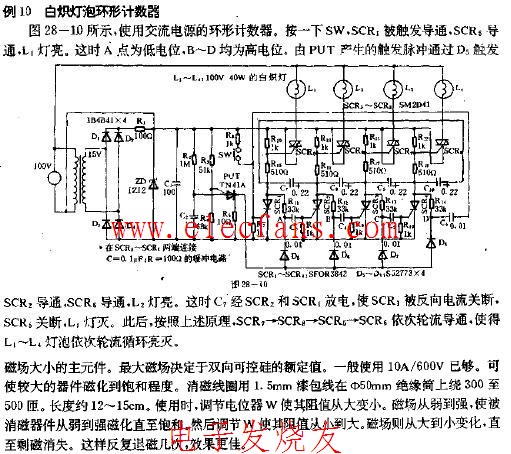

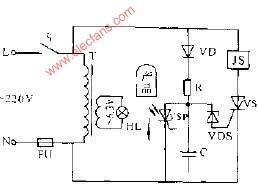

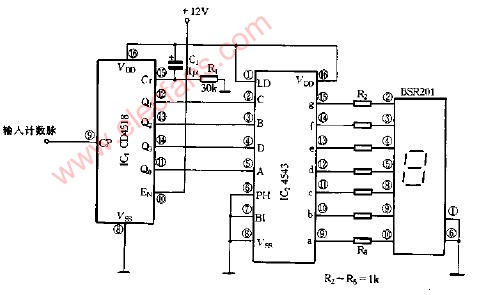

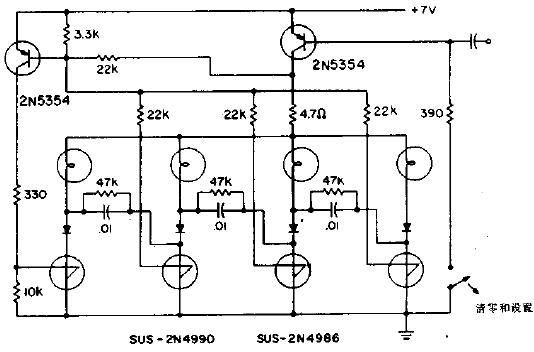

脈沖計數器電路圖設計(四)

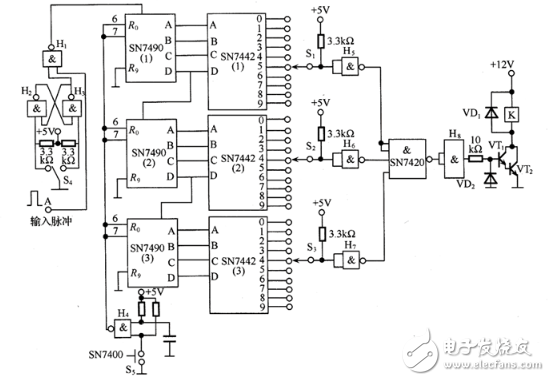

如圖所示電路,原機械計數器只有兩個磁開關信號端子,電子計數器則增加了c、d兩個AC6.3V輸入端子,共有4個接線端子。C1、C2、VD1、VD2組成倍壓整流、濾波電路,經7805穩壓后,輸出5V穩定直流電壓,經VD3、VD4降壓后,得到約3.6V的直流電壓,E1為小型3.6V鎳鎘充電電池,市電正常時,對其進行充電;市電斷電時,E1對負載進行供電,以保持斷電時的計數數值,VD3、VD4在這里起隔離作用。a、b兩端輸入磁開關閉合時接通交流220V電壓,此電壓經R1~R4降壓,并經VD5~VD8橋式整流后,得到約6V的直流脈動電壓,經R5限流后,加在光電耦合器的發光管上,使發光管點亮,光敏管受光照電阻下降,從而產生一個下降脈沖,經CD4011的N3反相后,加在N1、N2組成的觸發器上,由N1輸出計數脈沖,N1、N2、N3共同構成脈沖整形電路。CD40110是將計數器、鎖存器、譯碼器和筆段顯示驅動器制作在同一基片上的“四合一電路”芯片,其5腳置高電平時,計數器復位,因而,K2是清零開關。9腳為加計數輸入端,7腳為減計數輸入端。整形后的計數脈沖從9腳輸入,當第一片CD40110計至“9”時,若再輸入一個脈沖,則10腳輸出一個進位脈沖。依次類推,總共能計量“99999”印張(最左邊一個數碼管只顯示零,不起計數作用)。

元器件選擇:光耦合器OP1選擇TLP532,也可選擇TLP332、TLP632等型號。數字電路選擇CD4011型號。其他元器件如圖所標注。

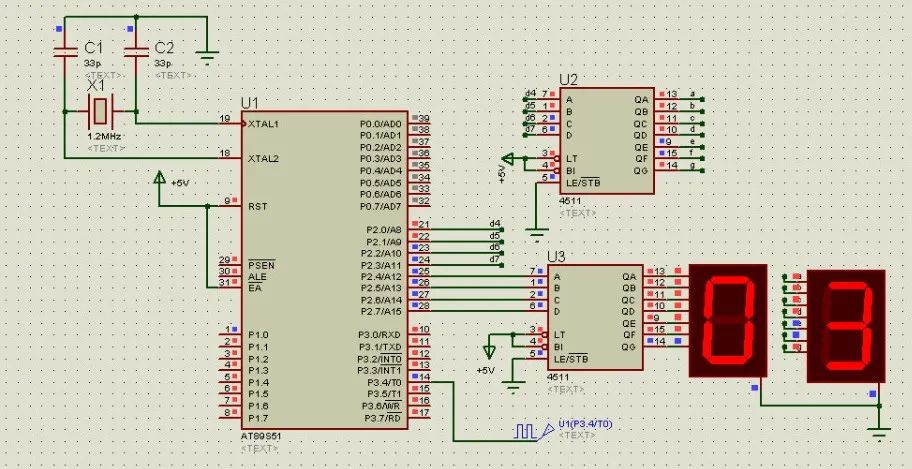

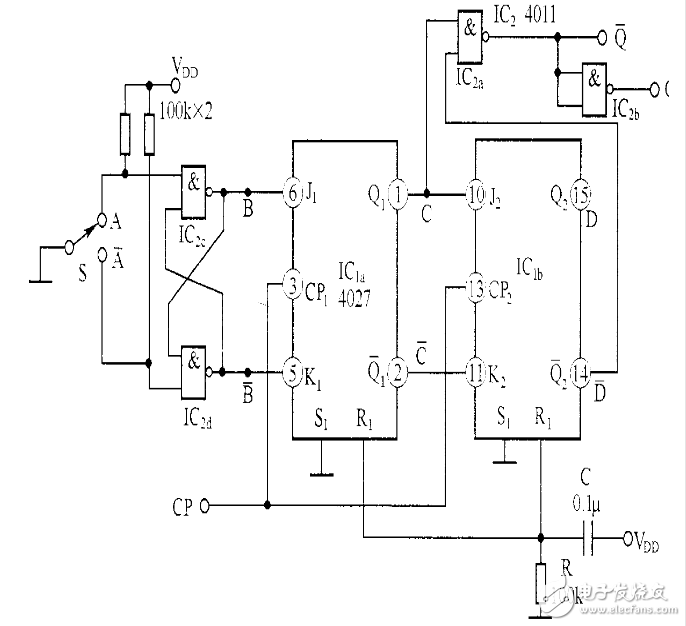

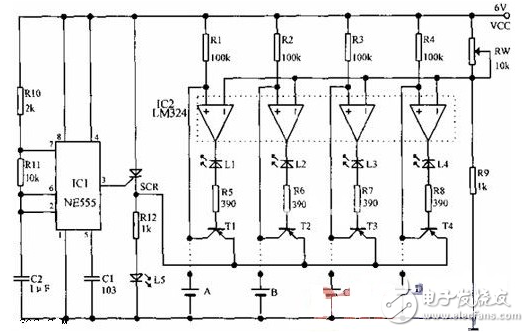

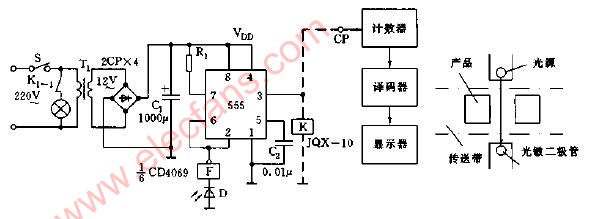

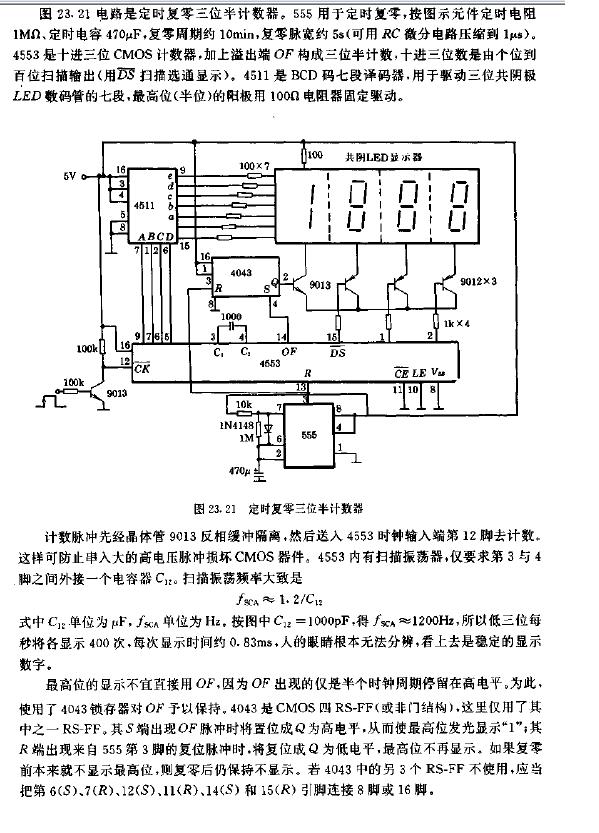

脈沖計數器電路圖設計(五)

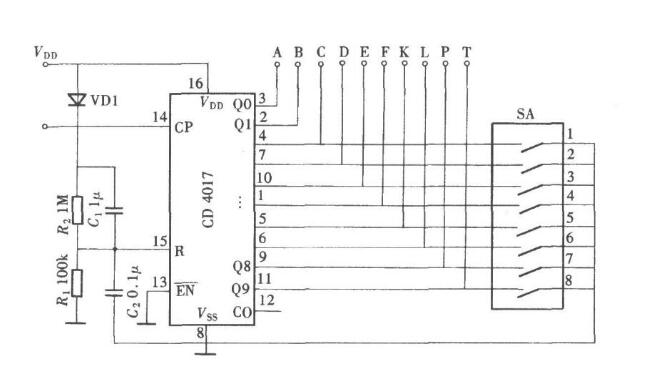

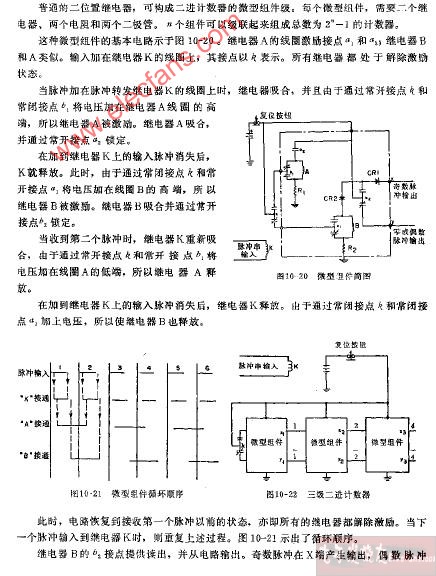

CD4017是5位Johnson計數器,具有10個譯碼輸出端,CP,CR,INH輸入端。時鐘輸入端的斯密特觸發器具有脈沖整形功能,對輸入時鐘脈沖上升和下降時間無限制。INH為低電平時,計算器在時鐘上升沿計數;反之,計數功能無效。CR為高電平時,計數器清零。Johnson計數器,提供了快速操作,2輸入譯碼選通和無毛刺譯碼輸出。防鎖選通,保證了正確的計數順序。譯碼輸出一般為低電平,只有在對應時鐘周期內保持高電平。在每10個時鐘輸入周期CO信號完成一次進位,并用作多級計數鏈的下級脈動時鐘。

CD4017邏輯結構圖

十進制計數/分頻器CD4017,其內部由計數器及譯碼器兩部分組成,由譯碼輸出實現對脈沖信號的分配,整個輸出時序就是O0、O1、O2、…、O9依次出現與時鐘同步的高電平,寬度等于時鐘周期。

CD4017有10個輸出端(O0~O9)和1個進位輸出端~O5-9。每輸入10個計數脈沖,~O5-9就可得到1個進位正脈沖,該進位輸出信號可作為下一級的時鐘信號。

CD4017有3個輸(MR、CP0和~CP1),MR為清零端,當在MR端上加高電平或正脈沖時其輸出O0為高電平,其余輸出端(O1~O9)均為低電平。CP0和~CPl是2個時鐘輸入端,若要用上升沿來計數,則信號由CP0端輸入;若要用下降沿來計數,則信號由~CPl端輸入。設置2個時鐘輸入端,級聯時比較方便,可驅動更多二極管發光。

由此可見,當CD4017有連續脈沖輸入時,其對應的輸出端依次變為高電平狀態,故可直接用作順序脈沖發生器。

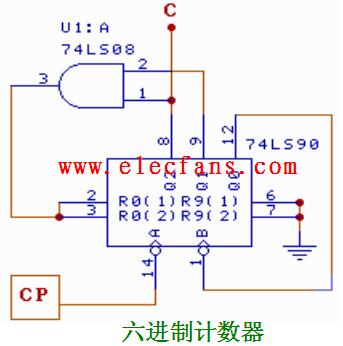

用CD4017和選擇開關組成多進制計數器

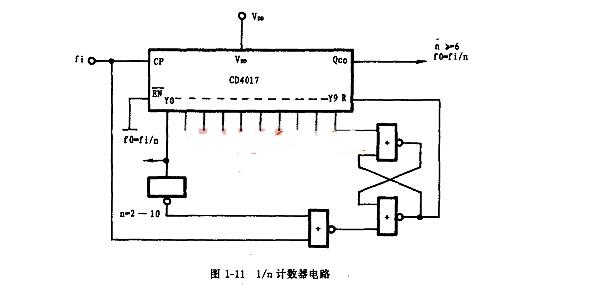

CD4017組成的1/n計數器電路圖

用CD40171C構成1/n計數器可以分為兩種情況:當n=10時,只需使用一塊CD4017IC,外接n個門電路即可構成1/n計數器如圖1-n所示。在時鐘脈沖的作用下,CD4017IC逐個。計數當到第Yn個譯碼輸出時,由外接或非門組成的R-S觸發器產生正脈沖輸出使CD40171C復零。如果n》=6時,則信號可由進位輸出端QCO輸出;如果n6時,則信號要由YO譯碼輸出端輸出因為n6時,q由端始終保持高電平(參見CD4017波形圖),不會產生脈中跳變。

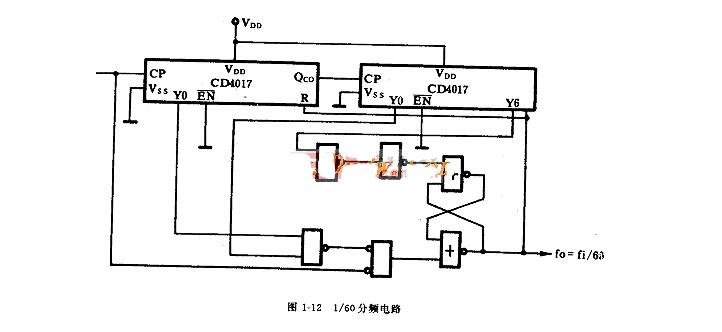

當分頻系數n》10時,應根據n的大小來確定CD4017的位數當n=60時的電路工作原理如圖1-12所示。輸入時鐘脈中當個位數的輸出YO為“1,十位數的輸出Y6為”1“時由外接門電路組成的R-S觸發器產生正脈沖輸出,從而使各級計數器全部清零。到輸入脈沖變為0電平時CD4017的YO輸出端又使R-S觸發器復位,于是又開始新的一輪計數如此循環往復即得到連續的60分頻脈沖輸出。

用CD4017組成1~17進制計數器電路

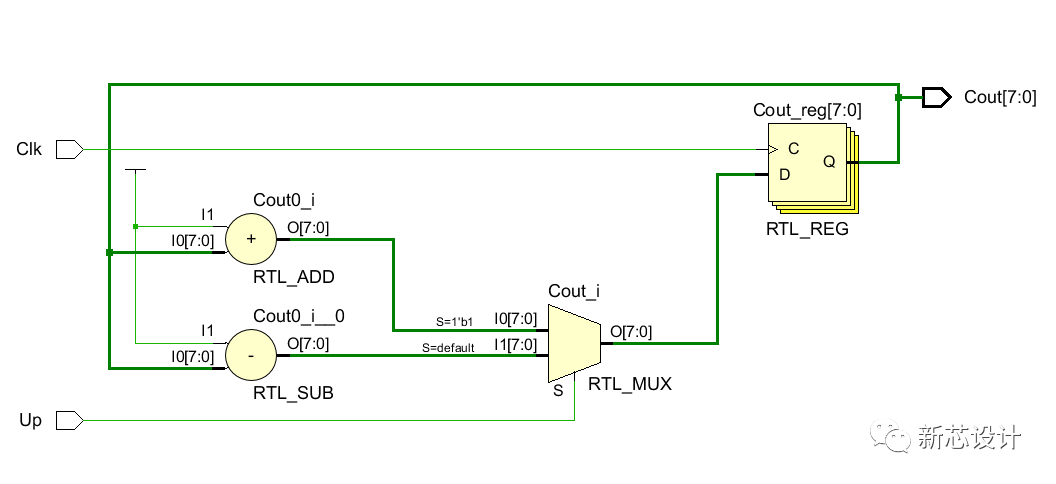

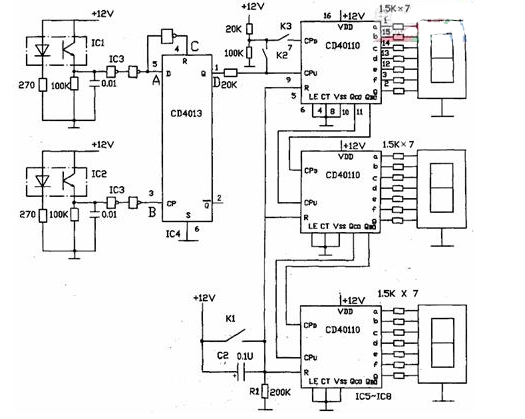

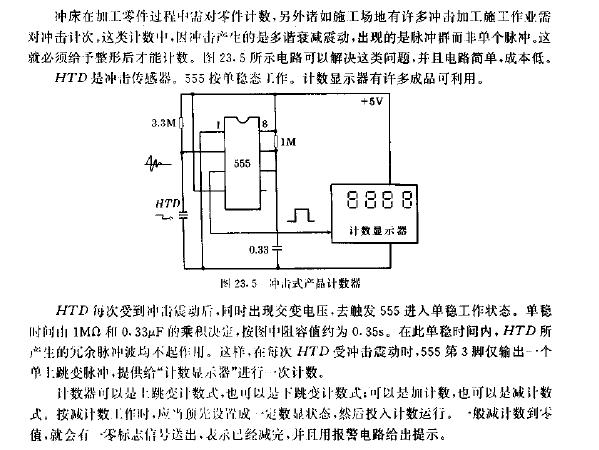

脈沖計數器電路圖設計(六)

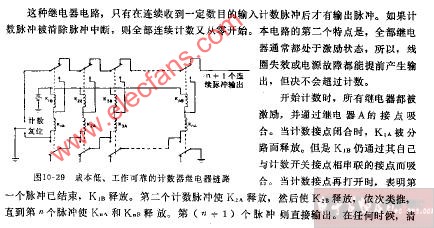

電路中由兩個與非門構成單脈沖發生器,74LS161計數器對其產生的脈沖進行計數,計數結果送入字符譯碼器并驅動七段數碼管,使數碼管顯示單脈沖發生器產生了多少個脈沖信號。

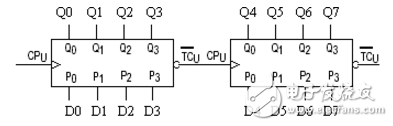

74LS161計數器的級連使用:下圖是由74LS192利用進位輸出控制高一位的加計數端構成的加數級連示意圖:

電子發燒友App

電子發燒友App

評論