數字電路設計中,如計數器、存儲器和時鐘電路等。 施密特觸發器的基本工作原理是,當輸入信號超過一定閾值時,輸出信號將被切換,并保持穩定狀態,一旦輸入信號低于另一個閾值,輸出信號將再次切換,并保持另一個穩定狀態。因此

2023-10-24 10:32:41 19

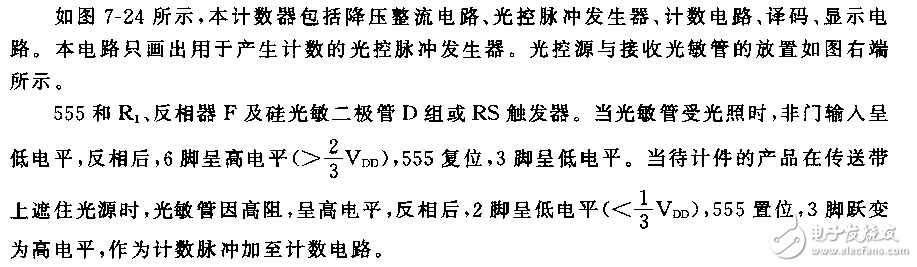

19 計數器是一個用以實現計數功能的時序部件,它不僅可用來計脈沖數,還常用作數字系統的定時、分頻和執行數字運算以及其它特定的邏輯功能。

2023-10-11 09:41:13 170

170

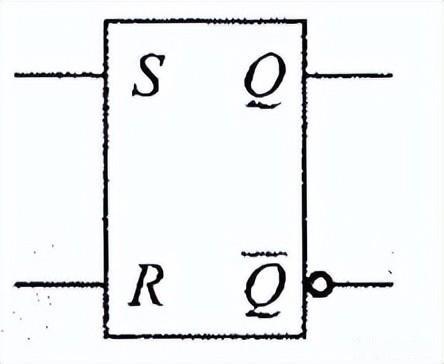

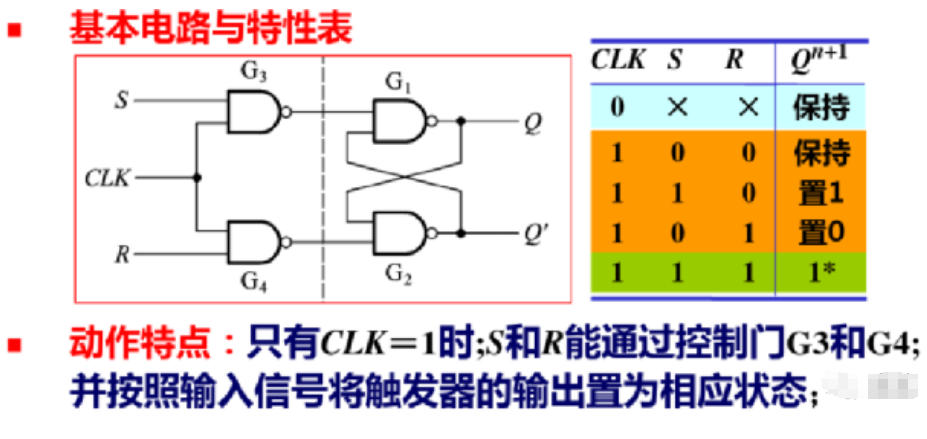

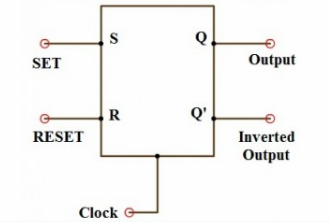

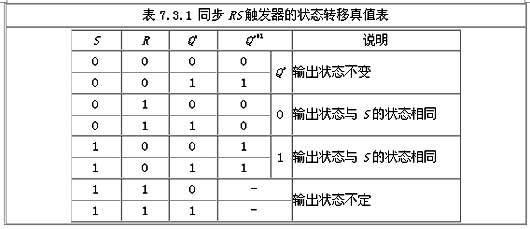

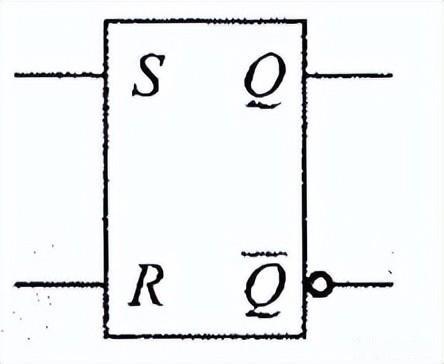

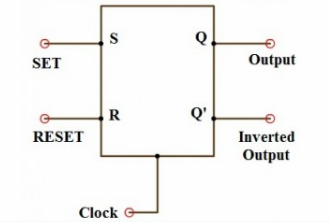

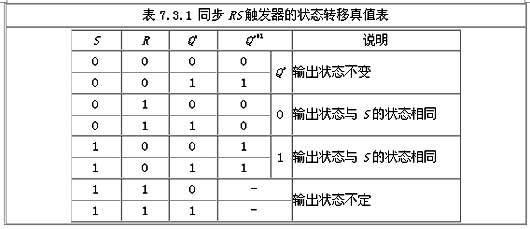

在數字電路中,RS觸發器(也稱為RS鎖存器)是一種基本的雙穩態觸發器,它可以通過特定的輸入信號來實現置位(Set)和復位(Reset)操作。

2023-09-28 16:31:07 1317

1317 觸發器(Flip-Flop)是數字電路中的一種時序邏輯元件,用于存儲二進制位的狀態。它是數字電路設計中的基本構建塊之一,常用于存儲數據、實現狀態機、控制信號的生成等。觸發器可以看作是一種特殊

2023-08-31 10:50:19 1435

1435

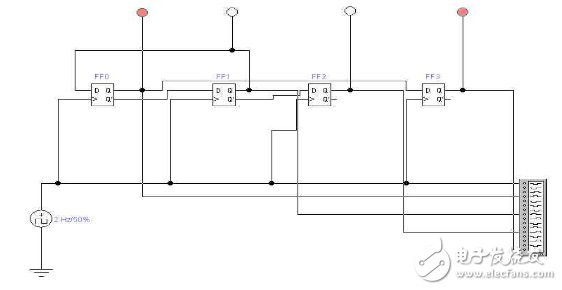

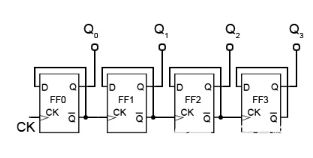

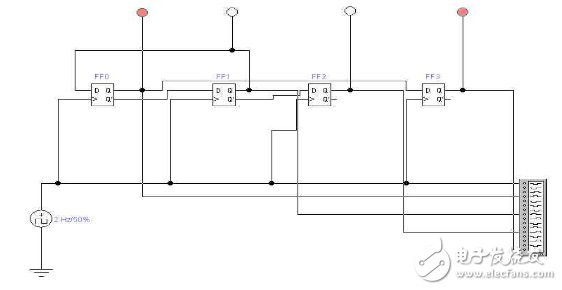

用D觸發器設計一個序列發生器 怎么用D觸發器做序列信號發生器? 序列發生器是數字電子技術中常用的電路模塊之一,它可以用來生成一系列的數字信號序列。在數字電路中,D觸發器是一種被廣泛使用的數字邏輯組件

2023-08-24 15:50:17 549

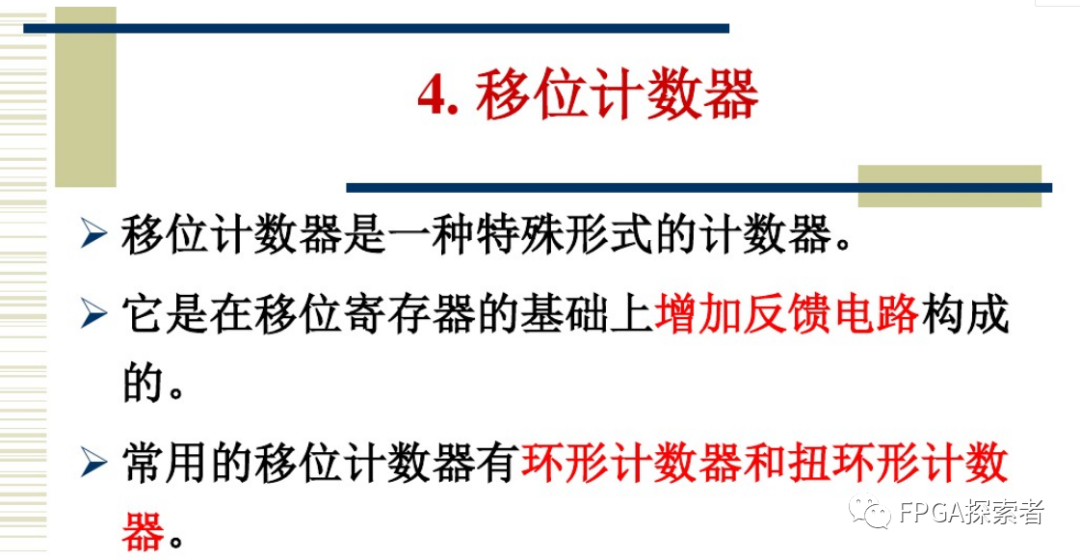

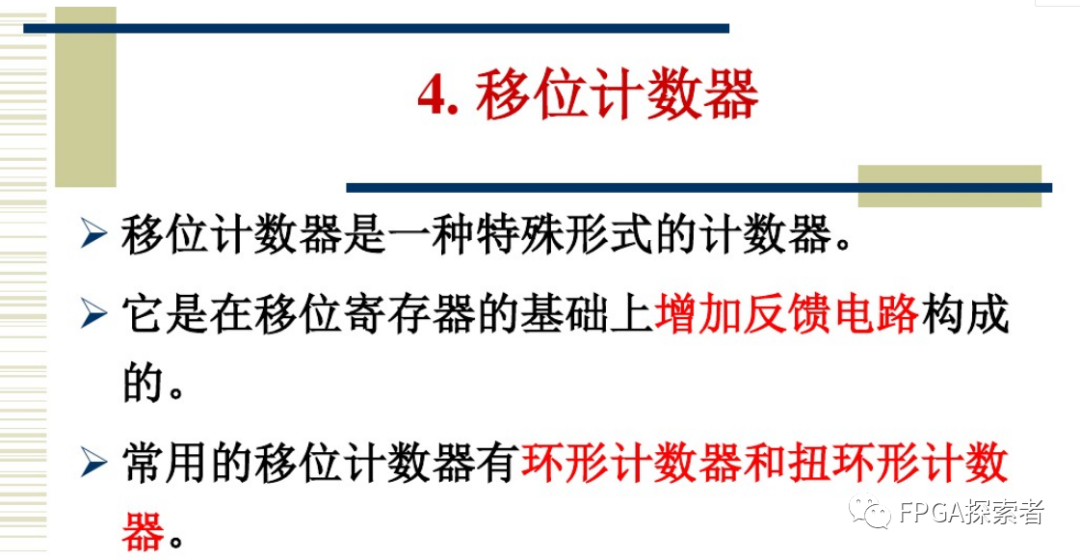

549 扭環形計數器,每次狀態變化時僅有一個觸發器發生翻轉,譯碼不存在競爭冒險,在n(n≥3)位計數器中,使用2n個狀態,有2^n-2n個狀態未使用;

2023-06-27 10:18:23 297

297

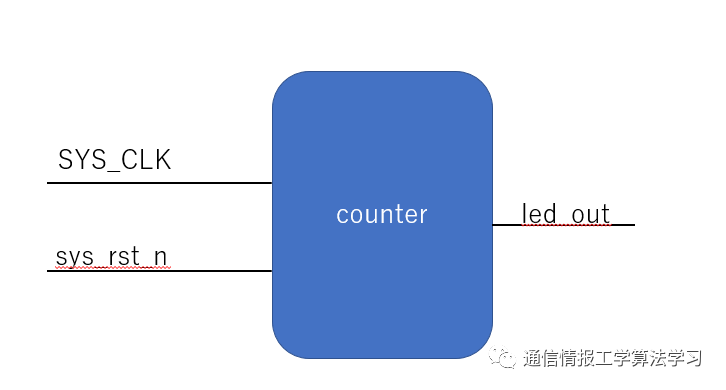

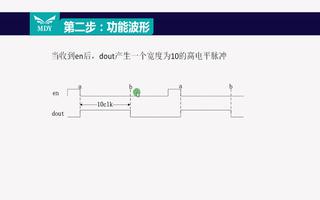

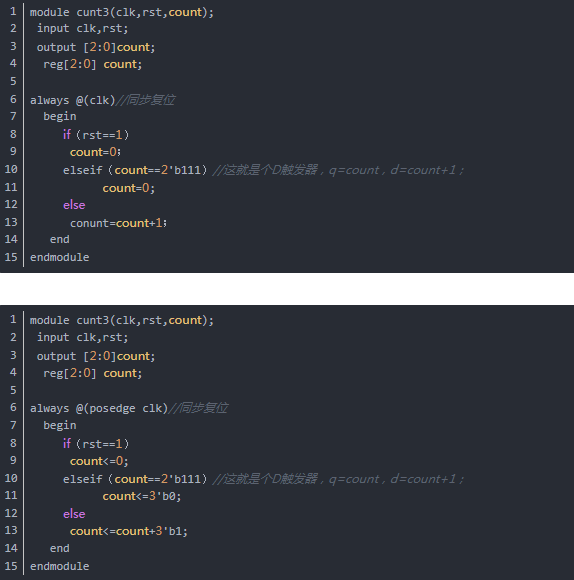

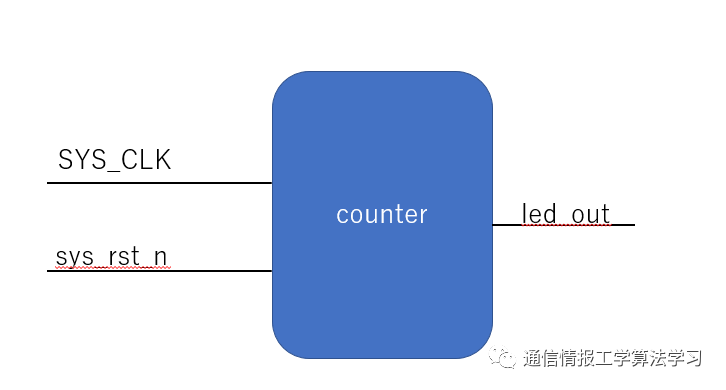

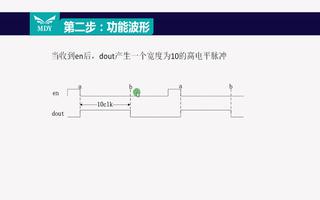

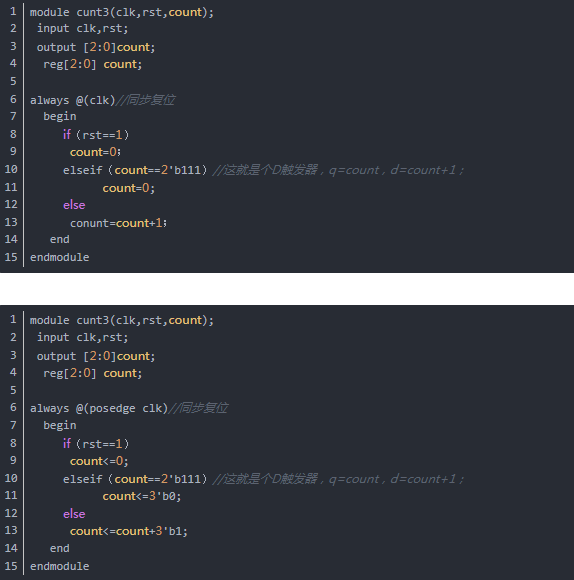

前面已經學習了時序邏輯電路中的基本單元:觸發器,這次就用其來整點活,實現計數器的設計,計數器可以說是任何和時序有關的設計都會用到他。

2023-05-22 16:54:50 886

886

在數字電子產品中,計數器是由一系列觸發器組成的時序邏輯電路。顧名思義,計數器用于計算輸入在負或正邊沿轉換中出現的次數。根據觸發觸發器的方式,計數器可以分為兩類:同步計數器和異步計數器。了解這兩種計數器的工作原理以及它們之間的區別。

2023-03-25 17:31:07 11617

11617

在電路中,觸發器(Flip-flop)是一種組合邏輯電路,可以存儲1個二進制位的信息。 觸發器有兩個穩定的狀態:SET(置位)和RESET(復位)。 當輸入信號滿足某些條件時,觸發器可以從一個狀態轉換到另一個狀態。

2023-03-23 11:45:39 4676

4676

具有置位和復位功能的雙 JK 觸發器;上升沿觸發-74HC_HCT109_Q100

2023-02-20 19:08:44 2

2 在針對特定的ASIC或FPGA之前,綜合編譯器使用的通用觸發器具有高電平有效的置位和復位輸入。

2023-02-19 10:22:17 264

264 具有置位和復位功能的雙 D 型觸發器;上升沿觸發-74ABT74

2023-02-17 19:21:45 1

1 帶復位功能的雙 JK 觸發器;下降沿觸發-74HC73_Q100

2023-02-17 19:04:31 3

3 具有復位功能的四路 D 型觸發器;上升沿觸發-74HC_HCT175_Q100

2023-02-17 18:39:55 0

0 帶復位功能的雙 JK 觸發器;下降沿觸發-74HC_HCT107

2023-02-16 19:58:24 1

1 帶復位功能的雙 JK 觸發器;下降沿觸發-74HC_HCT107_Q100

2023-02-16 19:58:13 0

0 具有置位和復位功能的雙 JK 觸發器;正 - 邊 - 觸發-74HC_HCT109

2023-02-15 20:02:18 1

1 帶復位功能的十六進制 D 型觸發器;上升沿觸發-74HC_HCT174

2023-02-15 19:44:20 0

0 帶復位功能的八路 D 型觸發器;上升沿觸發-74HC_HCT273

2023-02-15 19:43:13 0

0 帶復位功能的雙 JK 觸發器;下降沿觸發-74HC73

2023-02-15 19:33:13 3

3 帶復位功能的低功耗D型觸發器;上升沿觸發-74AUP1G175

2023-02-14 18:54:41 0

0 帶復位功能的單D型觸發器;上升沿觸發-74LVC1G175_Q100

2023-02-10 19:22:39 0

0 圖1是基本SR觸發器及其真值表。

2023-01-31 17:52:33 6163

6163

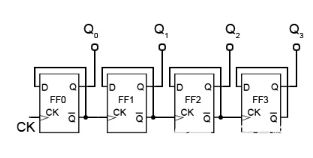

D 觸發器或數據觸發器是一種觸發器,它只有一個數據輸入“D”和一個時鐘脈沖輸入, 這種觸發器也稱為延遲觸發器,經常用于許多時序電路,如寄存器、計數器等。下面一起來了解一下D觸發器不同應用下的電路圖。

2023-01-06 14:19:46 1874

1874 構建一個4位二進制計數器,計數范圍從0到15(包括0和15),計數周期為16。同步復位輸入時,將計數器重置為0。

2022-12-02 09:20:28 1762

1762 我們用3個包含觸發器和多路選擇器的子模塊來實現圖中電路。題目要求我們寫出包含一個觸發器和一個多路選擇器的子模塊。

2022-11-17 09:37:00 511

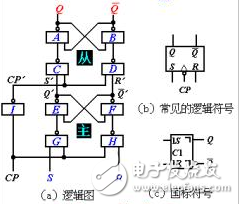

511 的輸出連接,其狀態由主觸發器的狀態決定,稱為從觸發器。電路結構 主從RS觸發器由兩個同步RS觸發器組成,它們分別稱為主觸發器和從觸發器。反相器使這兩個觸發器加上互補時鐘脈沖。如圖7.4.1所示。 工作原理: 當CP=1時,主觸發器的輸入門G7和G8打開

2022-10-19 19:16:03 16964

16964

什么是RS觸發器 其中R、S分別是英文復位 Reset 和置位 Set 的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。 RS觸發器可以用與非門實現或者

2022-10-19 17:49:59 5720

5720

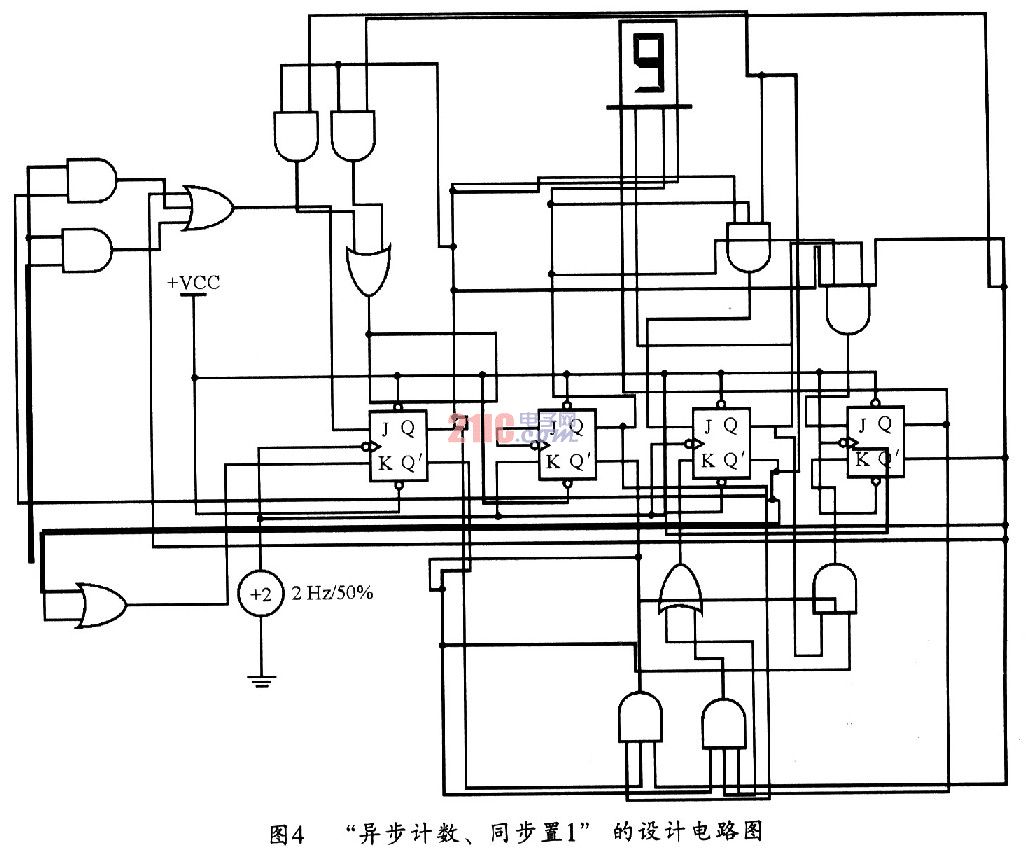

異步計數器是那些輸出不受時鐘信號影響的計數器。由于異步計數器中的觸發器提供有不同的時鐘信號,因此在產生輸出時可能會有延遲。設計異步計數器所需的邏輯門數量非常少,所以它們的設計很簡單。異步計數器的另一個名稱是“波紋計數器”。

2022-10-11 17:16:44 3105

3105

復位信號在數字電路里面的重要性僅次于時鐘信號。對一個芯片來說,復位的主要目的是使芯片電路進入一個已知的,確定的狀態。主要是觸發器進入確定的狀態。在一般情況下,芯片中的每個觸發器都應該是可復位的。

2022-09-19 10:07:20 15572

15572 你知道嗎?計算機和計算器使用觸發器來進行記憶。一定數量的觸發器組合將產生一定數量的內存。觸發器是使用邏輯門形成的,而邏輯門又由晶體管制成。

2022-09-12 16:36:00 44473

44473

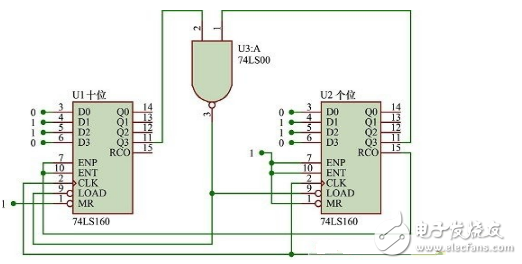

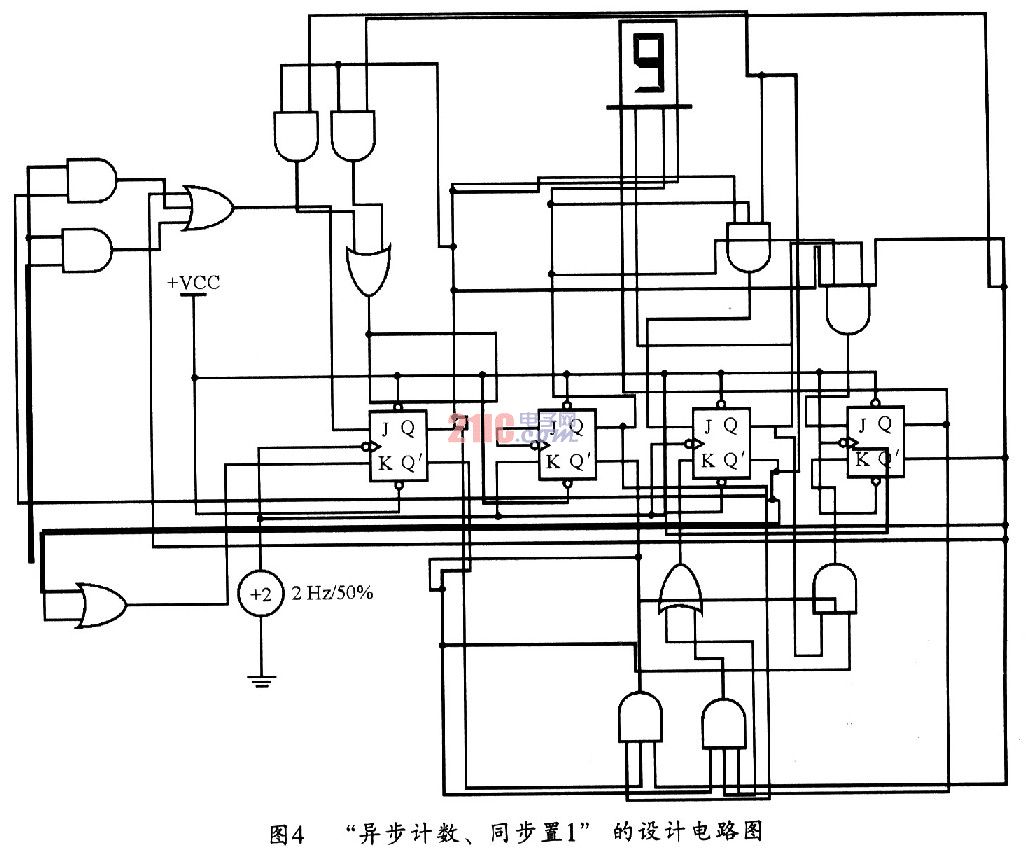

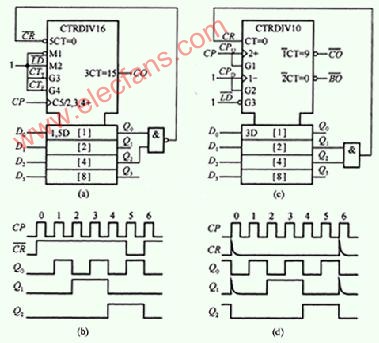

1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。

2、了解同步計數器,異步計數器的使用方法。

3、了解同步計數器通過清零阻塞法和預顯數法得到循環任意進制

2022-07-10 14:37:37 15

15 扭環形計數器,約翰遜計數器,每次狀態變化時僅有一個觸發器發生翻轉,譯碼不存在競爭冒險,在n(n≥3)位計數器中,使用2n個狀態,有2^n-2n個狀態未使用;

2022-06-15 09:27:57 1630

1630 一·定時器和計數器的原理 它們隨著計數器的輸入脈沖自行加1,每來一個脈沖,計數器自動賈1,當計數器全為1時,再輸入一個脈沖計數器回0,且計數器的溢出使相應的中斷標志位置1,向CPU發出中斷請求

2021-11-23 16:22:32 19

19 集成觸發器、集成計數器及譯碼顯示電路實驗目的1. 驗證基本RS、D、JK觸發器的邏輯功能。2. 了解十進制加法計數器和減法計數器的工作過程。3. 了解計數、譯碼、顯示電路的工作狀態。實驗原理在數

2008-12-11 23:38:01

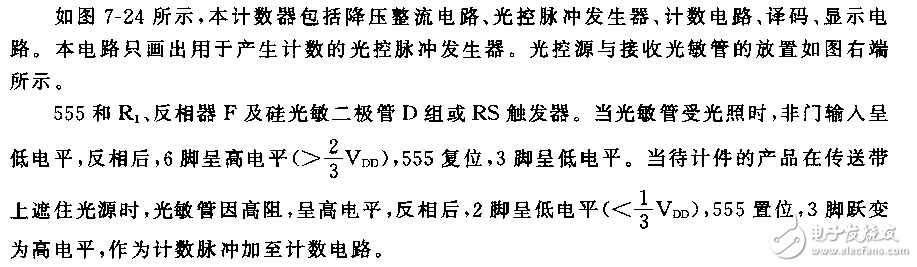

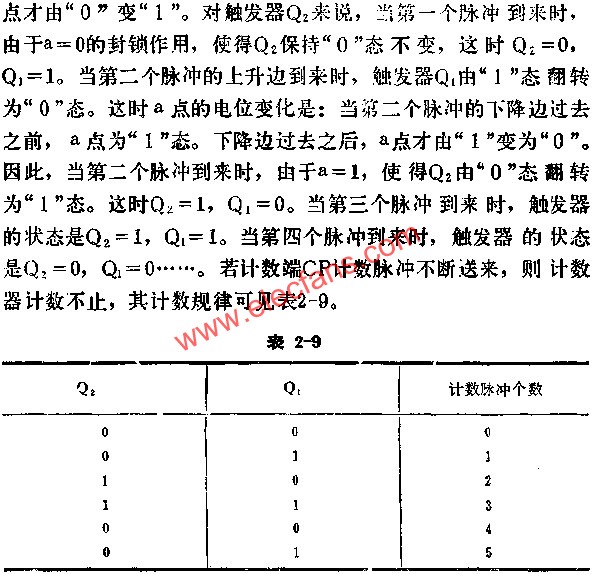

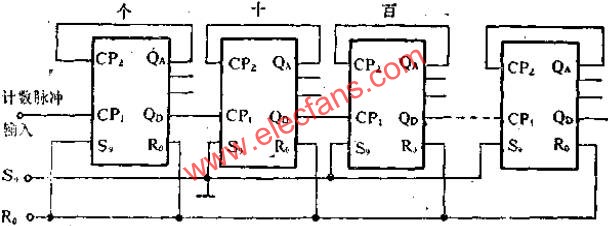

單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。 如何用二進制加法計數器芯片接成計數長度為6的計數器? 其實很簡單:用兩片級聯,第一片

2021-07-13 14:09:37 11289

11289 復位/置位觸發器(R、S分別是英文復位,置位的縮寫)也叫做基本R-S觸發器,是最簡單的一種觸發器,是構成各種復雜觸發器的基礎。

2021-06-30 17:13:06 91461

91461

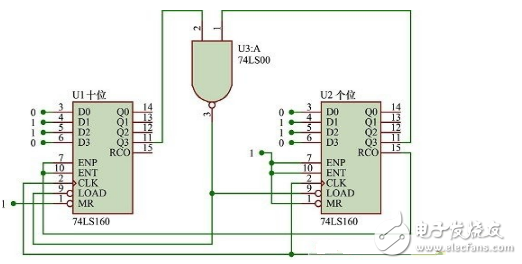

芯片74ls160是十進制計數器,這種同步可預置十進計數器是由四個D型觸發器和若干個門電路構成。

2021-06-05 14:35:38 12686

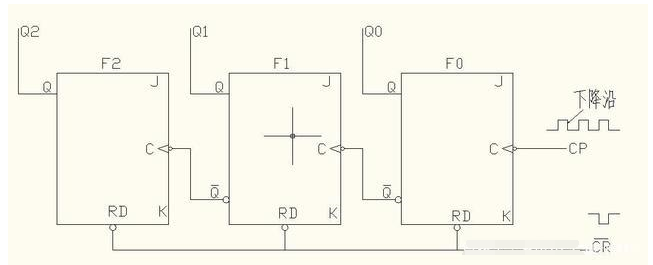

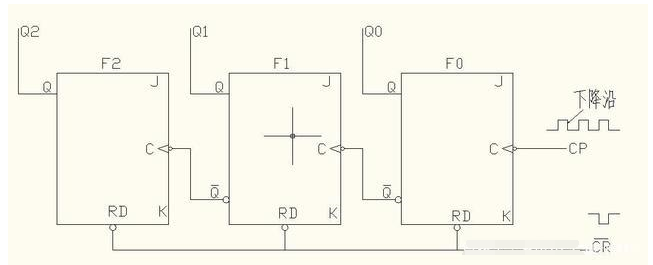

12686 該計數器是一個3位二進制異步減法計數器,它與前面介紹過的3位二進制異步加法計 數器一樣,是由3個JK觸發器組成,其中J、K端都懸空(相當于J=1、K=1),兩者的不同 之處在于,減法計數器是將前一個觸發器的Q非端與下一個觸發器的CP端相連。

2021-04-18 11:19:47 15455

15455

脈沖觸發器由兩個相同的電平觸發的SR觸發器組成,其中左SR觸發器成為主觸發器,右手側稱為從觸發器。

2021-02-11 10:56:00 6965

6965

HD74LS93包含四個主從觸發器和額外的選通,提供一個除以2計數器和用于除以的三態二進制計數器-八,到使用此計數器的最大計數長度,B輸入連接到Qa輸出輸入計數脈沖應用于輸入A,并在適當的功能表。

2020-05-26 08:00:00 0

0 74LS92是一個4級紋波計數器,包含一個高速觸發器,用作除以2,三個觸發器連接作為除以-6.高主復位(MR)輸入上的信號覆蓋時鐘,并強制所有輸出進入低狀態。

2020-05-26 08:00:00 1

1 計數器是由基本的計數單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等,計數器在數字系統中應用廣泛。

2019-12-19 07:09:00 2315

2315

計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。

2019-09-29 07:05:00 751

751

觸發器是一個具有異步復位異步置數的器件,那么怎么樣Verilog來具體描述這個器件呢,接下來我們就來看一下,

2019-07-26 10:17:16 23884

23884

D型觸發器是一個改進的置位復位觸發器,增加了一個反相器,由此可見以防止S和R輸入處于相同的邏輯電平,此狀態將強制兩個輸出都處于邏輯“1”,超越反饋鎖存動作,無論哪個輸入先進入邏輯電平“1”都將失去控制,而另一個仍處于邏輯“0”的輸入控制鎖存器的結果狀態。

2019-06-26 15:36:28 14537

14537

異步計數器使用串聯連接在一起的觸發器,使輸入時鐘脈沖看起來通過計數器紋波。

2019-06-23 10:39:41 17874

17874

同步計數器之所以被稱為是因為計數器內所有單個觸發器的時鐘輸入都由同一時鐘信號同時同時計時。

2019-06-23 10:16:39 23837

23837

我們之前看到,切換T型觸發器可以作為個體使用除以兩個計數器。如果我們將串聯鏈中的幾個觸發器觸發器連接在一起,我們就可以生成一個數字計數器,用于存儲或顯示特定計數序列發生的次數。

2019-06-23 08:47:00 14774

14774

分析:首先,我們可以看到有哪些信號。復位rst 、計數器3位的、時鐘信號。(用到2路選擇器。復位和不復位)

其次,怎樣實現,一個時鐘過來,記一次數就是加一次,保存(用到D觸發器),滿之后為0;

2019-02-01 07:08:00 2170

2170

,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。計數器在數字系統中應用廣泛,如在電子計算機的控制器中對指令地址進行計數,以便順序取出下一條指令,在運算器中作乘法、除法運算時記下加法、減法次數,又如在數字儀器中對脈沖的計數等等。

2019-01-24 14:35:40 62199

62199 本文主要介紹了雙穩態觸發器的工作原理詳解。雙穩態觸發器是脈沖和數字電路中常用的基本觸發器之一。雙穩態觸發器的特點是具有兩個穩定的狀態,并且在外加觸發信號的作用下,可以由一種穩定狀態轉換為另一種穩定

2018-04-04 10:58:47 93353

93353

本文主要介紹了單穩態觸發器芯片有哪些_單穩態觸發器工作原理。單穩態觸發器只有一個穩定狀態,一個暫穩態。在外加脈沖的作用下,單穩態觸發器可以從一個穩定狀態翻轉到一個暫穩態。由于電路中RC延時環節的作用

2018-03-28 18:22:32 27069

27069

和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。計數器在數字系統

2018-03-26 11:22:00 84513

84513

主從RS觸發器由兩個同步RS觸發器組成,它們分別稱為主觸發器和從觸發器。反相器使這兩個觸發器加上互補時鐘脈沖。

2018-02-08 14:23:24 23829

23829

,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。本文為大家帶來七種任意進制計數器設計方案及其電路設計的原理詳解。

2018-01-17 17:36:07 67188

67188

環形計數器是由移位寄存器加上一定的反饋電路構成的,用移位寄存器構成環形計數器的一般框圖,它是由一個移位寄存器和一個組合反饋邏輯電路閉環構成,反饋電路的輸出接向移位寄存器的串行輸入端,反饋電路的輸入端根據移位寄存器計數器類型的不同,可接向移位寄存器的串行輸出端或某些觸發器的輸出端。

2018-01-16 14:54:44 40935

40935

,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。計數器在數字系統中應用廣泛,如在電子計算機的控制器中對指令地址進行計數,以便順序取出下一條指令,在運

2017-10-23 17:48:48 15

15 ,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。計數器在數字系統中應用廣泛,如在電子計算機的控制器中對指令地址進行計數,以便順序取出下一條指令,在運

2017-09-25 10:13:37 8

8 CC4060 由一震蕩器和14 極二進制串行計數器位組成,震蕩器的結構可以是RC 或晶振電路。CR 為高電平時,計數器清零且振蕩器使用無效,所有的計數器位均為主從觸發器。

2012-03-29 15:01:57 196

196 異步計數器電路是指其構成的基本功能單元觸發器的時鐘輸入信號不是與觸發器在一起的,有的是外輸入的脈沖信號,有的是其他觸發器的輸出。本文給出了N進制 異步計數器 設計方案

2011-10-24 15:39:38 3245

3245

C182可預置數1/N計數器基本上是一個減法計數器,均由四個"T"型觸發器和附加控制門組成,具有級連N個計數器

2010-10-19 15:23:07 963

963

T210計數器(TTL)是異步計數器,它的內部有四個觸發器,第一個觸發器有獨立的時鐘輸入CP1和輸出QA,其余三個

2010-10-19 12:39:04 1723

1723

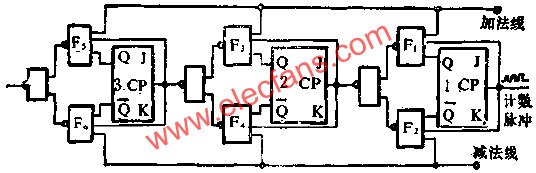

圖中所示是J-K觸發器組成可逆計數器電路。要求計數器能夠在一定條件下,從加法計數改換成減法計數,也可以

2010-09-24 01:03:53 2756

2756

圖中所示是用CMOS電路D觸發器組成的十進制環形計數器.圖中先將D觸發器拼成移位寄存器,然后把最后一級D觸發器

2010-09-20 23:46:58 17358

17358

上例圖中A將D觸發器的D端和Q相連,即可組成二分頻電路,如果把三個D觸發器串行相連,如圖所示,則經過一

2010-09-20 03:40:48 11549

11549 圖中所示是用與非門組成的二進制計數器,實際上它是用與非門組成的維持-阻塞觸發器而組成的計數器.圖

2010-09-19 00:54:13 2214

2214

一、基本要求1、理解R-S觸發器、J-K觸發器和D觸發器的邏輯功能;2、掌握觸發器構成的時序電路的分析,并了解其設計方法;3、理解計數器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 觸發器是數字電路的基本邏輯單元之一,也是構成各種時序電路的最基本邏輯單元。

文中給出了基于JK觸發器來設計十二歸一計數器的設計和實現方法,并通過EWB軟件進行了

2010-06-30 15:58:29 14012

14012

計數器的定義和分類

計數器定義在數字電路中,計數器屬于時序電路,它主要由具有記憶功能的觸發器構成。計數器不僅僅

2010-03-08 17:37:35 11724

11724 施密特觸發器,施密特觸發器是什么意思

施密特觸發器也有兩個穩定狀態,但與一般觸發器不同的是,施密特觸發器采用電位觸發

2010-03-08 14:14:56 1763

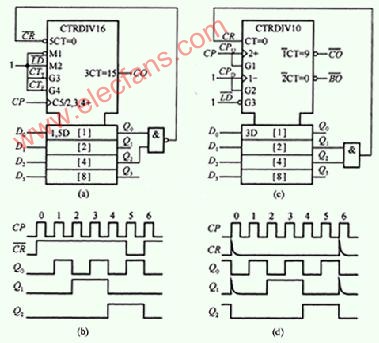

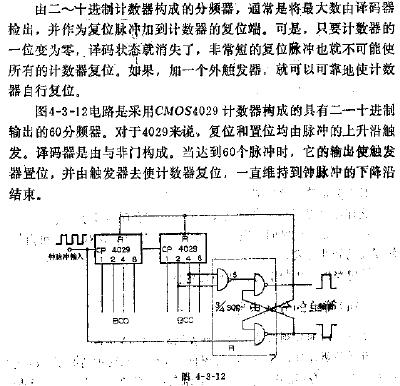

1763 利用復位端構成的模6計數器電路

利用集成計數器的預置端和復位端可以構成任意模計數器。下圖所示依次是利用74163和74192構成的

2010-01-12 13:54:31 4276

4276

第二十五講 同步計數器

7.3.2 同步計數器一、同步二進制計數器1.同步二進制加法計數器JK觸發器組成的4位同步二進制加法

2009-03-30 16:28:45 7879

7879

D觸發器的功能測試74LS74型雙D觸發器芯片引腳圖,D觸發器功能測試的引腳連線圖,D觸發器功能測試的引腳連線圖,用D觸發器構成二進制計數器,用D觸發器構成四位移位寄存器

J-K

2009-02-14 15:27:51 290

290

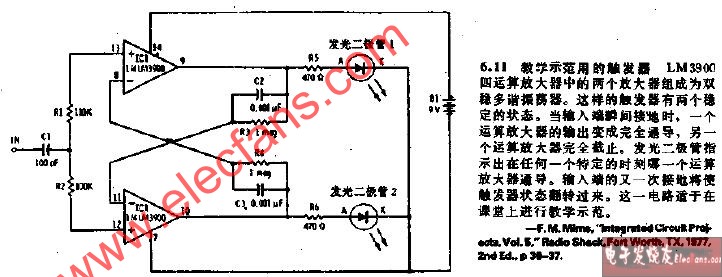

教學示范用的觸發器電路

2009-01-17 14:04:09 426

426

電子發燒友App

電子發燒友App

硬聲App

硬聲App

19

19 170

170

1317

1317 1435

1435

549

549 297

297

886

886

11617

11617

4676

4676

2

2 264

264 1874

1874 16964

16964

5720

5720

3105

3105

15572

15572 44473

44473

15

15 1630

1630 19

19 11289

11289 91461

91461

15455

15455

0

0 1

1 2315

2315

751

751

14537

14537

14774

14774

2170

2170

62199

62199 93353

93353

27069

27069

84513

84513

67188

67188

40935

40935

15

15 8

8 196

196 3245

3245

1723

1723

57

57 14012

14012

4276

4276

290

290

評論