摘 要:本文簡述了TMS320C5409與MAX125之間的硬件接口設計和軟件編程方法及其在聲強測試系統中的應用。

引言

隨著“綠色設計”的興起和人們對環境保護的意識增強,噪聲控制已成為現代工業發展的一項重大任務。而低噪產品設計很大程度上依賴于聲強測量。通過測量分析,可以了解產生振動和噪聲的原因,從而找到降低噪聲的有效途徑。過去的聲強測試系統中,一般基于單片機技術,數據處理能力差、可擴展空間小,只能實現時域分析。近年來,隨著信息處理技術的飛速發展,DSP在電子信息、儀器儀表等高科技領域得到了廣泛的運用。它具備特有的哈佛結構、多級流水線、硬件乘法器等特征,所以運算速度很快。如果將它運用于聲強 測試系統中可實現實時頻譜分析,提高測試的精度。而MAX125是內部集成采樣保持電路和多路選通電路的ADC芯片,最多能實現4個通道的模擬信號同步采樣,非常適合多通道聲強數據采集系統。

聲強測試系統中的ADC模塊

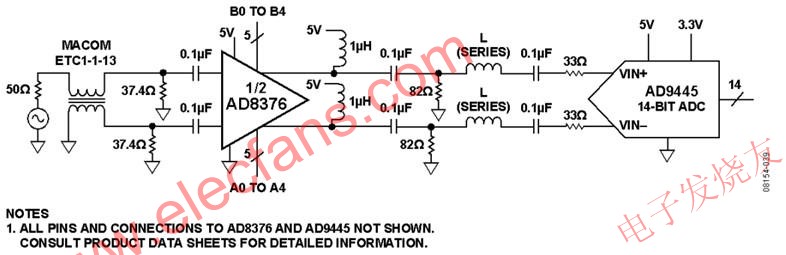

聲強測試中,噪聲信號的頻率為20Hz~20KHz,且要求系統進行高精度多通道并行采樣。根據這方面的要求選擇MAXIM公司的MAX125。它是高速2x4通道同步采樣14位逐次比較型A/D轉換器芯片,內部集成采樣保持電路。在4通道工作模式下,ADC芯片最高可以支持76KHz的高速采樣。所以即使在4通道同時采樣的情況下,它也可以滿足聲強數據采集的要求。同時,模擬電路十分簡單,抗干擾能力強、精度也高。

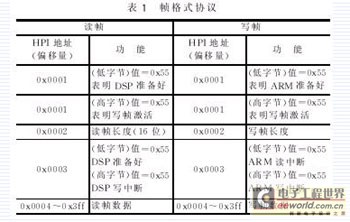

如表1所示,MAX125有8種通道轉換方式,并通過A0~A3引腳編程實現。上電時,芯片自動選擇CH1A作為轉換通道。用戶可編程選擇CH1A-CH4A或CH1B-CH4B這兩組中的任何4個通道。

聲強測試系統中的DSP

聲強測試系統要進行實時信號分析,要求有較高運算速度,同時信號處理也需要較大緩存空間。在各種算法中,FFT變換是基礎,也最占時間,所以我們可用FFT驗證DSP速度是否符合要求。在FFT變換中,N點復數做FFT變換約需要2N×Log2N次實數乘法運算和3N×Log2N實時加法運算。如果選擇TI公司的TMS320VC5409,它的乘法和加法都是單周期指令,取N=1024,不計內存訪問和其它時間,則一次FFT所需時間為:10×5120×10ns約0.512ms。按4通道76KSPS的采樣頻率計算,1024點的采樣時間約為3.333ms,可見該DSP速度足以滿足要求。所以本系統選用TI公司的16位定點DSP—TMS320VC5409 (TI公司產品)。重要的是它片內具有32×16bit內部RAM,這對提高聲強測試系統的整體性能有很大的幫助。

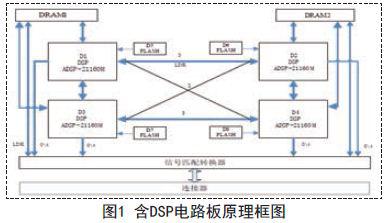

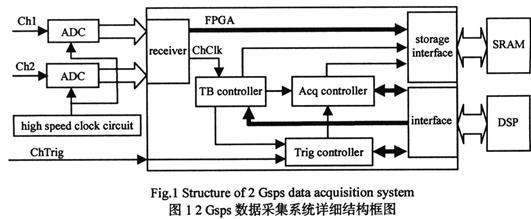

圖1 聲強測試系統結構框圖

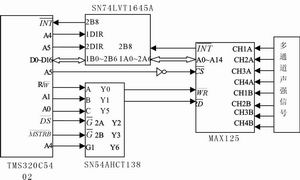

圖2 MAX125與C54的接口電路

聲強測試系統中MAX125與TMS320VC5409的接口

圖1為聲強測試系統的結構簡圖,圖中多路聲強信號在MAX125中實現A/D轉換后,采樣結果通過中斷方式輸入DSP中進行運算處理(FFT變換、相關分析、功率譜分析等),處理結果由USB接口送至主控計算機存儲和顯示。CPLD實現模塊接口控制邏輯,包括地址跟隨、數據鎖存等功能,8254則為MAX125等提供時鐘信號,便于上位機對時鐘信號的控制。

MAX125與TMS320C54的接口電路示圖2,在系統中,多路聲強模擬信號分別接MAX125的CH1A-CH4A和CH1B-CH4B通道上,MAX125實現A/D轉換后通過接口讀入TMS320C54進行信號處理。MAX125與TMS320C54之間的接口設計主要要考慮兩個問題:3V和5V混合邏輯的設計:C54的外圍工作電壓為3.3V,而它的外圍器件包括MAX125一般工作在5V,必須為DSP和外圍芯片設計一個安全可靠的接口;速度匹配問題:MAX125的時序要求兩次讀操作之間的延遲時間不小于40nS, TMS320C54的指令執行周期為10nS.所以,DSP讀寫A/D時必須解決速度匹配問題。

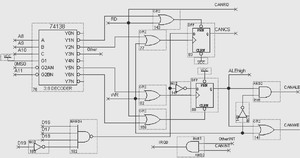

如圖2所示,C54的數據總線掛有一個SN74LVT1645A,它是TI公司的3.3V和5V雙向收發器, SN74LVT1645A可以看作兩個8位收發器或一個16位收發器。收發的方向由兩個方向控制引腳(DIR)控制。這樣在數據總線上既可為DSP提供驅動5V數字電路的能力,也可為DSP提供5V信號讀入的保護。所以使用SN74LVT1645A可以為DSP擴展多個外設提供可靠的接口,解決了3.3V和5V混合邏輯設計問題。TMS320VC54X與慢速器件接口可采用硬件或軟件的方法插入等待狀態。軟件的方法插入等待狀態的 方法是通過TMS320C54X內部一個軟件等待狀態寄存器實現的,它最多插入7可等待狀態,非常方便。通過分析在與MAX125接口中最多插入三個等待狀態即可,所以在接口中我們采用了軟件插入等待周期的方法。時鐘信號CLK和啟動轉換信號由可編程計數器/定時器8254為MAX125提供,8254則由上位機通過USB接口控制,從而上位機可以通過USB接口控制MAX125的采樣頻率。高速譯碼器SN74AHCT138用于產生MAX125所需的讀寫信號、和片選信號,簡化了電路結構。TMS320VC54和MAX125之間采了中斷控制的工作方式,在MAX125每完成一次A/D轉換以后,它通過中斷通知TMS320VC54讀取數據,在MAX125進行A/D轉換時,它不受MAX125的影響,這樣提高了TMS320VC54的工作效率。

MAX125與TMS320VC54接口程序

下面給出了MAX125中4通道采樣的接口程序,程序中采用中斷方式讀取數據。將MAX125的端口作為TMS320VC54擴展的外部存儲單元。

MAX125端口占用的地址空間為:

工作方式編程地址ADIN=8000;

獲取轉換結果的地址ADOUT=800C

ADIN .set 8000h

ADOUT .set 800Ch

DSPIN .set 0800h ;0800h為DSP內部

數據緩存區間的首地址

中斷矢量程序

int2: B INT

NOP

NOP

.space 13*4*16

接口初始化程序

_c_int00:

LD #0,DP ;設置頁指針

STM #3000h,SP ;設置堆棧指針

SSBX INTM ;關閉所有中斷

STM #0F4BFh,SWWSR ;設置等待

發生器

ST #3h,ADIN ;設置B組四通道

采樣

STM #0F6FFh,SWWSR ;設置等待

發生器

STM #0FFFFh,IFR ;清除中斷標志

寄存器

STM #0004h,IMR ;開放中斷2

RSBX INTM ;開放所有中斷

中斷子程序

INT PSHM AR3

PSHM AR2

PSHM AR0 ;保護現場

STM #1,ARO

STM #2048,BK

STM #ADOUT,AR2

STM #DSPIN,AR3

RPT #3

MVDD *AR2,*AR3+0% ;

四次讀操作

POPM AR0

POPM AR2

POPM AR3 ;恢復現場

RETE

.end

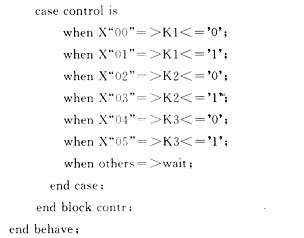

程序設計中要注意下面的問題:

MAX125的時序要求兩次讀操作之間的延遲時間不小于40nS,而TMS320VC5409的指令執行周期為10nS。所以,TMS320VC5409讀寫A/D時必須插入等待周期.在進行存儲器寫操作時,TMS320VC5409需兩個機器周期;在進行存儲器讀操作時,TMS320VC5409只需一個機器周期。由此可以得出,在MAX125與TMS320VC5409的接口中,對MAX125的寫操作至少需要插入兩個機器周期;讀操作時至少需要插入三個周期。

結語

本接口電路簡單、成本低廉,充分利用了MAX125的多同道A/D轉換功能和TMS320VC5409較強的數據處理能力,滿足了多同道聲強測量的要求。目前,該電路已運用于安徽省十五重點項目“智能聲強測試系統”中,效果良好。

- 接口電路(56780)

- 聲強測試(6751)

相關推薦

基于EMIF接口的DSP控制系統設計

5573

5573

針對含DSP電路板的測試方法與診斷分析

8277

8277

ADC在數據采集系統中的研究及應用

DSP FIFO ADC讀取數據問題

DSP NSAT-2000自動化測試系統

DSP2812的輸入問題

DSP系統設計100問

DSP_的USB_接口電路原理

DSP與PC機串行通信接口硬件設計

DSP小系統接口電路可移植性設計方案

DSP硬件系統的基本設計中時鐘電路的設計

CAN總線控制器與DSP的接口

GS-AIM聲強報警音頻矩陣系統控制軟件使用說明書

MCU SPI接口如何訪問非標準SPI ADC

【TL6748 DSP申請】噪聲實時分析系統

一文教你如何進行ADC的外圍電路設計!

一種基于DSP的嵌入式系統人機接口設計介紹

一種基于FPGA的光纖陀螺慣導系統溫控電路接口設計

在數據采集系統中的DSP技術應用

基于DSP平臺的USB接口硬件方案設計

基于DSP的CompactFlash卡接口設計

基于DSP的列車應變力測試系統設計

基于DSP的嵌入式以太網接口電路設計

基于C66x平臺DSP與FPGA通信測試

基于CPLD的DSP與聲卡的接口技術

基于邊界掃描的電路板快速測試系統設計

如何利用DSP平臺設計USB接口?

嵌入式系統接口測試

怎么實現ARM/DSP雙核系統的通信接口的設計?

流水線型模數轉換器MAX1200及其與DSP的接口

電壓監控ADC系統中輸入電壓和輸出接口隔離問題

請問我的ADC與DSP的EMIF接口設計還有問題嗎?

通過FPGA實現溫控電路接口及其與DSP通信接口的設計

采用DSP平臺實現USB接口設計

采用CPCI總線多DSP系統實現高速主機接口設計

采用CPLD的DSP與聲卡的接口電路設計

采用CPLD的DSP與聲卡的接口技術

采用USB接口和DSP實現飛機防滑剎車測試系統設計

采用USB接口和DSP實現飛機防滑剎車測試系統設計

采用USB協議實現DSP高速上位機接口設計

需要用到RJ45接口,DAC、ADC,基于DSP的MCU有什么推薦的嗎?

高速 ADC/DAC 測試原理及測試方法

高速ADC能否用DSP驅動采集數據?

基于DSP的架空電導線蠕變量測試系統研究

11

11主從模式的TLC320AC01 與DSP 的接口設計

25

25DSP應用系統中的USB接口

29

29Trimedia DSP芯片JTAG接口的仿真器設計

70

70流水線型ADC MAX1200 及其與DSP 的接口

11

11主從模式的TLC320AC01 與DSP 的接口設計

7

7測試接口原理與電源芯片應用案例

33

33基于DSP的聲音采集系統硬件設計

106

106DSP系統的測試和調試1~4

25

25基于DSP 的架空電導線蠕變量測試系統研究

17

17聲強測試系統中DSP和ADC的接口電路

5

5基于ISP的導彈測試系統接口電路設計?

864

864

SHARC DSP與SJA1000的CAN總線接口設計

1310

1310

DSP與PCI網卡接口設計

1264

1264DSP/ARM雙核系統的通信接口設計

1572

1572

DSP嵌入式系統人機接口設計

796

796

基于DSP的汽油機點火參數自動測試系統

45

45基于DSP的USB主機接口設計

46

46基于DSP接口分組件單板測試系統研究

2

2基于TLC320AC01與DSP的接口電路設計方案解析

0

0邊界掃描測試技術在帶DSP芯片數字電路板測試中的應用解析

3

3基于DSP處理器的數字電源設計

26

26基于DSP中頻電源測試系統的設計與實現

14

14采用ADC+時鐘電路+FPGA+DSP實現高分辨率的數據采集系統設計

5271

5271

基于CPLD的測試系統接口設計

1472

1472

DSP原理與應用教程之DSP系統應用硬件設計的資料說明

59

59DSP應用系統中的硬件接口電路設計

15

15AD7878:LC2MOS、完整的12位100 kHz采樣ADC,配有DSP接口

11

11DSP電路板測試中的邊界掃描技術研究綜述

9

9DSP ADC程序中文的說明

9

9DSP教程---ADC和DAC

18

18MCU SPI接口訪問非標準SPI ADC的方法!

10

10如何為DSP接口模式配置MAX2769C ADC寄存器

1243

1243

并行接口的ADC、DAC的測試方法

857

857 電子發燒友App

電子發燒友App

評論