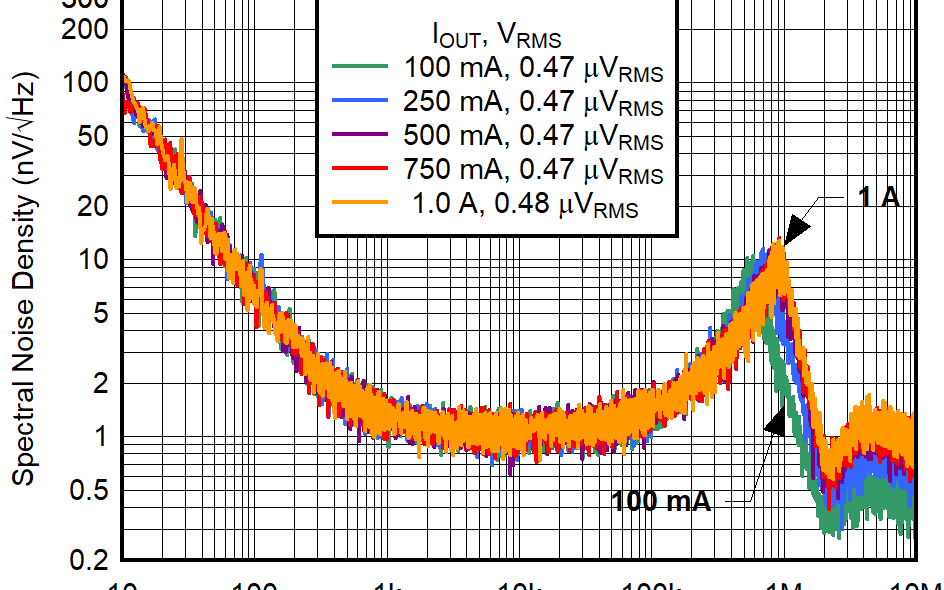

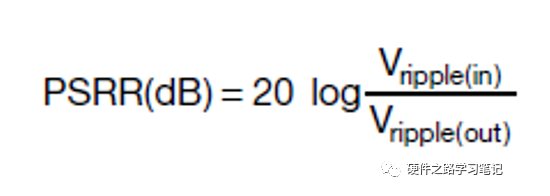

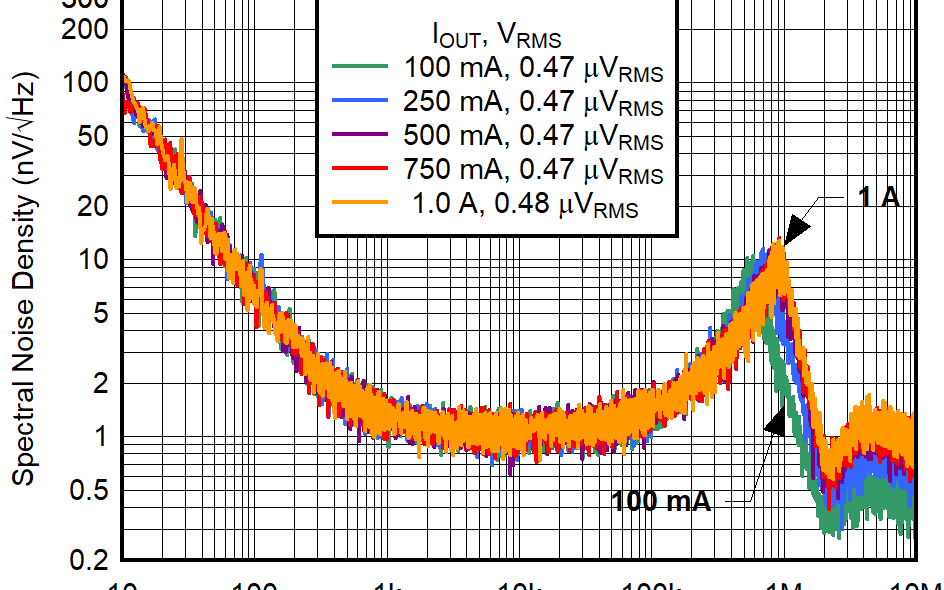

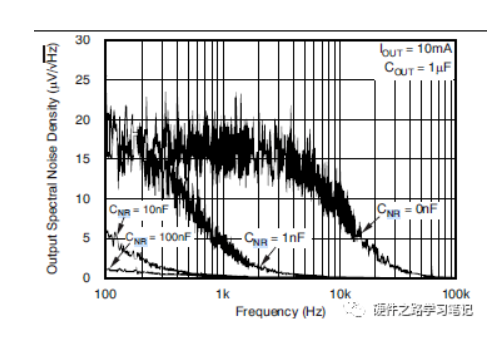

是電子器件,因此它們會自行產(chǎn)生一定量的噪聲。選擇低噪聲LDO并采取措施來降低內(nèi)部噪聲對于生成不會影響系統(tǒng)性能的清潔電源軌而言不可或缺。 識別噪聲 理想的 LDO 會生成沒有交流元件的電壓軌。遺憾的是,LDO 會像其他電子器件一樣自行產(chǎn)生噪聲。圖1顯示了這種噪聲在時(shí)域

2022-04-18 18:05:29 5781

5781

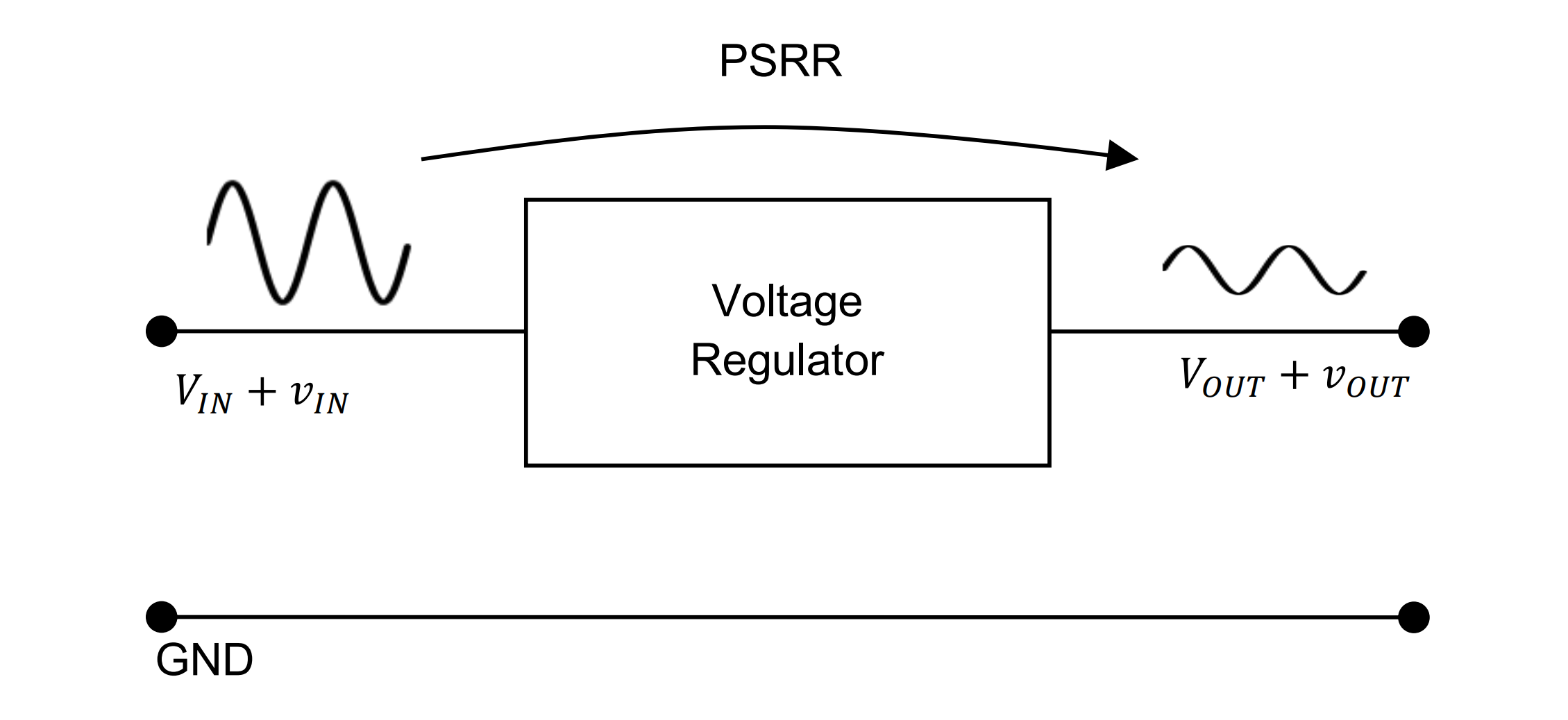

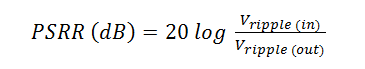

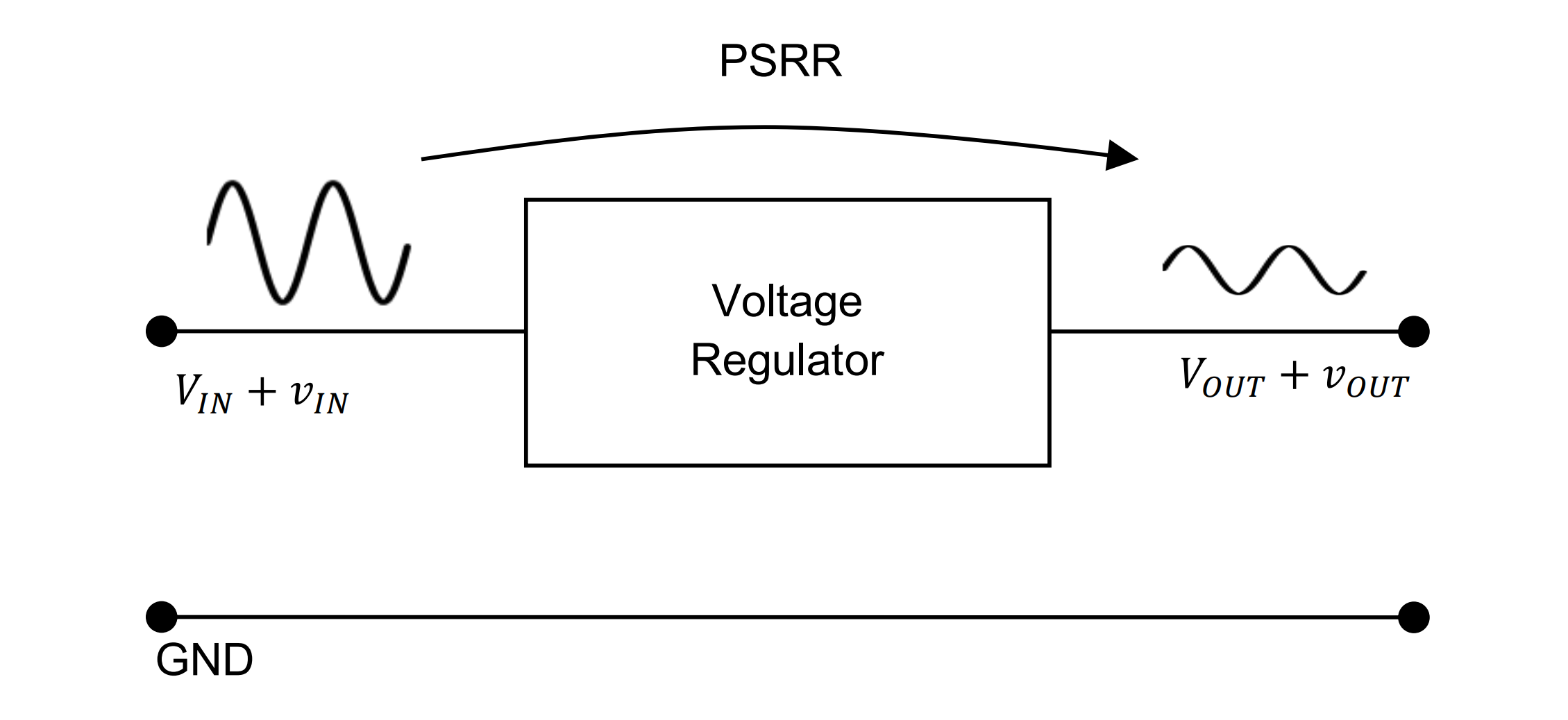

電源抑制比 (PSRR) 用于衡量 LDO 清除或抑制由上游其他元件傳入噪聲的能力。對于高端 ADC,為了更大限度地減少位錯誤,輸入電源噪聲要求不斷提高。

2022-03-09 09:24:03 1093

1093

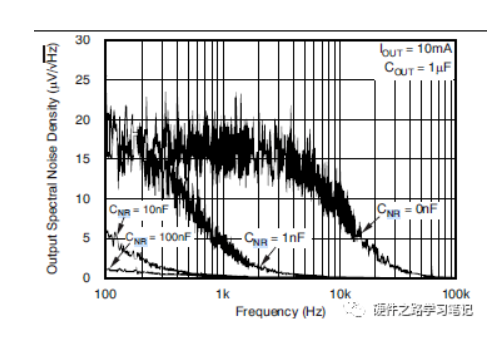

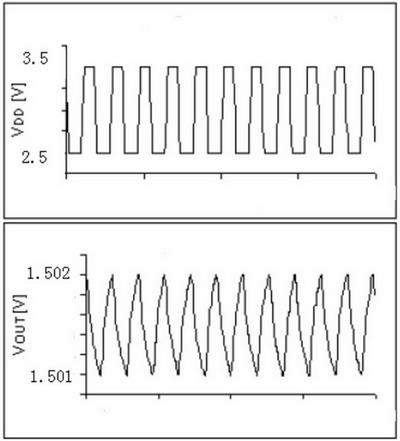

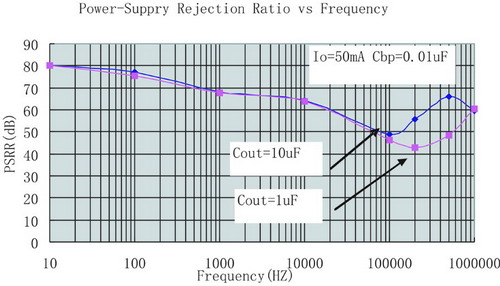

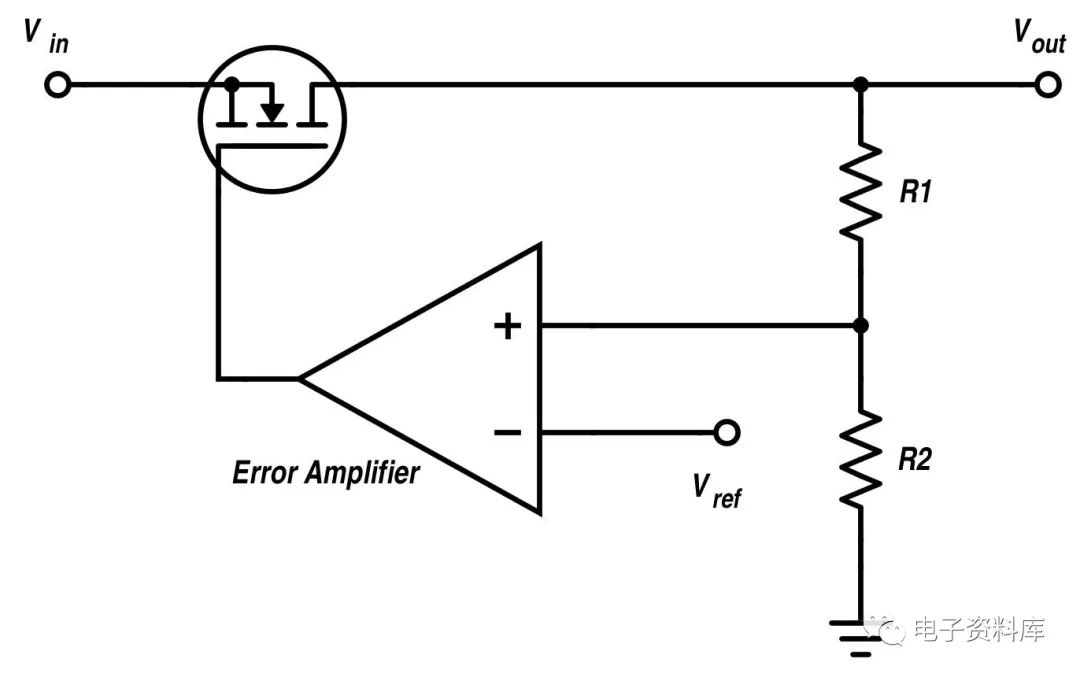

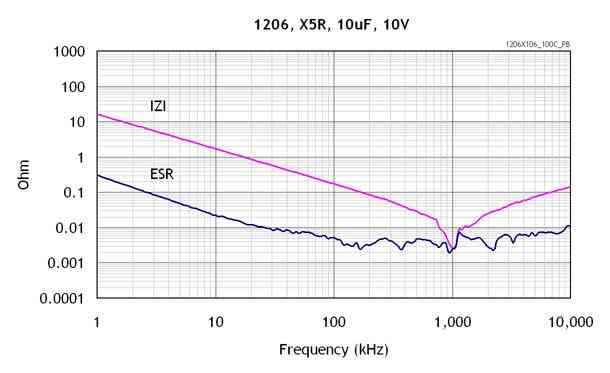

低壓差線性穩(wěn)壓器(LDO)相比 DC-DC 的優(yōu)點(diǎn)之一,是輸出電壓紋波小。但是高速電路下,LDO 的電源抑制比(PSRR)也是不可忽略的因素,通常被誤認(rèn)為是單一的靜態(tài)值,本篇文章將詳細(xì)講解電源抑制比(PSRR)及如何測量它。

2022-08-30 17:09:25 14841

14841

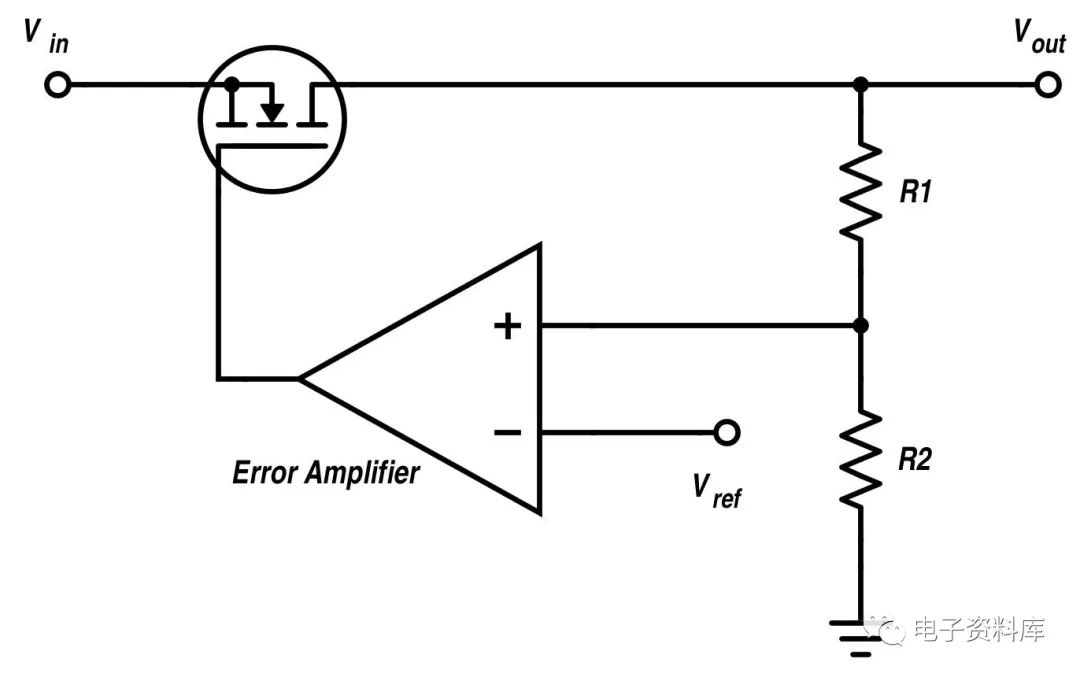

在本文中,我們將介紹噪聲和電源抑制比 (PSRR) 在低壓差 (LDO) 穩(wěn)壓器中的影響。讓我們簡要討論一下什么是 LDO。

2023-09-26 14:29:43 2236

2236

在本文中,我們將介紹低壓差 (LDO) 穩(wěn)壓器中噪聲和電源抑制比 (PSRR) 的影響。讓我們簡單討論一下什么是 LDO。

2024-03-15 17:12:08 638

638

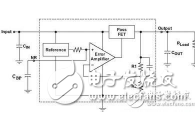

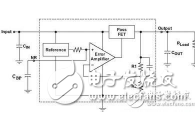

器件擁有非常好的電源紋波抑制 (PSRR) 性能,其為高性能 LDO 的另一個(gè)關(guān)鍵性能參數(shù)。為了滿足這種矛盾的要求,IC 廠商選擇使用寬帶寬誤差放大器,以實(shí)現(xiàn)最佳低噪聲 PSRR.如果低噪聲也為強(qiáng)制要求

2018-11-29 17:02:59

的影響。對于高性能的時(shí)鐘和射頻頻綜產(chǎn)品,為了獲得極低的相噪性能,往往采用低噪聲的 LDO 供電。然而,采用不同的 LDO 給頻綜供電,取得的相噪性能往往會有很大差別,同時(shí),LDO 外圍電路設(shè)計(jì)也會影響到頻綜的相噪性能。

2019-08-21 08:04:28

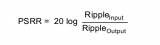

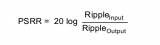

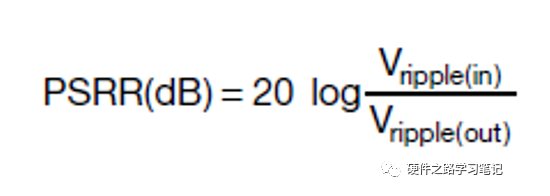

作者:Hao Wang深圳模擬工程師PSRR是什么PSRR(Power supply rejection ratio)又稱電源抑制比,是衡量電路對于輸入電源中紋波抑制大小的重要參數(shù),表示為輸出紋波

2019-03-20 06:45:01

如圖,請問下LDO的紋波抑制比是否可以這樣測試,測試的LDO為3.3V輸出,規(guī)格書紋波抑制比40dB但實(shí)際上計(jì)算數(shù)差很多

2021-11-20 09:50:15

的設(shè)計(jì)和功率分配。同樣,在系統(tǒng)設(shè)計(jì)中,也要從節(jié)省電池能量的角度出發(fā)多加考慮。帶有使能控制的低壓差線性穩(wěn)壓器(LDO)是不錯的選擇。

2019-07-05 06:22:55

1kHz的頻率下電源抑制比(PSRR)高達(dá)73dB,它能夠?yàn)橹T如射頻(RF)接收器和發(fā)送器、壓控振蕩器(VCO)和音頻放大器等對噪聲敏感的模擬電路的供電提供低噪聲、電源紋波抑制比(PSRR)和快速瞬態(tài)響應(yīng)

2019-07-25 06:15:03

現(xiàn)在正做一個(gè)折疊式共源共柵放大器的設(shè)計(jì),性能指標(biāo)增益和電源抑制比不能同時(shí)達(dá)到要求,各位大神幫忙告訴我怎么提高電源抑制比?另外,抑制電路到底是什么啊?最好有圖呈現(xiàn),謝謝了!

2016-05-27 13:52:28

電源抑制比電源抑制比(Power Supply Rejection Ratio):把電源的輸入與輸出看作獨(dú)立的信號源,輸入與輸出的紋波比值即是PSRR,通常用對數(shù)形式表示,單位是dB。 PSRR=20log{[ripple(in)/...

2021-12-31 07:03:52

1. 高的噪音和紋波抑制;2. 占用PCB板面積小,如手機(jī)等手持電子產(chǎn)品;3. 電路電源不允許使用電感器,如手機(jī);4. 電源需要具有瞬時(shí)校準(zhǔn)和輸出狀態(tài)自檢功能;5. 要求穩(wěn)壓器低壓降,自身功耗低;6. 要求線路成本低和方案簡單;此時(shí),選用LDO是最恰當(dāng)?shù)?b class="flag-6" style="color: red">選擇,同時(shí)滿足產(chǎn)品設(shè)計(jì)的各種要求。二、再

2021-11-17 07:07:52

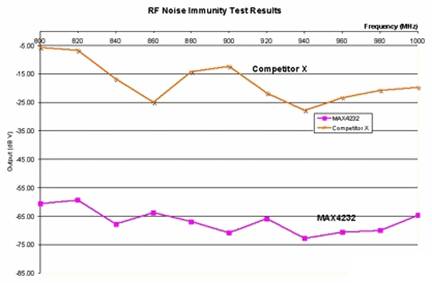

設(shè)計(jì)中可以看出每個(gè)回路長度相當(dāng)即高頻電流會均勻分配到每個(gè)電容中。 圖1電源PCB走線優(yōu)化 如果PCB是多層板,可以選擇和主電流回路層最近一層覆地,覆地可以有效的解決噪聲問題,注意,盡量保證覆地的完整性

2018-11-21 15:57:51

,改進(jìn)設(shè)計(jì)中可以看出每個(gè)回路長度相當(dāng)即高頻電流會均勻分配到每個(gè)電容中。圖1 電源PCB走線優(yōu)化如果PCB是多層板,可以選擇和主電流回路層最近一層覆地,覆地可以有效的解決噪聲問題,注意,盡量保證覆

2019-03-27 17:10:04

選擇一款LDO,要關(guān)注以下指標(biāo):Vin(min)Vin(max)VoutIout靜態(tài)電流最小電壓差耗散功率電源抑制比Vin(min)需要考慮輸入電壓是否能驅(qū)動LDO內(nèi)部調(diào)整管。Vin(min

2021-11-16 08:43:51

到目前為止,在這個(gè)博客系列中,我們已經(jīng)研究了ADC的電源抑制比(PSRR)和先前功率級的PSRR要求,以確保最小的噪聲。在進(jìn)一步分析電源之前,我們需要了解電源噪聲對ADC的影響。在本博客中,我們將

2018-07-24 17:25:11

我們看到PCB設(shè)計(jì)中還是很多用到LDO電源的,說明它肯定有自身的優(yōu)勢。其中,它最大的一個(gè)優(yōu)勢很多網(wǎng)友也提到了,就是紋波小。本文就展開講講它們紋波的情況。紋波小是我們通常的說法,其實(shí)衡量電源,尤其是LDO

2018-09-21 11:55:39

內(nèi)部噪聲)。外部噪聲是由外界影響(輸入處的紋波――實(shí)際源)產(chǎn)生的各種噪聲。輸入波紋與電源抑制比(PSRR)有關(guān)。此外,還有如熱和閃爍等噪聲的不同類別。熱噪聲是由粒子的隨機(jī)熱運(yùn)動引起的,這種運(yùn)動稱為擴(kuò)散

2020-10-27 07:29:38

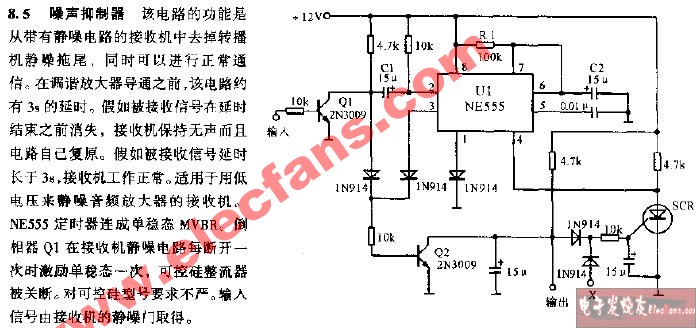

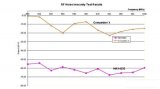

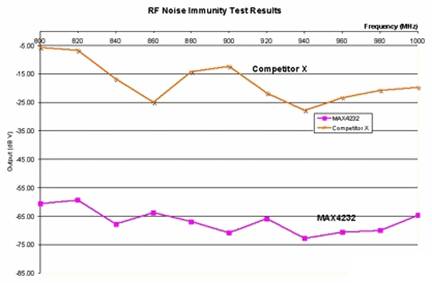

本文描述了一種通用的集成電路RF噪聲抑制能力測量技術(shù)。RF抑制能力測試將電路板置于可控制的RF信號電平下,該RF電平代表電路工作時(shí)可能受到的干擾強(qiáng)度。這樣就產(chǎn)生了一個(gè)標(biāo)準(zhǔn)化、結(jié)構(gòu)化的測試方法

2019-07-04 06:21:39

要的聽得見的“嗡嗡”聲。由此可見,RF抑制能力較差的電路會對蜂窩電話的RF信號解調(diào),并會產(chǎn)生不希望聽到的低頻噪音。為了測量產(chǎn)品的質(zhì)量,測試時(shí)需要把電路放在RF環(huán)境中測量,該RF環(huán)境要與正常操作時(shí)電路遇到的環(huán)境相當(dāng)。

2019-06-03 06:07:07

在我們之前的博客中,我們談到《低壓降(LDO)穩(wěn)壓器之理想與現(xiàn)實(shí)》,介紹了什么是LDO穩(wěn)壓器及其噪聲參數(shù)的基本信息。今天,我們將進(jìn)一步詳細(xì)談?wù)勈裁词?b class="flag-6" style="color: red">LDO噪聲?LDO噪聲是如何分類的?

2019-08-01 07:20:41

內(nèi)部噪聲)。外部噪聲是由外界影響(輸入處的紋波——實(shí)際源)產(chǎn)生的各種噪聲。輸入波紋與電源抑制比(PSRR)有關(guān)。此外,還有如熱和閃爍等噪聲的不同類別。熱噪聲是由粒子的隨機(jī)熱運(yùn)動引起的,這種運(yùn)動稱為擴(kuò)散

2018-10-30 09:04:53

什么是集成電路RF噪聲抑制能力測量技術(shù)?

2019-08-02 08:07:40

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運(yùn)放性能的重要指標(biāo),關(guān)于他們的具體仿真

2021-12-27 07:24:51

讀論文analysis of switched-capacitor commom-mode feedback circuit1.與單端輸出相比,全差分電路有更好的共模抑制比和電源抑制比。2.共模環(huán)路

2021-10-29 07:10:25

近期,項(xiàng)目遇到的問題,不得不考慮ldo的紋波抑制比問題,在選型時(shí),確實(shí)沒有仔細(xì)研究,咨詢所選電源芯片的廠家后,才得知,自己選的這個(gè)芯片,紋波抑制不是很好。具體什么是紋波抑制比,腦子里倒是有,還是準(zhǔn)確

2021-07-30 06:38:39

要的聽得見的“嗡嗡”聲。由此可見,RF抑制能力較差的電路會對蜂窩電話的RF信號解調(diào),并會產(chǎn)生不希望聽到的低頻噪音。為了測量產(chǎn)品的質(zhì)量,測試時(shí)需要把電路放在RF環(huán)境中測量,該RF環(huán)境要與正常操作時(shí)電路遇到的環(huán)境相當(dāng)。

2019-05-30 08:04:46

噪聲航天級 LDO 的 PSRR電源抑制比 (PSRR) 用于衡量 LDO 清除或抑制由上游其他元件傳入噪聲的能力。對于高端 ADC,為了更大限度地減少位錯誤,輸入電源噪聲要求不斷提高。鑒于控制環(huán)路

2022-11-03 08:23:55

1 kHz 的頻率下電源抑制比(PSRR)高達(dá)73dB,它能夠?yàn)橹T如射頻(RF)接收器和發(fā)送器、壓控振蕩器(VCO)和音頻放大器等對噪聲敏感的模擬電路的供電提供低噪聲、電源紋波抑制比(PSRR)和快速

2019-06-19 06:43:54

/DC,因?yàn)槠湫矢撸?b class="flag-6" style="color: red">LDO會因?yàn)閴航荡蠖陨頁p耗很大部分效率; 如果壓降比較小,選擇LDO,因?yàn)槠?b class="flag-6" style="color: red">噪聲低,電源干凈,而且外圍電路簡單,成本低。 LDO是low dropout

2018-11-30 17:24:24

部分效率;如果壓降比較小,選擇LDO,因?yàn)槠?b class="flag-6" style="color: red">噪聲低,電源干凈,而且外圍電路簡單,成本低。LDO是low dropout regulator,意為低壓差線性穩(wěn)壓器,是相對于傳統(tǒng)的線性穩(wěn)壓器來說的。傳統(tǒng)的線性

2017-02-22 11:48:00

。此紋波電壓一般沒有固定的頻率。閉環(huán)調(diào)節(jié)控制引起的紋波噪聲閉環(huán)調(diào)節(jié)控制引起的紋波噪聲的抑制 在開關(guān)直流電源中,往往因調(diào)節(jié)器參數(shù)選擇不適當(dāng)會引起輸出紋波的增大,這部分紋波可通過以下方法進(jìn)行抑制。a、在

2022-05-01 16:31:12

如何抑制電子電路中噪聲的產(chǎn)生低噪聲前置放大器電路的設(shè)計(jì)方法元件選擇原則PDA麥克風(fēng)前置放大器電路

2021-02-25 07:06:39

電源波紋抑止比 (PSRR)、噪聲與封裝大小通常是為便攜式應(yīng)用決定最佳 LDO 選擇的要素。

2021-03-25 07:20:44

接地電流或靜態(tài)電流 (IGND 或 IQ)、電源波紋抑止比 (PSRR)、噪聲與封裝大小通常是為便攜式應(yīng)用決定最佳LDO選擇的要素。在選擇低壓降線性調(diào)節(jié)器(LDO) 時(shí),需要考慮的基本問題包括

2021-01-28 17:09:01

電源線不要和信號線捆扎在一起。

小結(jié)

在運(yùn)放電路設(shè)計(jì)中降低電源噪聲的主要措施包括:

通過去耦、濾波等措施降低電源輸出的紋波和噪聲成分。

改善設(shè)計(jì),提高電源電壓調(diào)整率。

合理電路結(jié)構(gòu)、考究的PCB布線、合理的走線工藝。

選擇在敏感噪聲頻段的PSRR或CMRR較高的器件。

2023-11-21 06:27:27

中,100Hz紋波是主要的電源噪聲,對于運(yùn)放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內(nèi),這取決于三個(gè)因素:運(yùn)放在100Hz時(shí)的電源抑制比(PSRR),穩(wěn)壓器的紋波抑制比及

2017-10-19 23:34:27

源 電源紋波在全波整流的線性穩(wěn)壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運(yùn)放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內(nèi),這取決于三個(gè)

2018-12-29 10:10:32

同的設(shè)計(jì)需要單獨(dú)進(jìn)行電源評估。例如,ADRF6820VCO 電源上的集成LDO 比不采用集成LDO 的PLL 電源具有更強(qiáng)的噪聲抑制能力。ADRF6820 電源域和功耗ADRF6820 電源域和功耗

2019-10-17 09:06:34

、靜態(tài)電流、接地電流、關(guān)斷電流、效率、直流輸入電壓和負(fù)載調(diào)整率、輸入電壓和負(fù)載瞬態(tài)響應(yīng)、電源抑制比(PSRR)、輸出噪聲和精度。同時(shí),為了方便理解,文中采用了示例和插圖。設(shè)計(jì)過程中通常到后期才會進(jìn)行LDO 選型,并且很少進(jìn)行分析。本文所述的概念將使設(shè)計(jì)人員能夠根據(jù)系統(tǒng)要求挑選最佳的LDO。壓差壓差(

2021-11-15 07:38:55

能力的LDO的電源抑制比在100KHz以上都不太好開關(guān)電源如果選用類似LM2596這樣的芯片,看到紋波輸出大概在150KHz以上,求大神指點(diǎn)迷津,開關(guān)電源的紋波和噪聲可以抑制到什么程度呢?可不可以不用開關(guān)電源,直接用LDO來抑制適配器的噪聲呢?開關(guān)電源芯片有沒有開關(guān)頻率比較低的呢?

2014-04-22 22:30:52

的自激振蕩,引起附加紋波。此紋波電壓一般沒有固定的頻率。(閉環(huán)調(diào)節(jié)控制引起的紋波噪聲)10閉環(huán)調(diào)節(jié)控制引起的紋波噪聲的抑制在開關(guān)直流電源中,往往因調(diào)節(jié)器參數(shù)選擇不適當(dāng)會引起輸出紋波的增大,這部分紋波可通過以下

2021-02-17 07:00:00

什么是紋波抑制比PSRR?如何確定應(yīng)用的紋波抑制比PSRR呢?怎樣去測量LDO芯片的紋波抑制比PSRR呢?

2021-11-03 06:48:15

扁平線共模電感對CE噪聲的高效抑制?|深圳比創(chuàng)達(dá)電子EMC(中)扁平線共模電感對CE噪聲的高效抑制(中)?相信不少人是有疑問的,今天深圳市比創(chuàng)達(dá)電子科技有限公司就跟大家解答一下!

比創(chuàng)達(dá)整改實(shí)例

2024-02-28 10:26:20

選擇好的前端濾波器以加強(qiáng)帶外抑制。關(guān)于如何解決RF的電源干擾以及如何選用RF的LDO,首先必須確定RF電源已經(jīng)被很好地濾波,其次有必要的話最好是不同的RF線路使用獨(dú)立的電源。在選用RF的LDO時(shí)要注意考慮它的驅(qū)動電流、輸出噪聲及紋波抑制等特性。

2019-07-08 08:26:47

的頻率噪聲(F1)會對RF信號質(zhì)量產(chǎn)生影響。低頻帶噪聲是DC-DC轉(zhuǎn)換器的開關(guān)發(fā)出噪聲(一般的PA用的DC/DC轉(zhuǎn)換器的開關(guān)頻率為2~10MHz)的主要原因。因此,PA的電源線的對策中,必須要抑制DC

2018-10-10 16:50:20

具有良好電源抑制比(PSRR)的ADC。當(dāng)然,使您的系統(tǒng)性能免受其電源影響的最佳方法是選擇具有足夠PSRR的ADC來開始工作。如果您所選擇的ADC不能完全滿足您的PSRR需求,那么您可在自己原來

2022-11-18 07:31:30

為 400KHz 的噪聲,折算到輸出端是幅值為 4mV 頻率為 400KHz 噪聲。圖 2.62 ADA4077 電源抑制比評估電路所以在開關(guān)電源供電精密電路中,依靠放大器自身提高電源抑制比的方式十分

2020-11-24 09:20:54

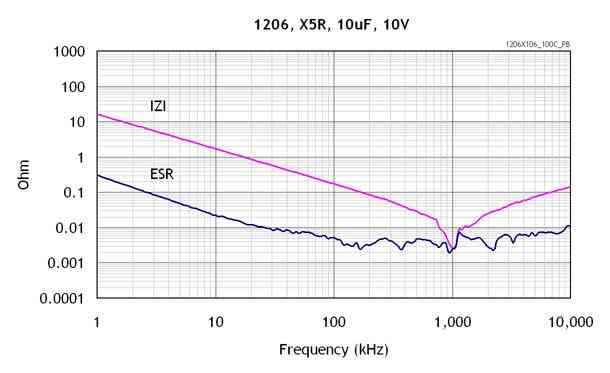

電源或共模電壓變化產(chǎn)生的失調(diào)偏移時(shí)很容易產(chǎn)生困惑。這種困惑的根本原因如下圖所示:圖 1:儀表放大器的典型電源抑制比曲線在圖 1 中,放大器的電源抑制比 (PSRR) 隨放大器增益配置的升高而增加。這樣很

2018-09-19 11:00:26

Vo 到Vmax, 輸出電壓最大值和最小值之差g.電源抑制比(Power Supply Rejection Ratio. PSRR)LDO 的輸入源往往許多干擾信號存在。PSRR 反映了LDO 對于這些

2019-09-17 09:05:03

GSM手機(jī)的隨處可見正導(dǎo)致不需要的RF信號的持續(xù)增加,如果電子電路沒有足夠的RF抑制能力,這些RF信號會導(dǎo)致電路產(chǎn)生的結(jié)果失真。為了確保電子電路可靠工作,對于電子電路RF抑制能力的測量已經(jīng)成為

2019-07-31 06:26:15

處理不當(dāng),開關(guān)電源本身就會變成一個(gè)干擾源。LDO有較高的電源抑制比,且LDO是低噪聲器件,因此應(yīng)用LDO可以有效地濾除開關(guān)電源EMI,減小紋波輸出。 4.為開關(guān)電源提供過流保護(hù) 盡管許多PWM控制芯片本身具有過流保護(hù)功能,但LDO的過流保護(hù)功能可以提升開關(guān)電源的安全系數(shù)。`

2019-03-07 11:25:13

的噪聲和漣漪,防止它們對LDO的工作造成影響。在輸入電容和LDO之間,形成了一個(gè)低通濾波器,能夠?yàn)V除輸入電源中的高頻噪聲和漣漪。當(dāng)輸入電容越大時(shí),它對電源的過濾效果就越好,能夠提高LDO的穩(wěn)定性和噪聲抑制

2023-03-11 18:04:26

削弱了穩(wěn)壓器的噪聲抑制能力,不適合為敏感電路模塊供電。 為了保持良好的調(diào)節(jié)和噪聲抑制能力,LDO必須使用比它們輸入輸出電壓差規(guī)范中規(guī)定的更高的輸入電壓供電,這降低了轉(zhuǎn)換效率。為滿足輸入輸出電壓差

2018-09-26 14:33:58

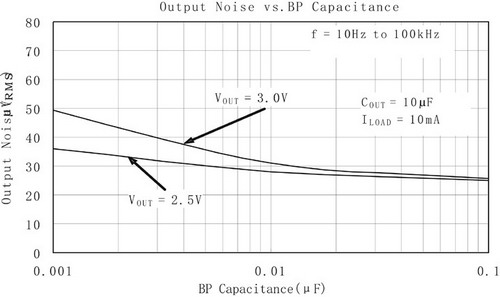

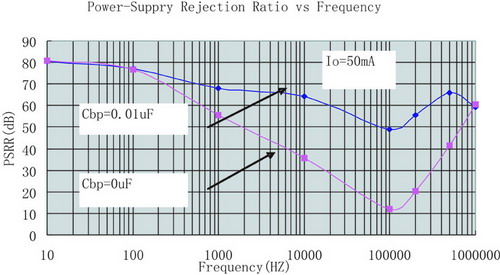

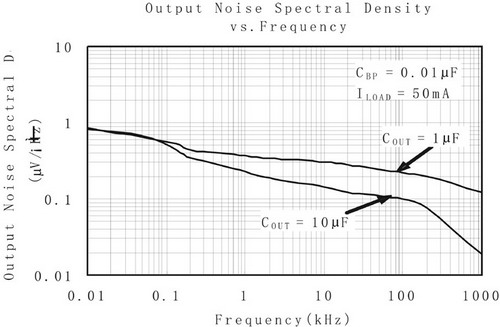

LDO穩(wěn)壓器的PSRR和輸出噪聲在RF電路中的選擇:LDO是一種微功耗的低壓差線性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比(PSRR)。SGM2007高性能低壓差線性穩(wěn)壓器在10Hz至100kHz頻率

2009-09-25 08:19:27 19

19

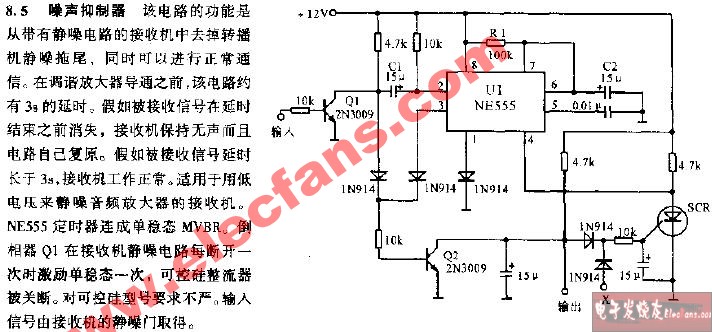

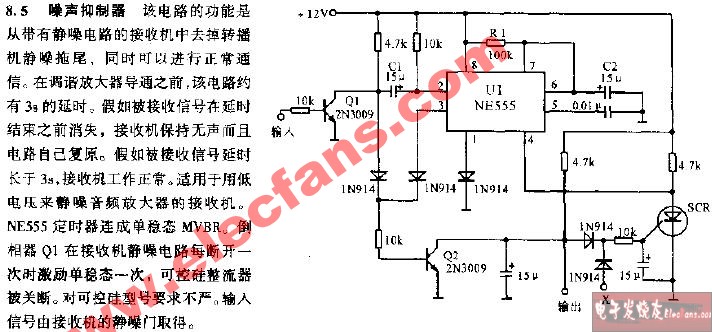

噪聲抑制器電路

2009-03-29 16:54:20 536

536

噪聲抑制器電路

2009-03-30 20:17:08 1021

1021

利用電波暗室測試電路的RF噪聲抑制

GSM手機(jī)的隨處可見正導(dǎo)致不需要的RF信號的持續(xù)增加,如果電子電路沒有足夠的RF抑制能力,這些RF信號會導(dǎo)致電路產(chǎn)生的結(jié)果失真。為

2010-04-13 10:17:19 893

893

LDO是一種微功耗的低壓差線性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比(

2010-11-11 17:35:42 1917

1917

本文描述了一種通用的集成電路RF噪聲抑制能力測量技術(shù)。RF抑制能力測試將電路板置于可控制的RF信號電平下,該RF電平代表電路工作時(shí)可能受到的干擾強(qiáng)度。

2012-01-16 09:37:54 1568

1568

便攜產(chǎn)品電源設(shè)計(jì)需要系統(tǒng)級思維,在開發(fā)由電池供電的設(shè)備時(shí),諸如手機(jī)、MP3、PDA、PMP、DSC等低功耗產(chǎn)品,如果電源系統(tǒng)設(shè)計(jì)不合理,將影響到整個(gè)系統(tǒng)的架構(gòu)、產(chǎn)品的特性組合、元件的選擇、軟件

2017-11-25 09:56:40 1457

1457

GSM手機(jī)的隨處可見正導(dǎo)致不需要的RF信號的持續(xù)增加,如果電子電路沒有足夠的RF抑制能力,這些RF信號會導(dǎo)致電路產(chǎn)生的結(jié)果失真。為了確保電子電路可靠工作,對于電子電路RF抑制能力的測量已經(jīng)成為

2017-12-05 15:11:01 359

359

模塊對外部電源進(jìn)行處理,得到模塊所需性能標(biāo)準(zhǔn)的電壓。 設(shè)計(jì)了一種可用于射頻前端芯片供電的高電源抑制比(PSR)無片外電容CMOS低壓差線性穩(wěn)壓器(LDO)。基于對全頻段電源抑制比的詳細(xì)分析,提出了一種PSR增強(qiáng)電路模塊,使100

2018-02-23 11:41:48 0

0 LT3094演示電路-超低噪聲、超高電源抑制比負(fù)LDO穩(wěn)壓器(-20V至-3.3V@500 mA)

2021-03-23 14:27:09 14

14 ADM7155:600 mA,超低噪聲,高電源抑制比,RF線性穩(wěn)壓器數(shù)據(jù)表

2021-04-19 19:48:03 3

3 ADM7154:600 mA,超低噪聲,高電源抑制比,RF線性穩(wěn)壓器數(shù)據(jù)表

2021-04-19 20:05:36 0

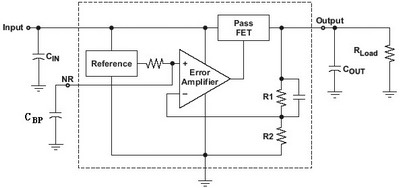

0 和 PSRR 低壓差線性穩(wěn)壓器 (LDO) 為調(diào)節(jié)由較高電壓輸入產(chǎn)生的輸出電壓提供了一種簡單方法。雖然操作簡單,但其自生噪聲在很多時(shí)候易與電源抑制比 (PSRR) 混淆。這兩者在很多情況下統(tǒng)稱為“噪聲”,這是不恰當(dāng)?shù)摹?b class="flag-6" style="color: red">噪聲是由LDO 內(nèi)部電路中的晶體管和電阻器以及外部元件產(chǎn)生

2021-05-13 15:35:18 3424

3424

ADM7172:6.5 V,2 A,超低噪聲,高電源抑制比,快速瞬態(tài)響應(yīng)CMOS LDO數(shù)據(jù)表

2021-05-14 17:01:48 6

6 ADP7156:1.2 A,超低噪聲,高電源抑制比,RF線性穩(wěn)壓器數(shù)據(jù)表

2021-05-17 16:32:35 3

3 ADP7157:1.2 A,超低噪聲,高電源抑制比,RF線性穩(wěn)壓器數(shù)據(jù)表

2021-05-17 16:58:49 0

0 ADP7158:2 A,超低噪聲,高電源抑制比,RF線性穩(wěn)壓器數(shù)據(jù)表

2021-05-17 18:01:40 1

1 ADM7170:6.5 V,500 mA,超低噪聲,高電源抑制比,快速瞬態(tài)響應(yīng)CMOS LDO數(shù)據(jù)表

2021-05-21 19:19:34 7

7 ADM7171:6.5 V,1 A,超低噪聲,高電源抑制比,快速瞬態(tài)響應(yīng)CMOS LDO數(shù)據(jù)表

2021-05-21 19:33:05 12

12 LT3045演示電路-低噪聲、高電源抑制比RF線性穩(wěn)壓器(3.8-20V至3.3V@500 mA)

2021-06-02 16:16:21 26

26 LT3042演示電路-低噪聲、高電源抑制比RF線性穩(wěn)壓器(3.8-20V至3.3V@200 mA)

2021-06-03 10:50:23 2

2 大的情況下,選擇DC/DC,因?yàn)槠湫矢撸?b class="flag-6" style="color: red">LDO會因?yàn)閴航荡蠖陨頁p耗很大部分效率;如果壓降比較小,選擇LDO,因?yàn)槠?b class="flag-6" style="color: red">噪聲低,電源干凈,而且外圍電路簡單,成本低。LDO是low dropout...

2021-11-09 16:51:01 18

18 LDO基礎(chǔ)知識:電源抑制比

2022-11-01 08:26:41 2

2 在便攜式通信中,低壓差線性穩(wěn)壓器(LDO)為RF電路產(chǎn)生電源電壓;為頻率合成器和壓控振蕩器(VCO)供電時(shí),這些電壓必須特別干凈。為穩(wěn)壓器供電的電源通常包括疊加在直流上的寬帶交流紋波。預(yù)計(jì)LDO會抑制這些偽影。本文介紹了三種提高LDO電源抑制比(PSRR)的方法。

2023-03-13 09:32:37 980

980

低壓差線性穩(wěn)壓器(LDO)最大的優(yōu)點(diǎn)之一是它們能夠衰減開關(guān)模式電源產(chǎn)生的電壓紋波。這對鎖相環(huán)(PLL)和時(shí)鐘等信號調(diào)節(jié)器件在內(nèi)的數(shù)據(jù)轉(zhuǎn)換器尤為重要,因?yàn)?b class="flag-6" style="color: red">噪聲電源電壓會影響性能。電源抑制比(PSRR)仍然通常被誤認(rèn)為單一的靜態(tài)值。在這篇文章中,我將嘗試說明什么是PSRR以及影響它的變量有哪些。

2023-04-04 10:25:33 1247

1247

LDO的電源抑制比基本概念與應(yīng)用

2023-07-24 16:15:14 1271

1271

LDO噪聲源與降低噪聲方式

2023-07-25 08:56:49 1330

1330

電源抑制比是什么意思?電源抑制比怎么提高? 一、電源抑制比的概念 電源抑制比(PSRR)又稱電源噪聲抑制比,是指在電路中,當(dāng)電源發(fā)生噪聲時(shí),電路輸出端對電源噪聲的抑制程度,一般使用分貝(dB)單位

2023-09-02 17:50:32 3365

3365 五種紋波噪聲。這種噪聲會對電路穩(wěn)定性、噪聲抑制、射頻干擾等方面產(chǎn)生很大影響,因此必須加以抑制。本文將介紹開關(guān)電源的五種紋波噪聲以及抑制的方法。 一、電源線傳輸噪聲 電源線傳輸噪聲是指開關(guān)電源輸出時(shí)通過電路中的電源線

2023-11-06 10:13:22 548

548 電子發(fā)燒友網(wǎng)站提供《超低噪聲、高電源抑制比 (PSRR)、快速、射頻 (RF)、1A 低壓差線性穩(wěn)壓器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-02-28 15:14:45 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論