如果是三次諧波大,二次諧波小,可能因?yàn)?a target="_blank">信號(hào)占空比為50%,因?yàn)檫@種情況下,信號(hào)沒有偶次諧波。這時(shí)需要修改一下信號(hào)占空比。

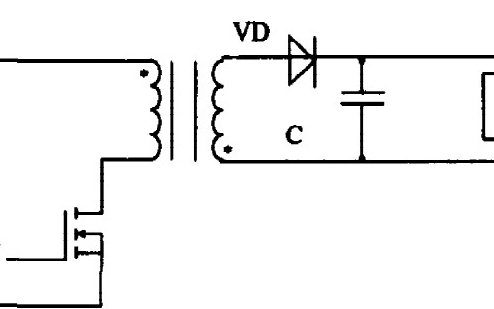

此外,對(duì)于如果是單向的時(shí)鐘信號(hào),一般采用源端串聯(lián)匹配。這樣可以抑制二次反射,但不會(huì)影響時(shí)鐘沿速率。源端匹配值,可以采用下圖公式得到。

此主題相關(guān)圖片如下:

39、什么是走線的拓?fù)浼軜?gòu)?

Topology,有的也叫routing order.對(duì)于多端口連接的網(wǎng)絡(luò)的布線次序。

40、怎樣調(diào)整走線的拓?fù)浼軜?gòu)來提高信號(hào)的完整性?

這種網(wǎng)絡(luò)信號(hào)方向比較復(fù)雜,因?yàn)閷?duì)單向,雙向信號(hào),不同電平種類信號(hào),拓樸影響都不一樣,很難說哪種拓樸對(duì)信號(hào)質(zhì)量有利。而且作前仿真時(shí),采用何種拓樸對(duì)工程師要求很高,要求對(duì)電路原理,信號(hào)類型,甚至布線難度等都要了解。

41、怎樣通過安排迭層來減少EMI問題?

首先,EMI要從系統(tǒng)考慮,單憑PCB無法解決問題。

層疊對(duì)EMI來講,我認(rèn)為主要是提供信號(hào)最短回流路徑,減小耦合面積,抑制差模干擾。另外地層與電源層緊耦合,適當(dāng)比電源層外延,對(duì)抑制共模干擾有好處。

42、為何要鋪銅?

一般鋪銅有幾個(gè)方面原因。

1,EMC.對(duì)于大面積的地或電源鋪銅,會(huì)起到屏蔽作用,有些特殊地,如PGND起到防護(hù)作用。

2,PCB工藝要求。一般為了保證電鍍效果,或者層壓不變形,對(duì)于布線較少的PCB板層鋪銅。

3,信號(hào)完整性要求,給高頻數(shù)字信號(hào)一個(gè)完整的回流路徑,并減少直流網(wǎng)絡(luò)的布線。當(dāng)然還有散熱,特殊器件安裝要求鋪銅等等原因。

43、在一個(gè)系統(tǒng)中,包含了dsp和pld,請(qǐng)問布線時(shí)要注意哪些問題呢?

看你的信號(hào)速率和布線長(zhǎng)度的比值。如果信號(hào)在傳輸線上的時(shí)延和信號(hào)變化沿時(shí)間可比的話,就要考慮信號(hào)完整性問題。另外對(duì)于多個(gè)DSP,時(shí)鐘,數(shù)據(jù)信號(hào)走線拓普也會(huì)影響信號(hào)質(zhì)量和時(shí)序,需要關(guān)注。

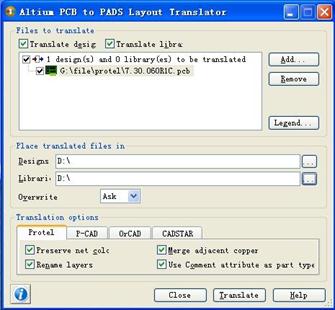

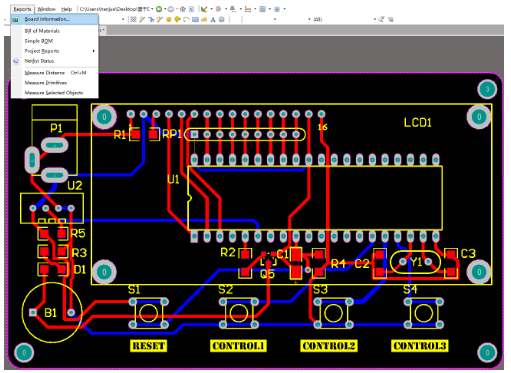

44、除protel工具布線外,還有其他好的工具嗎?

至于工具,除了PROTEL,還有很多布線工具,如MENTOR的WG2000,EN2000系列和powerpcb,Cadence的allegro,zuken的cadstar,cr5000等,各有所長(zhǎng)。

45、什么是“信號(hào)回流路徑”?

信號(hào)回流路徑,即return current。高速數(shù)字信號(hào)在傳輸時(shí),信號(hào)的流向是從驅(qū)動(dòng)器沿PCB傳輸線到負(fù)載,再由負(fù)載沿著地或電源通過最短路徑返回驅(qū)動(dòng)器端。這個(gè)在地或電源上的返回信號(hào)就稱信號(hào)回流路徑。Dr.Johson在他的書中解釋,高頻信號(hào)傳輸,實(shí)際上是對(duì)傳輸線與直流層之間包夾的介質(zhì)電容充電的過程。SI分析的就是這個(gè)圍場(chǎng)的電磁特性,以及他們之間的耦合。

46、如何對(duì)接插件進(jìn)行SI分析?

在IBIS3.2規(guī)范中,有關(guān)于接插件模型的描述。一般使用EBD模型。如果是特殊板,如背板,需要SPICE模型。也可以使用多板仿真軟件(HYPERLYNX或IS_multiboard),建立多板系統(tǒng)時(shí),輸入接插件的分布參數(shù),一般從接插件手冊(cè)中得到。當(dāng)然這種方式會(huì)不夠精確,但只要在可接受范圍內(nèi)即可。

47、請(qǐng)問端接的方式有哪些?

端接(terminal),也稱匹配。一般按照匹配位置分有源端匹配和終端匹配。其中源端匹配一般為電阻串聯(lián)匹配,終端匹配一般為并聯(lián)匹配,方式比較多,有電阻上拉,電阻下拉,戴維南匹配,AC匹配,肖特基二極管匹配。

48、采用端接(匹配)的方式是由什么因素決定的?

匹配采用方式一般由BUFFER特性,拓普情況,電平種類和判決方式來決定,也要考慮信號(hào)占空比,系統(tǒng)功耗等。

49、采用端接(匹配)的方式有什么規(guī)則?

數(shù)字電路最關(guān)鍵的是時(shí)序問題,加匹配的目的是改善信號(hào)質(zhì)量,在判決時(shí)刻得到可以確定的信號(hào)。對(duì)于電平有效信號(hào),在保證建立、保持時(shí)間的前提下,信號(hào)質(zhì)量穩(wěn)定;對(duì)延有效信號(hào),在保證信號(hào)延單調(diào)性前提下,信號(hào)變化延速度滿足要求。Mentor ICX產(chǎn)品教材中有關(guān)于匹配的一些資料。另外《High Speed Digital design a hand book of blackmagic》有一章專門對(duì)terminal的講述,從電磁波原理上講述匹配對(duì)信號(hào)完整性的作用,可供參考。

50、能否利用器件的IBIS模型對(duì)器件的邏輯功能進(jìn)行仿真?如果不能,那么如何進(jìn)行電路的板級(jí)和系統(tǒng)級(jí)仿真?

IBIS模型是行為級(jí)模型,不能用于功能仿真。功能仿真,需要用SPICE模型,或者其他結(jié)構(gòu)級(jí)模型。

51、在數(shù)字和模擬并存的系統(tǒng)中,有2種處理方法,一個(gè)是數(shù)字地和模擬地分開,比如在地層,數(shù)字地是獨(dú)立地一塊,模擬地獨(dú)立一塊,單點(diǎn)用銅皮或FB磁珠連接,而電源不分開;另一種是模擬電源和數(shù)字電源分開用FB連接,而地是統(tǒng)一地地。請(qǐng)問李先生,這兩種方法效果是否一樣?

應(yīng)該說從原理上講是一樣的。因?yàn)殡娫春偷貙?duì)高頻信號(hào)是等效的。

區(qū)分模擬和數(shù)字部分的目的是為了抗干擾,主要是數(shù)字電路對(duì)模擬電路的干擾。但是,分割可能造成信號(hào)回流路徑不完整,影響數(shù)字信號(hào)的信號(hào)質(zhì)量,影響系統(tǒng)EMC質(zhì)量。因此,無論分割哪個(gè)平面,要看這樣作,信號(hào)回流路徑是否被增大,回流信號(hào)對(duì)正常工作信號(hào)干擾有多大。

現(xiàn)在也有一些混合設(shè)計(jì),不分電源和地,在布局時(shí),按照數(shù)字部分、模擬部分分開布局布線,避免出現(xiàn)跨區(qū)信號(hào)。

52、安規(guī)問題:FCC、EMC的具體含義是什么?

FCC: federal communication commission 美國通信委員會(huì)

EMC: electro megnetic compatibility 電磁兼容

FCC是個(gè)標(biāo)準(zhǔn)組織,EMC是一個(gè)標(biāo)準(zhǔn)。標(biāo)準(zhǔn)頒布都有相應(yīng)的原因,標(biāo)準(zhǔn)和測(cè)試方法。

53、何謂差分布線?

差分信號(hào),有些也稱差動(dòng)信號(hào),用兩根完全一樣,極性相反的信號(hào)傳輸一路數(shù)據(jù),依*兩根信號(hào)電平差進(jìn)行判決。為了保證兩根信號(hào)完全一致,在布線時(shí)要保持并行,線寬、線間距保持不變。

54、PCB仿真軟件有哪些?

仿真的種類很多,高速數(shù)字電路信號(hào)完整性分析仿真分析(SI)常用軟件有icx,signalvision,hyperlynx,XTK,speectraquest等。有些也用Hspice。

55、PCB仿真軟件是如何進(jìn)行LAYOUT仿真的?

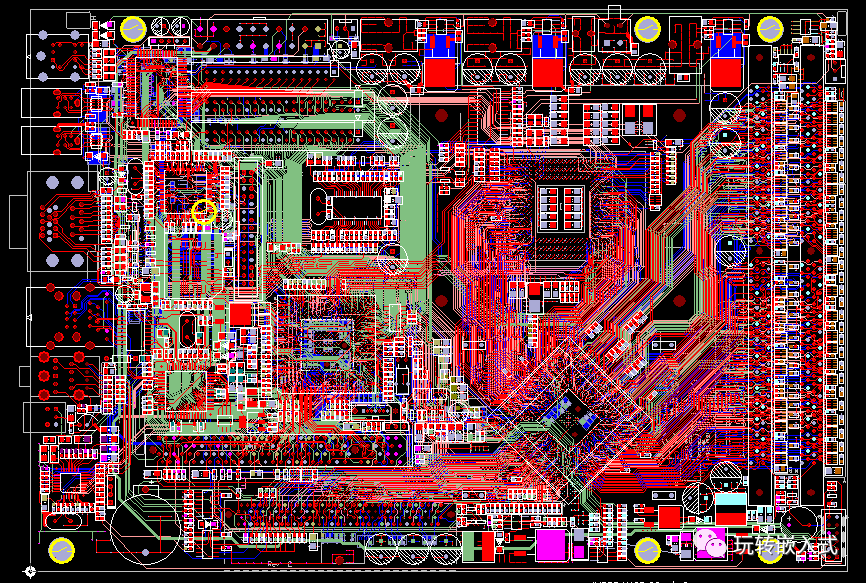

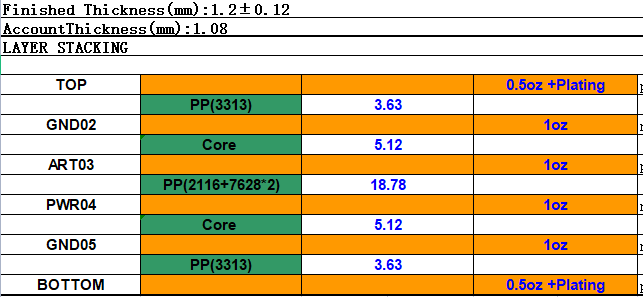

高速數(shù)字電路中,為了提高信號(hào)質(zhì)量,降低布線難度,一般采用多層板,分配專門的電源層,地層。

56、在布局、布線中如何處理才能保證50M以上信號(hào)的穩(wěn)定性

高速數(shù)字信號(hào)布線,關(guān)鍵是減小傳輸線對(duì)信號(hào)質(zhì)量的影響。因此,100M以上的高速信號(hào)布局時(shí)要求信號(hào)走線盡量短。

數(shù)字電路中,高速信號(hào)是用信號(hào)上升延時(shí)間來界定的。而且,不同種類的信號(hào)(如TTL,GTL,LVTTL),確保信號(hào)質(zhì)量的方法不一樣。

57、室外單元的射頻部分,中頻部分,乃至對(duì)室外單元進(jìn)行監(jiān)控的低頻電路部分往往采用部署在同一PCB上,請(qǐng)問對(duì)這樣的PCB在材質(zhì)上有何要求?如何防止射頻,中頻乃至低頻電路互相之間的干擾?

混合電路設(shè)計(jì)是一個(gè)很大的問題。很難有一個(gè)完美的解決方案。

一般射頻電路在系統(tǒng)中都作為一個(gè)獨(dú)立的單板進(jìn)行布局布線,甚至?xí)袑iT的屏蔽腔體。而且射頻電路一般為單面或雙面板,電路較為簡(jiǎn)單,所有這些都是為了減少對(duì)射頻電路分布參數(shù)的影響,提高射頻系統(tǒng)的一致性。相對(duì)于一般的FR4材質(zhì),射頻電路板傾向與采用高Q值的基材,這種材料的介電常數(shù)比較小,傳輸線分布電容較小,阻抗高,信號(hào)傳輸時(shí)延小。

在混合電路設(shè)計(jì)中,雖然射頻,數(shù)字電路做在同一塊PCB上,但一般都分成射頻電路區(qū)和數(shù)字電路區(qū),分別布局布線。之間用接地過孔帶和屏蔽盒屏蔽。

58、對(duì)于射頻部分,中頻部分和低頻電路部分部署在同一PCB上,mentor有什么解決方案?

Mentor的板級(jí)系統(tǒng)設(shè)計(jì)軟件,除了基本的電路設(shè)計(jì)功能外,還有專門的RF設(shè)計(jì)模塊。在RF原理圖設(shè)計(jì)模塊中,提供參數(shù)化的器件模型,并且提供和EESOFT等射頻電路分析仿真工具的雙向接口;在RF LAYOUT模塊中,提供專門用于射頻電路布局布線的圖案編輯功能,也有和EESOFT等射頻電路分析仿真工具的雙向接口,對(duì)于分析仿真后的結(jié)果可以反標(biāo)回原理圖和PCB。同時(shí),利用Mentor軟件的設(shè)計(jì)管理功能,可以方便的實(shí)現(xiàn)設(shè)計(jì)復(fù)用,設(shè)計(jì)派生,和協(xié)同設(shè)計(jì)。大大加速混合電路設(shè)計(jì)進(jìn)程。

手機(jī)板是典型的混合電路設(shè)計(jì),很多大型手機(jī)設(shè)計(jì)制造商都利用Mentor加安杰倫的eesoft作為設(shè)計(jì)平臺(tái)。

59、mentor的產(chǎn)品結(jié)構(gòu)如何?

Mentor Graphics的PCB工具有WG(原veribest)系列和Enterprise(boardstation)系列。詳細(xì)信息,請(qǐng)登錄http://www.mentor.com/。

- 圖文PC(6492)

相關(guān)推薦

Mentor Graphics的PCB設(shè)計(jì)復(fù)用方法

1770

1770

電磁干擾的PCB設(shè)計(jì)方法

842

842PCB設(shè)計(jì)高速模擬輸入信號(hào)走線方法及規(guī)則

8394

8394

PCB技術(shù)中的高速PCB設(shè)計(jì)中的屏蔽方法

789

789

PCB設(shè)計(jì)方法和技巧

855

855

PCB設(shè)計(jì)

PCB設(shè)計(jì)中EMI控制原理與實(shí)戰(zhàn)技巧

PCB設(shè)計(jì)中常見的問題

PCB設(shè)計(jì)中降低RF效應(yīng)的基本方法

PCB設(shè)計(jì)后期處理概述

PCB設(shè)計(jì)后期處理概述

PCB設(shè)計(jì)培訓(xùn)

PCB設(shè)計(jì)技術(shù)的三種效應(yīng)

PCB設(shè)計(jì)的重點(diǎn)是什么?

pcb設(shè)計(jì)

AD PCB設(shè)計(jì)是提示Cannot load 3D files mode?

AD21--1個(gè)重新調(diào)整PCB設(shè)計(jì)區(qū)域的方法

Altium Designer PCB文件太大解決方法

Altium18軟件實(shí)操、Altium19預(yù)覽及PCB設(shè)計(jì)學(xué)習(xí)思路方法詳解

Altium中PCB上走線鍍錫的方法

Altium的pcb文件轉(zhuǎn)allegro的方法

“圖文并茂的”PCB設(shè)計(jì)經(jīng)驗(yàn)分享

傳統(tǒng)的PCB設(shè)計(jì)方法

哪有PCB設(shè)計(jì)視頻教程下載

基于Cadence的高速PCB設(shè)計(jì)方法,不看肯定后悔

并行PCB設(shè)計(jì)的關(guān)鍵準(zhǔn)則

怎么利用PCB設(shè)計(jì)電容傳感器?

怎么才能實(shí)現(xiàn)高性能的PCB設(shè)計(jì)?

熱門PCB設(shè)計(jì)技術(shù)方案

繪制數(shù)顯溫度計(jì)電路圖及PCB設(shè)計(jì)方法,有什么注意事項(xiàng)?

給大家介紹一種PCB設(shè)計(jì)復(fù)用方法

進(jìn)行高頻PCB設(shè)計(jì)的技巧和方法有哪些?

高速PCB設(shè)計(jì)經(jīng)驗(yàn)與體會(huì)

高速pcb設(shè)計(jì)指南。

pcb設(shè)計(jì)教程 (收藏多年的經(jīng)典知識(shí))

0

0高速PCB設(shè)計(jì)方法

0

0PCB設(shè)計(jì)技巧百問

0

0PCB設(shè)計(jì)中20H規(guī)則的驗(yàn)證方法

0

0PCB設(shè)計(jì)基礎(chǔ)教程手冊(cè)

0

0[組圖]PCB設(shè)計(jì)方法和技巧(4)

499

499PCB設(shè)計(jì)考慮EMC的接地技巧

1326

1326編寫PCB設(shè)計(jì)規(guī)則檢查器技巧

1019

1019PCB設(shè)計(jì)時(shí)防范ESD的方法

371

371PCB設(shè)計(jì)軟件坐標(biāo)數(shù)據(jù)導(dǎo)出方法

1325

1325減少諧波失真的PCB設(shè)計(jì)方法

1041

1041

導(dǎo)出PCB設(shè)計(jì)軟件坐標(biāo)數(shù)據(jù)的方法

4660

4660

仿制PCB板與電路板

1440

1440穩(wěn)壓電源電路的PCB設(shè)計(jì)

498

498Cadence高速PCB設(shè)計(jì)

0

0PCB抄板/PCB設(shè)計(jì)基本步驟

30289

30289PCB設(shè)計(jì)相關(guān)經(jīng)驗(yàn)分享及PCB新手在PCB設(shè)計(jì)中應(yīng)該注意的問題

0

0PCB設(shè)計(jì)技巧_覆銅技巧

0

0PCB設(shè)計(jì)應(yīng)用教材-嘉立創(chuàng)

0

0PCB設(shè)計(jì)中如何設(shè)置格點(diǎn)_pcb設(shè)計(jì)中格點(diǎn)的設(shè)置方法

11802

11802Altium Designer教程之PCB設(shè)計(jì)基礎(chǔ)的詳細(xì)資料免費(fèi)下載

0

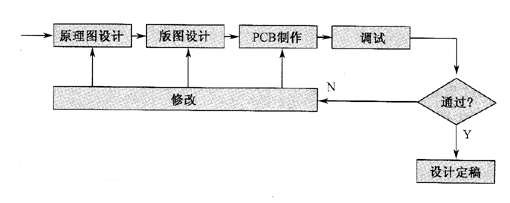

0從原理圖到PCB設(shè)計(jì)流程詳解

8487

8487

降低PCB的KMI無疑是成功的PCB設(shè)計(jì)!

3032

3032

pcb設(shè)計(jì)實(shí)例講解

19080

19080PCB設(shè)計(jì)布線的幾種檢查方法解析

9568

9568

制作PCB設(shè)計(jì)分孔圖的方法分享

3891

3891PCB設(shè)計(jì)中防止串?dāng)_的方法有哪些

6906

6906PADS技術(shù)是更好的一種PCB設(shè)計(jì)方式

2135

2135PCB設(shè)計(jì)軟件輸出裝配圖的3個(gè)方法

11939

11939影響PCB設(shè)計(jì)的一些DFM問題

3805

3805PCB設(shè)計(jì) PCB設(shè)計(jì)用什么軟件

5289

5289pcb設(shè)計(jì)入門基礎(chǔ)知識(shí)介紹

17505

17505PCB設(shè)計(jì)經(jīng)驗(yàn)(1)

19

19PCB設(shè)計(jì)中的20個(gè)規(guī)則!

63

63STC15單片機(jī)實(shí)戰(zhàn)項(xiàng)目 - PCB設(shè)計(jì)

25

25PCB設(shè)計(jì)問題的改善方法和技巧

1177

1177如何確保PCB設(shè)計(jì)信號(hào)完整性的方法

771

771通過PCB設(shè)計(jì)降低PCBA成本的方法

1093

1093PCB設(shè)計(jì)布局規(guī)則及技巧

1554

1554傳統(tǒng)的PCB設(shè)計(jì)方法

151

151

PCB設(shè)計(jì)中遇到的阻抗不連續(xù)問題及解決方法

634

634

高速PCB設(shè)計(jì)中的射頻分析與處理方法

316

316

PCB設(shè)計(jì)阻抗不連續(xù)的原因及解決方法

86

86 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論