74ls574特點

·三態(tài)總線驅動輸出

·置數全并行存取

·緩沖控制輸入

·時鐘輸入有改善抗擾度的滯后作用

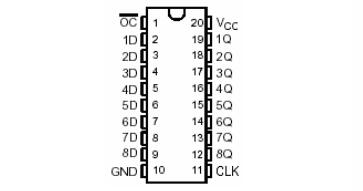

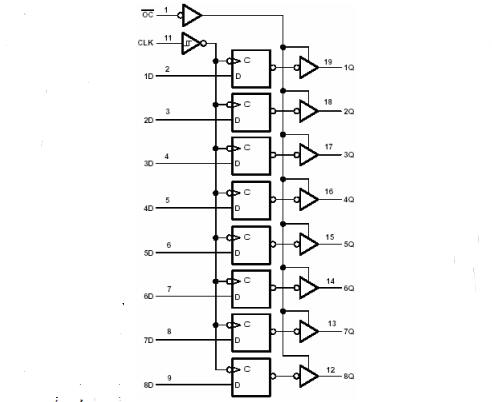

74ls574引腳圖

74ls574功能表

H=高電平 L=低電平 ×=不定 Z=高阻態(tài) ↑=從低轉換到高電平 QO=建立穩(wěn)態(tài)輸入條件前的電平

說明: LS574的八個觸發(fā)器是邊沿觸發(fā) D 型觸發(fā)器。在時鐘的正跳動,Q 輸出將處于 D 輸入端已建立的邏輯狀態(tài)。時鐘線上的施密特觸發(fā)緩沖輸入將簡化系統設計,因為輸入滯后作用使交流和直流抗擾度一般提高 400mV。緩沖輸出的控制輸入將使八個輸出處于正常狀態(tài)(高電平或低電平)或處于高阻狀態(tài)。在高阻態(tài)下,輸出既不能有效地給總線加負載,也不能有效地驅動總線。輸出控制不影響觸發(fā)器的內部工作,既老數據可以保持,甚至當輸出被關閉,新的數據也可以置入。

74ls574內部框圖

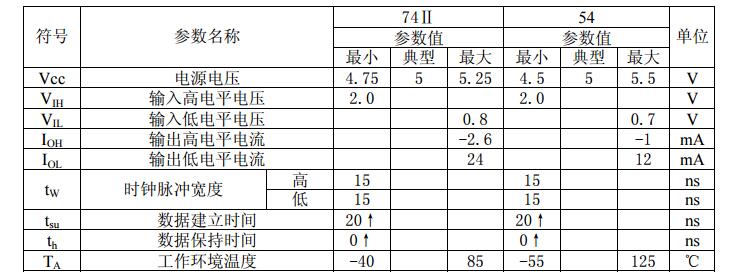

74ls574推薦工作條件

74ls574電性能

(除特別說明外,均為全溫度范圍)

注:Icc在輸出控制端加4.5V時測量。所有典型值均在Vcc=5.0V,TA=25℃下測量得出。

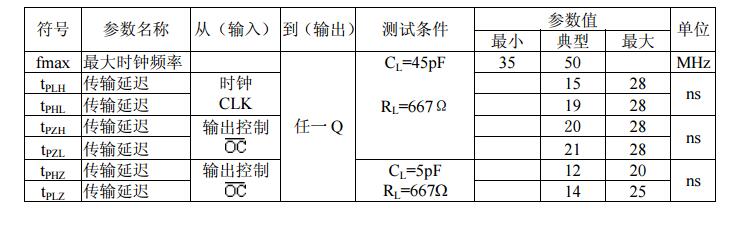

74ls574交流(開關)參數

Vcc=5.0V,TA=25℃

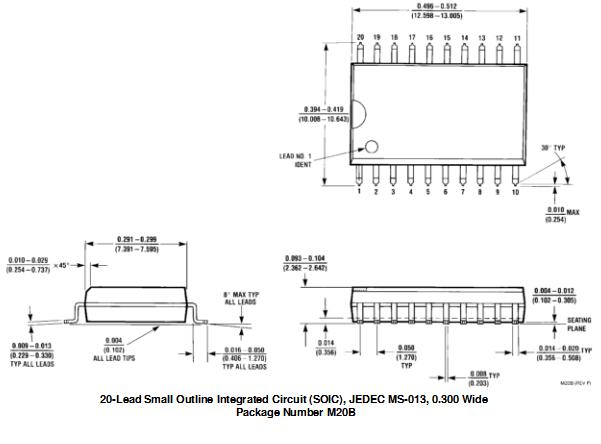

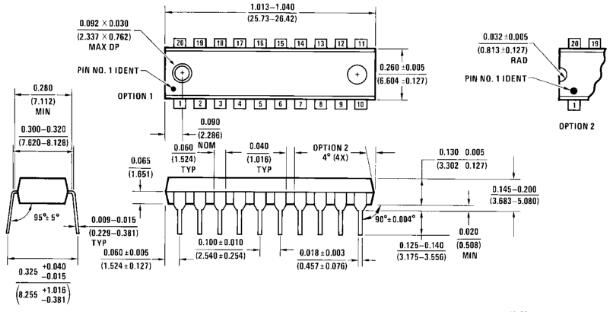

74ls574封裝