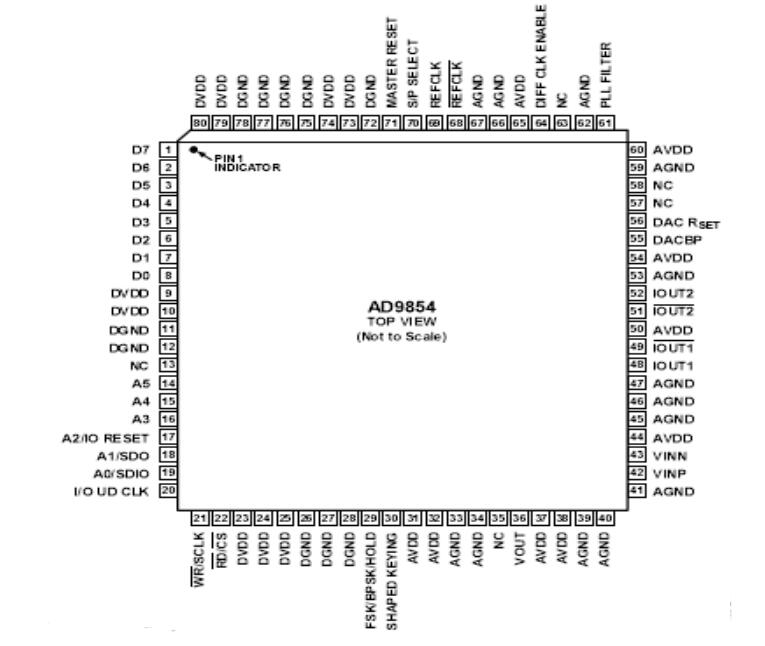

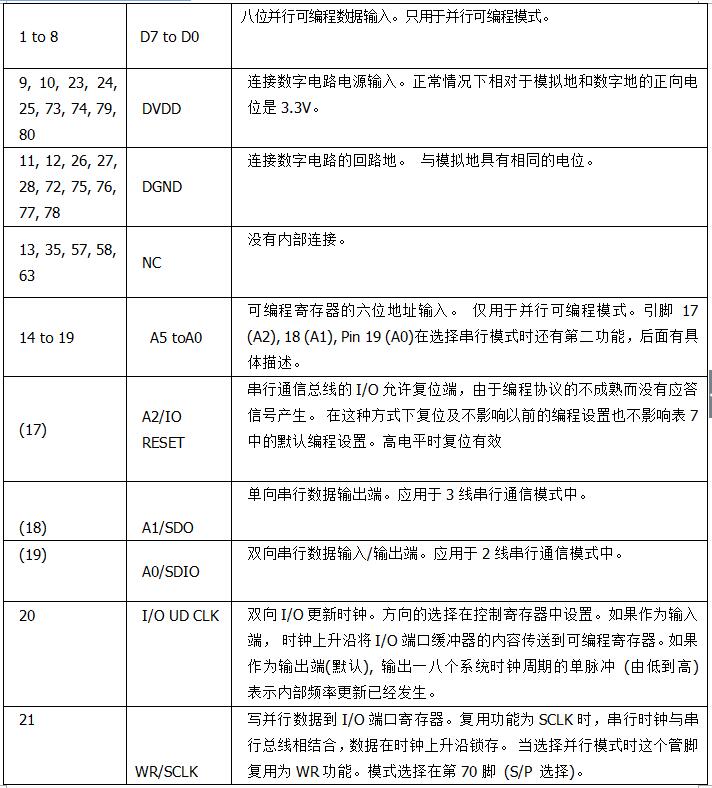

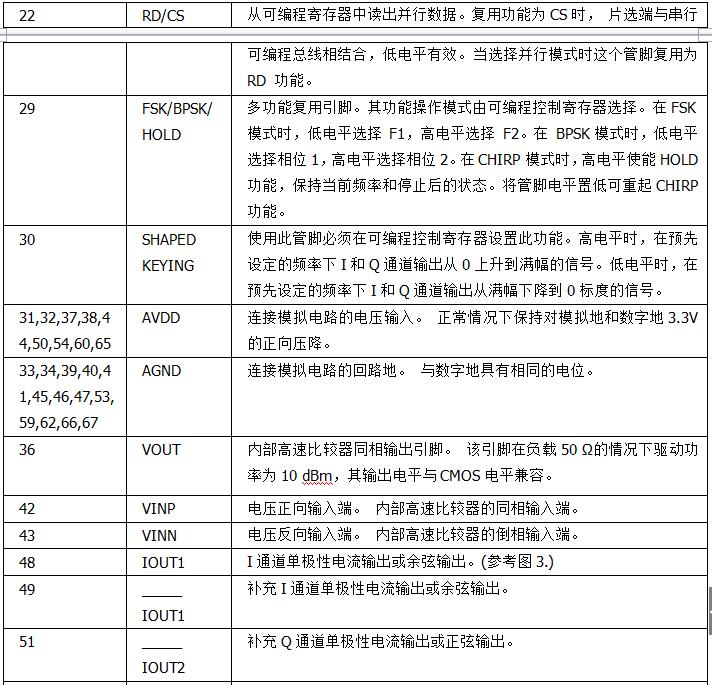

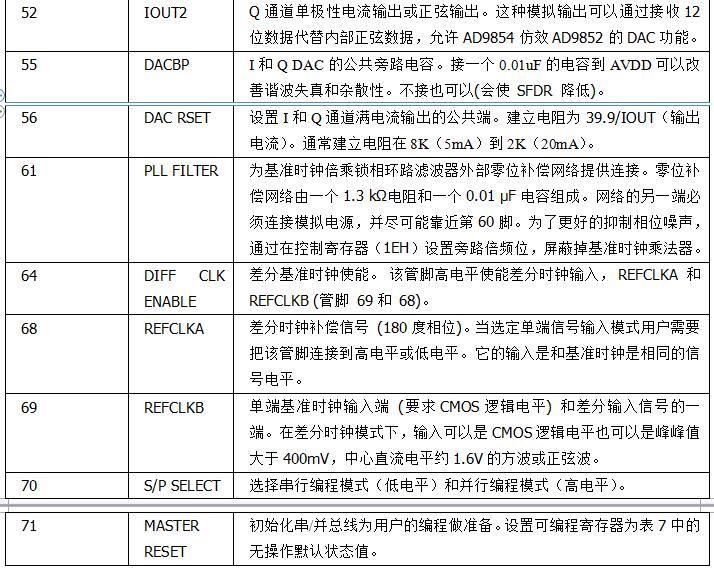

AD9854引腳及功能

引腳描述:

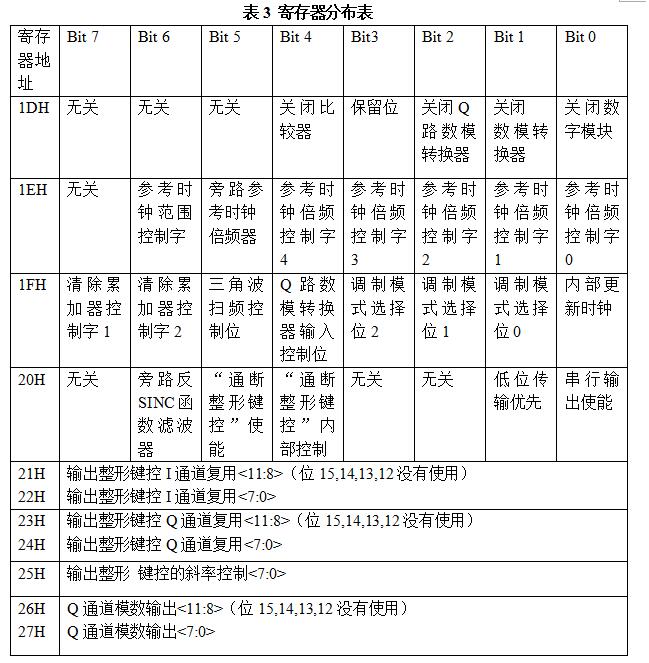

AD9854的編程

AD9854的各寄存器列出在下表,包含各各功能的片內編程信息。很多應用要求很小的編程規模去裝配AD9854,就可以使用了,實現功能了。但有一些要求用戶使用所有的12個寄存器入口地址。AD9854支持8位并行I/O操作或一位SPI-compatible串行I/O操作。所有入口寄存器能讀和寫,在每個I/O操作模式下。S/P選擇,引腳70,用于I/O模式選擇。若系統使用并行I/O模式,必須連接S/P選擇引腳到VDD。若系統操作在串行模式,必須連接S/P選擇引腳到GND。

不使用模式,I/O口數據寫入緩沖寄存器,不影響該部分操作直到緩沖寄存器傳輸數據到寄存器數據庫。信息傳輸同時產生在系統時鐘,兩種產生方式:

(1)內部控制在某一由用戶編程產生的速率

(2)由用戶外部控制,I/O操作能在沒有REFCLK情況下進行,但數據從緩沖期傳輸到存儲器,沒有REFCLK是不行的。能從該文獻更新時鐘章節中了解到更多的詳細信息。復位管理——邏輯高電平有效,必須保證電平不小于10個系統時鐘周期的持續時間。復位主要引起通信總線的初始化并載入默認值到內部或外部的時鐘更新段。

并行輸入輸出操作

在S/P選擇引腳被拉為高電平時,并行輸入輸出模式被激活。這種輸入輸出口與標準工業DSPs 和microcontrollers相兼容。6個地址位,8個雙向數據位,和分離的寫/讀控制輸入來補足這輸入輸出口引腳。

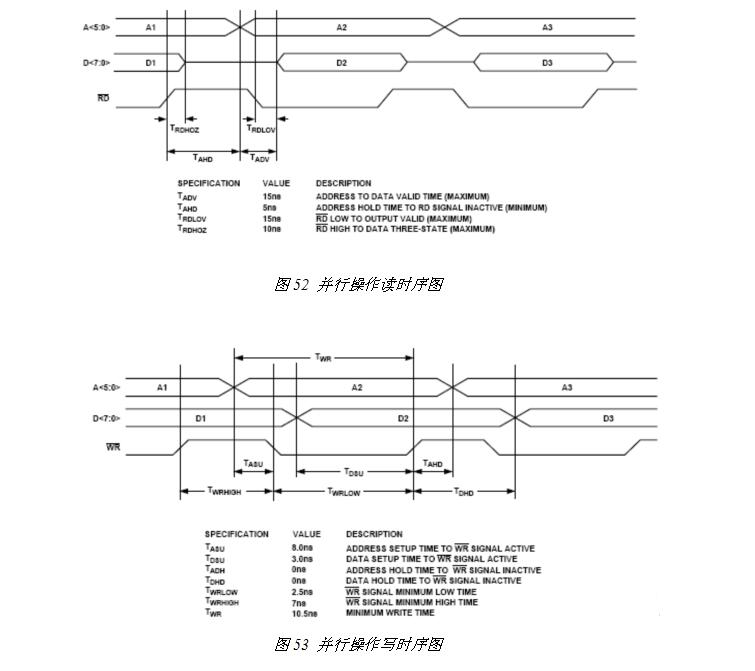

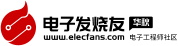

并行輸入輸出操作模式允許到1/10.5納秒對每個寄存器進行單字節操作。對寄存的回讀操作主要用來優化對AD9854的設計 (讀寄存器不能保證100 MHz的操作速度,這一點他們為只是軟件調試準備的)。

并行輸入輸出操作時序圖如圖52 和圖53 所示。