AD9850概要

AD9850是AD公司生產(chǎn)的最高時鐘為125MHz、采用先進(jìn)的CMOS技術(shù)的直接頻率合成器,主要由可編程DDS系統(tǒng)、高性能數(shù)模變換器(DAC)和高速比較器3部分構(gòu)成,能實現(xiàn)全數(shù)字編程控制的頻率合成。

AD9850內(nèi)部結(jié)構(gòu)

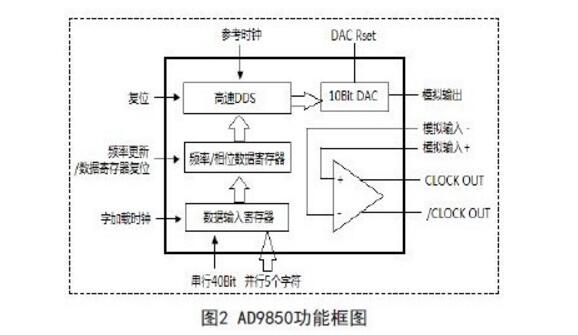

AD9850的芯片功能框圖如圖2所示。

AD9850芯片內(nèi)包括高速DDS.10位DAC.頻率/相位數(shù)據(jù)寄存器。數(shù)據(jù)輸入寄存器。比較器等,在125MHz參考時鐘下,AD9850經(jīng)過高速的DDS核心芯片能產(chǎn)生一個32位頻率調(diào)整控制字可使AD9850的輸出頻率達(dá)0.0291Hz;并能提供了5bits的相位控制位,它能使輸出相位以180°.90°.45°.22.5°.11.25°或是它們?nèi)我饨M合的增量改變.AD9850的電路結(jié)構(gòu)允許產(chǎn)生頻率值是參考時鐘的一半的輸出,并且輸出的頻率能用數(shù)控方式以每秒產(chǎn)生23000000個新頻率的速度變化.AD9850芯片內(nèi)的比較器構(gòu)成能接收經(jīng)外部低通濾波后的DAC轉(zhuǎn)換輸出,可以產(chǎn)生一個低抖動的方波輸出的裝置,因此AD9850用作時鐘發(fā)生器十分方便。頻率/相位數(shù)據(jù)寄存器。數(shù)據(jù)輸入寄存器在外部的頻率更新時鐘和字加載時鐘的控制下進(jìn)行頻率控制字的輸入和更新,使芯片輸出所要求的頻率和相位.

AD9850的工作原理

AD9850內(nèi)含可編程DDS系統(tǒng)和高速比較器,可實現(xiàn)全數(shù)字編程控制的頻率合成。

可編程DDS系統(tǒng)由相位累加器和正弦查表組成,其相位累加器由一個加法器和一個N位的相位寄存器組成,N一般為24~32;實質(zhì)上是一個可變模的計數(shù)器,即DDS相位增量的個數(shù)在計數(shù)器收到每一個時鐘脈沖時被存儲起來,當(dāng)計數(shù)器溢出時,它就回到初態(tài)并使用相位累加器輸出到相鄰值。頻率控制字能設(shè)置計數(shù)器的模,它決定了相位增量的大小。相位增量在每個時鐘到來時便在相位累加器中相加,相位增量越大,則累加器溢出的速度越快,產(chǎn)生的輸出頻率越高。

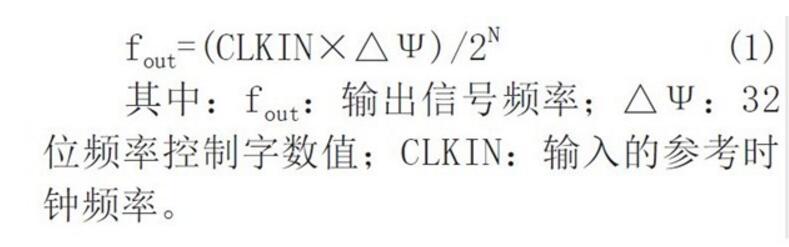

AD9850采用32位的相位累加器,AD9850利用改進(jìn)的,獨(dú)有的算法,把14bits已截斷的相位累加器的輸出轉(zhuǎn)變成適當(dāng)?shù)挠嘞抑担?jīng)片內(nèi)高速的10bitDAC轉(zhuǎn)換器,可得到模擬正弦波。這個獨(dú)特的算法使用一個簡化了的ROM表和DSP技術(shù)等功能,有助于縮小AD9850的體積和功耗。輸入。輸出。參考時鐘和頻率控制字的關(guān)系如下: