與門真值表

與門(英語:AND gate)又稱“與電路”、邏輯“積”、邏輯“與”電路。是執行“與”運算的基本邏輯門電路。有多個輸入端,一個輸出端。當所有的輸入同時為高電平(邏輯1)時,輸出才為高電平,否則輸出為低電平(邏輯0)。

基本功能及真值表

與門是實現邏輯“乘”運算的電路,有兩個以上輸入端,一個輸出端(一般電路都只有一個輸出端,ECL電路則有二個輸出端)。只有當所有輸入端都是高電平(邏輯“1”)時,該電路輸出才是高電平(邏輯“1”),否則輸出為低電平(邏輯“0”)。[1] 其二輸入與門的數學邏輯表達式:Y = AB,對應的真值表如下

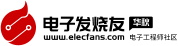

邏輯符號

與門有3種邏輯符號,包括:形狀特征型符號(ANSI/IEEEStd 91-1984)、IEC矩形國標符號(IEC 60617-12)、DIN符號(DIN 40700)。

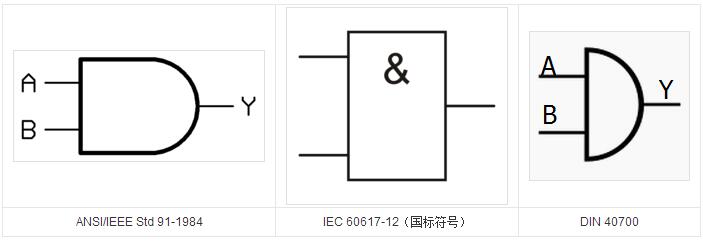

與門是基本的邏輯門,因此在TTL和CMOS集成電路中都是可以使用的。標準的74系列CMOS集成電路有74X08、74X09(OC),包含四個獨立的2輸入與門;74X11,包含三個獨立的3輸入與門;74X21,包含兩個獨立的4輸入與門。CD4000系列集成電路有:CD4081,包含四個2輸入端與門;CD4082,包含兩個4輸入端與門。

引腳分配如下:

與非門真值表

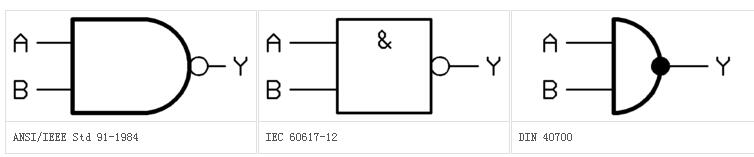

與非門是與門和非門的結合,先進行與運算,再進行非運算。與非運算輸入要求有兩個,如果輸入都用0和1表示的話,那么與運算的結果就是這兩個數的乘積。如1和1(兩端都有信號),則輸出為0;1和0,則輸出為1;0和0,則輸出為1。與非門的結果就是對兩個輸入信號先進行與運算,再對此與運算結果進行非運算的結果。簡單說,與非與非,就是先與后非。

電工學里一種基本邏輯電路,是與門和非門的疊加,有兩個輸入和一個輸出。

CMOS電路中的邏輯門有非門、與門、與非門、或非門、或門、異或門、異或非門,施密特觸發門、緩沖器、驅動器等。

與非門則是當輸入端中有1個或1個以上是低電平時,輸出為高電平;只有所有輸入是高電平時,輸出才是低電平。與非門芯片:74ls系列:74ls00、74LS20,CMOS系列:CD4011

與非門真值表

邏輯符號

與門真值表和與非門真值表的區別

與門真值表:有0出0,全1出1

與非門真值表:有0出1,全1出0