集成電路(integrated circuit)是一種微型電子器件或部件。采用一定的工藝,把一個電路中所需的晶體管、電阻、電容和電感等元件及布線互連一起,制作在一小塊或幾小塊半導(dǎo)體晶片或介質(zhì)基片上,然后封裝在一個管殼內(nèi),成為具有所需電路功能的微型結(jié)構(gòu);其中所有元件在結(jié)構(gòu)上已組成一個整體,使電子元件向著微小型化、低功耗、智能化和高可靠性方面邁進了一大步。它在電路中用字母“IC”表示。集成電路發(fā)明者為杰克·基爾比(基于鍺(Ge)的集成電路)和羅伯特·諾伊思(基于硅(Si)的集成電路)。當(dāng)今半導(dǎo)體工業(yè)大多數(shù)應(yīng)用的是基于硅的集成電路。

是20世紀50年代后期一60年代發(fā)展起來的一種新型半導(dǎo)體器件。它是經(jīng)過氧化、光刻、擴散、外延、蒸鋁等半導(dǎo)體制造工藝,把構(gòu)成具有一定功能的電路所需的半導(dǎo)體、電阻、電容等元件及它們之間的連接導(dǎo)線全部集成在一小塊硅片上,然后焊接封裝在一個管殼內(nèi)的電子器件。其封裝外殼有圓殼式、扁平式或雙列直插式等多種形式。集成電路技術(shù)包括芯片制造技術(shù)與設(shè)計技術(shù),主要體現(xiàn)在加工設(shè)備,加工工藝,封裝測試,批量生產(chǎn)及設(shè)計創(chuàng)新的能力上。

集成電路是什么

由電子元件和電子器件組成的電路叫電子電路。通常將電子設(shè)備中的電阻器、電容器、電感器、變壓器、開關(guān)等稱為電子元件,而將電子管、離子管、晶體管等稱為電子器件。電子電路按組成方式,可分為分立電路和集成電路二大類。

集成電路(integrated circuit)是一種微型電子器件或部件。采用一定的工藝,把一個電路中所需的晶體管、二極管、電阻、電容和電感等元件及布線互連一起,制作在一小塊或幾小塊半導(dǎo)體晶片或介質(zhì)基片上,然后封裝在一個管殼內(nèi),成為具有所需電路功能的微型結(jié)構(gòu);其中所有元件在結(jié)構(gòu)上已組成一個整體,使電子元件向著微小型化、低功耗和高可靠性方面邁進了一大步。

它在電路中用字母“IC”表示。集成電路發(fā)明者為杰克·基爾比(基于鍺的集成電路)和羅伯特·諾伊思(基于硅的集成電路)。當(dāng)今半導(dǎo)體工業(yè)大多數(shù)應(yīng)用的是基于硅的集成電路。集成電路或稱微電路(microcircuit)、 微芯片(microchip)、芯片(chip)在電子學(xué)中是一種把電路(主要包括半導(dǎo)體裝置,也包括被動元件等)小型化的方式,并通常制造在半導(dǎo)體晶圓表面上。前述將電路制造在半導(dǎo)體芯片表面上的集成電路又稱薄膜(thin-film)集成電路。另有一種厚膜(thick-film)混成集成電路(hybrid integrated circuit)是由獨立半導(dǎo)體設(shè)備和被動元件,集成到襯底或線路板所構(gòu)成的小型化電路。本文是關(guān)于單片(monolithic)集成電路,即薄膜集成電路。集成電路具有體積小,重量輕,引出線和焊接點少,壽命長,可靠性高,性能好等優(yōu)點,同時成本低,便于大規(guī)模生產(chǎn)。它不僅在工、民用電子設(shè)備如收錄機、電視機、計算機等方面得到廣泛的應(yīng)用,同時在軍事、通訊、遙控等方面也得到廣泛的應(yīng)用。用集成電路來裝配電子設(shè)備,其裝配密度比晶體管可提高幾十倍至幾千倍,設(shè)備的穩(wěn)定工作時間也可大大提高。

集成電路上電復(fù)位與關(guān)斷功能作用

現(xiàn)代集成電路采用精密復(fù)雜的電路來確保其開啟后進入已知狀態(tài),保留存儲器內(nèi)容,快速引導(dǎo),并且在其關(guān)斷時節(jié)省功耗。本文分兩部分,提供有關(guān)使用上電復(fù)位和關(guān)斷功能的一些建議。

簡介

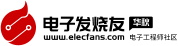

許多IC 都包含上電復(fù)位(POR)電路,其作用是保證在施加電源后,模擬和數(shù)字模塊初始化至已知狀態(tài)。基本POR功能會產(chǎn)生一個內(nèi)部復(fù)位脈沖以避免“競爭”現(xiàn)象,并使器件保持靜態(tài),直至電源電壓達到一個能保證正常工作的閾值。注意,此閾值電壓不同于數(shù)據(jù)手冊中給出的最小電源電壓。一旦電源電壓達到閾值電壓,POR電路就會釋放內(nèi)部復(fù)位信號,狀態(tài)機開始初始化器件。在初始化完成之前,器件應(yīng)當(dāng)忽略外部信號,包括傳輸?shù)臄?shù)據(jù)。唯一例外是復(fù)位引腳(如有),它會利用POR信號內(nèi)部選通。POR電路可以表示為窗口比較器,如圖1 所示。比較器電平VT2在電路設(shè)計期間定義,取決于器件的工作電壓和制程尺寸。

POR策略

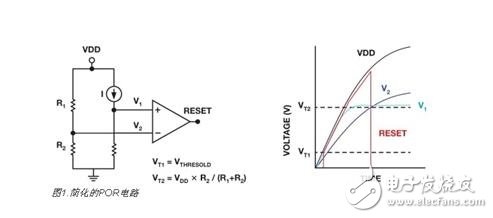

比較器窗口通常由數(shù)字電源電平定義。數(shù)字模塊控制模擬模塊,數(shù)字模塊全面工作所需的電壓與模擬模塊工作所需的最小電壓相似,如圖2所示。

較高的VT2閾值對模擬模塊會更好,但若過于接近推薦最小電源電壓,當(dāng)電壓略微降低時,可能會意外觸發(fā)復(fù)位。如果器件包括獨立的模擬電源和數(shù)字電源,則避免故障的一種策略是增加一個POR電路,使兩個模塊保持復(fù)位狀態(tài),直至電源電壓高到足以確保電路正常工作。例如,在一種3V IC工藝中,VT1 ≈ 0.8 V,VT2 ≈ 1.6 V。

這些電壓會隨著制程以及其他設(shè)計偏移而變化,但它們是合理的近似值。閾值容差可以是20%或更大,某些舊式設(shè)計的容差高達40%。高容差與功耗相關(guān)。POR必須一直使能,因此精度與功耗之間始終存在的取舍關(guān)系很重要;較高的精度會提高電路在待機模式下的功耗,而對功能性并無實際意義。

掉電檢測器

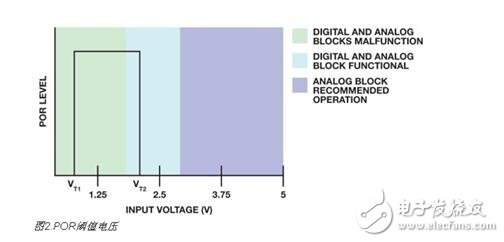

POR 電路有時會集成一個掉電檢測器(BOD),用于防止電路在電壓非常短暫地意外降低時發(fā)生復(fù)位,從而避免故障。實際上,掉電電路給POR模塊所定義的閾值電壓增加了遲滯,通常為300mV左右。BOD保證,當(dāng)電源電壓降至VT2以下時,POR不會產(chǎn)生復(fù)位脈沖,除非電源電壓降至另一閾值VBOD以下,如圖3 所示。

掉電閾值電平足以保證數(shù)字電路保留信息,但不足以保證其正常工作。這樣,控制器可以在電源降至某一電平以下時中止活動而不會讓整個器件都重新初始化,如果電源電平只是非常短暫地降低的話。

器件正確上電

實際的POR電路比圖1 所示的簡化版本要復(fù)雜得多,例如用MOS晶體管代替電阻。因此,必須考慮寄生模型。另外,POR電路需要一個啟動模塊來產(chǎn)生啟動脈沖,這在某些情況下可能會失效。其他重要考慮在以下內(nèi)容中說明。

必須使用單調(diào)性電源,因為若使用非單調(diào)性電源,當(dāng)偏差接近任何閾值電平時,非單調(diào)性斜坡可能會引起問題。較高的閾值偏差會引起同樣的非單調(diào)性序列對某一個元件有效,而對其他元件無效,如圖4 所示。

某些時候,即使斷開電源(禁用LDO),儲能電容也會保留一定的殘余電壓,如圖5 所示。此電壓應(yīng)盡可能小,以便保證電源能降至VT1 以下,否則POR將無法正確復(fù)位,器件將無法正確初始化。

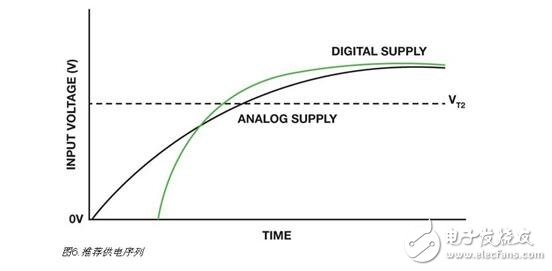

某些數(shù)據(jù)手冊給出了應(yīng)當(dāng)應(yīng)用于具有一個以上電源引腳的器件的推薦供電序列。遵守這個序列是很重要的。例如,想想一個具有兩個獨立電源的器件。推薦供電序列要求數(shù)字電源先于模擬電源供電(這是常規(guī),因為數(shù)字模塊控制模擬模塊,所以必須首先為數(shù)字模塊供電),該模塊必須首先初始化。哪個電源首先開始上升不重要,但數(shù)字電源必須先于模擬電源跨過閾值,如圖6 所示。如果電源之間的延遲為100 μs左右,則影響應(yīng)當(dāng)很小,器件應(yīng)能正確初始化。

由于內(nèi)部三極管寄生效應(yīng),數(shù)百ms 的慢速電源斜坡可能會引起問題。POR 電路要在各種壓擺率下進行評估,以保證其在正常電源條件下能正確工作。數(shù)據(jù)手冊會說明是否需要快速電源斜坡(100 μs或更短)。

例如,對于用細電纜連接電源的電路板,不良的接地連接會具有高阻抗,它可能會在上電期間產(chǎn)生毛刺。另外,在某些電磁環(huán)境(EME)下,MOS晶體管的寄生柵極電容可能會充電,導(dǎo)致晶體管不能正常工作,除非讓該電容放電。這可能引起POR初始化失敗。

漂移和容差也需要考慮。某些情況下,電容等分立元件具有高容差(高達40%)和高漂移(隨溫度、電壓和時間的漂移)。此外,閾值電壓具有負溫度系數(shù)。例如,VT1 在室溫下為0.8V,在-40°C下為0.9 V,在+105°C 為0.7V。

現(xiàn)代集成電路采用精密復(fù)雜的電路來確保其開啟后進入已知狀態(tài),保留存儲器內(nèi)容,快速引導(dǎo),并且在其關(guān)斷時節(jié)省功耗。本文分兩部分,提供有關(guān)使用上電復(fù)位和關(guān)斷功能的一些建議。

斷電還是關(guān)斷?

“當(dāng)然是關(guān)斷!”對這個問題感到吃驚的人會大聲說道。其他人可能會尋思二者有何差異。關(guān)斷模式常常會保留存儲器內(nèi)容,啟動時間更短,漏電流超低,而如果切斷電源,這一切都不復(fù)存在。但是,假如不需要這些特性呢?設(shè)計人員會讓電源保持穩(wěn)定并使用關(guān)斷模式而浪費電源嗎?為何不能簡單地通過切斷電源來降低漏電流?關(guān)斷模式是否存在一些基本的深層次的要求?感到迷惑不解?請看下文。

誘惑與風(fēng)險

現(xiàn)代系統(tǒng)包含豐富的特性,這是通過多層次的復(fù)雜設(shè)計實現(xiàn)的,常常涉及到不止一個芯片。功耗是很多應(yīng)用都關(guān)心的,諸如便攜式醫(yī)療設(shè)備,因此這些芯片常常包含一種或多種關(guān)斷模式。這些模式提供存儲器內(nèi)容保留、外設(shè)使用和快速開啟等特性,而消耗的電源電流非常少。另一種方法是完全關(guān)斷電源。這會完全切斷芯片的電源,不允許任何電流進入電源引腳。雖然能夠降低功耗,但這種方法存在一些嚴重的副作用。

考慮一個包括多個芯片的復(fù)雜系統(tǒng),這些芯片通過多路復(fù)用總線相連。如果該系統(tǒng)設(shè)計用于功耗受限的應(yīng)用,簡單地切斷未在使用的芯片電源似乎有利可圖,尤其是在不需要關(guān)斷模式提供的其他特性的時候。切斷電源可降低漏電流,但沒有電源時,引腳對輸入信號可能起到低阻抗節(jié)點的作用,導(dǎo)致不可預(yù)測的操作和潛在的系統(tǒng)級威脅。雖然斷電選項可能很誘人,但關(guān)斷模式對復(fù)雜系統(tǒng)有著根本上的好處:它使各芯片處于已知的、希望的狀態(tài),即使芯片在低功耗與高性能模式之間循環(huán),也能維持安全可靠的操作。詳細情況可通過考察一個I/O節(jié)點來了解。

簡單示例

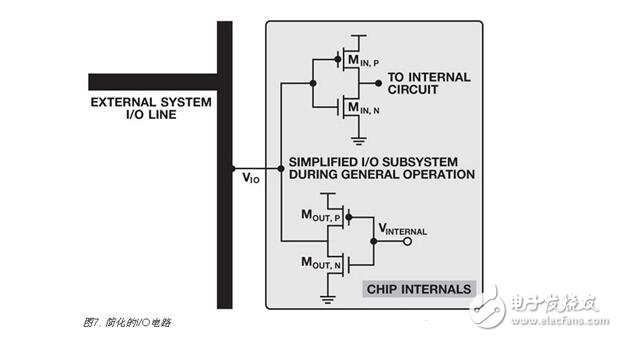

圖7中的引腳連接到一個復(fù)用節(jié)點,其操作由一個經(jīng)驗證的系統(tǒng)架構(gòu)設(shè)定。作為I/O引腳,它同時擁有輸入和輸出功能。

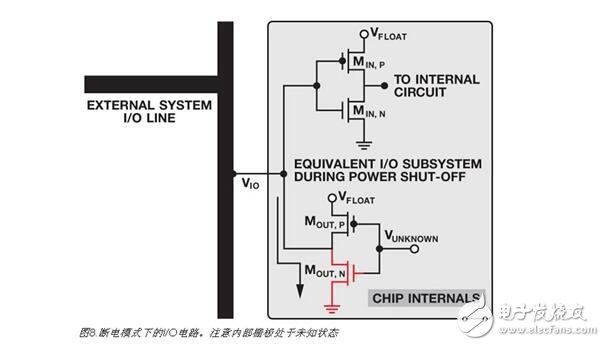

不考慮功率開關(guān)所用器件的問題,斷開此芯片的電源(假設(shè)不需要任何芯片操作)將導(dǎo)致圖8所示的情況,芯片內(nèi)核到處都是未知狀態(tài)。在最壞情況下,浮置柵極輸出器件(MOUT, p 和MOUT, n)可能會在休眠時暴露于意想不到的外部電壓下。對于本例所示的CMOS I/O,這可能產(chǎn)生一個經(jīng)由NMOS漏極連接的對地低阻抗連接(紅色亮顯)。高電流將導(dǎo)致前一級的驅(qū)動能力透支,從而損害芯片中的MOS電路,甚至芯片本身。即使未損害系統(tǒng),其性能也會降低。

關(guān)斷模式

關(guān)斷模式為芯片提供額外的一重保護,可防范上述意外工作狀況。實現(xiàn)方式會因不同的模式、產(chǎn)品系列和供應(yīng)商而異,但重點是在芯片內(nèi)核休眠時提供安全的I/O邊界,維持已知的、可信賴的低功耗狀態(tài)。好處是系統(tǒng)器件之間的I/O操作(例如通過系統(tǒng)級多路復(fù)用總線)不會威脅到休眠中的器件。一個實現(xiàn)方案是在低功耗模式下將I/O引腳置于高阻態(tài),使連接到邊界引腳的內(nèi)部節(jié)點處于已精確定義的狀態(tài)。圖9 顯示了一個簡化的實現(xiàn)方案。信號對內(nèi)部電路無影響,從根本上保證其安全。其他實現(xiàn)方案(例如淺休眠模式)也可以讓I/O外設(shè)保持上電,同時確保在關(guān)斷模式期間芯片外設(shè)與內(nèi)核之間的操作得到驗證。這使得芯片在保持低功耗的同時,能夠處理激活狀態(tài)下的使用情形。此外,該系統(tǒng)降低了功率開關(guān)的成本;如若不然,將需要使用一個很大的低電阻器件,其漏電流和導(dǎo)通狀態(tài)功耗均會相當(dāng)大。

關(guān)斷模式因芯片和供應(yīng)商而異,因此,“淺休眠模式”之類名稱的含義并不總是相同。有些支持保留存儲器內(nèi)容,有些則提供更多的中斷數(shù)或其他類似特性。與完全斷電相比,這些模式的一個突出優(yōu)勢是可以縮短系統(tǒng)響應(yīng)時間。有些電路提供單獨的I/O電源和內(nèi)核電源。這種分離的一個優(yōu)點是,電路板設(shè)計人員可以切斷內(nèi)核電源以降低漏電流,而I/O 則保持上電。強烈建議一定要從產(chǎn)品數(shù)據(jù)手冊獲得準(zhǔn)確的詳細信息,確保所需的特性和保護方法受到產(chǎn)品的支持。

尺寸不斷縮小的影響

作為器件尺寸縮小的自然后果,現(xiàn)代IC工藝技術(shù)提供更高密度的封裝,使得關(guān)斷模式的優(yōu)化使用越來越重要。不過,這也降低了器件的壓力處理能力。例如,28nm 器件的柵極氧化物就比相應(yīng)的180nm 器件要薄。這樣,斷電模式下柵極電壓所施加的壓力更有可能損壞較小的器件。此外,布局相關(guān)的參數(shù)也可能導(dǎo)致尺寸較小的器件發(fā)生災(zāi)難性故障。

所有這些影響使得關(guān)斷模式對現(xiàn)代器件越來越有吸引力。現(xiàn)代芯片充盈著各種特性,包括成百上千萬的元件;如果保持開啟,每個器件都可能產(chǎn)生漏電流。優(yōu)化特性使用并關(guān)斷芯片中不使用的部分,可以消除其中的大部分漏電流。然而用戶應(yīng)該確保供應(yīng)商明確支持這些模式,而不要試圖自行開發(fā)關(guān)斷功能。

更多情形

關(guān)于關(guān)斷的完整拼圖還缺幾片。如果同時切斷接地連接(這將形成另一條低阻抗路徑)會怎樣?這與直接驅(qū)動I/O引腳而不使能電源的ESD 情況相似,如果信號足夠強,可能會觸發(fā)ESD 保護結(jié)構(gòu),導(dǎo)致高電流流經(jīng)其他相連的I/O引腳,產(chǎn)生假上電情況。更有可能的情況是信號稍弱一點,但仍然強到足以通過一條路徑(如I/O箝位)抵達電源。信號可能無法觸發(fā)電源箝位,但會在電源上引起意想不到的虛電壓,從而造成未知工作狀態(tài),具體情形取決于芯片的拓撲結(jié)構(gòu)。任一情況下,如果電路狀態(tài)持續(xù)如此,則芯片可能受損,除非前一級已經(jīng)停止供應(yīng)高電流。如果信號強度不足以觸發(fā)I/O箝位,它仍可能會對所遇到的第一個晶體管施壓,長時間操作后可能會損壞該晶體管。

如果斷開電源并拉低電源輸入呢?這種情況下,芯片無浮動電源,不可能觸發(fā)任何ESD 結(jié)構(gòu),但PMOS漏極電壓可能高于主體電壓,使漏極-主體二極管正偏。這樣,來自前一級的電流將經(jīng)過PMOS 器件流至地,直至器件燒毀、前一級停止提供電流或設(shè)計人員注意到報警。

結(jié)論

本文討論了電路板上電時可能引發(fā)系統(tǒng)問題的一些常見問題,并說明了保證電路板正確初始化的基本原則。電源常常被忽視,但其最終電壓精度和過渡行為均很重要。

關(guān)斷模式使得系統(tǒng)級響應(yīng)更快速、更安全,因而是不可缺少的特性,尤其是在考察復(fù)雜系統(tǒng)中的完整信號鏈時。如果器件之間的交互很有限,或者系統(tǒng)整體很簡單,足以確保不會出現(xiàn)復(fù)雜情況,則可以考慮完全切斷電源。