我從何處入手?

哪一款通用軟件無(wú)線(xiàn)電外設(shè)(USRP)適合我?

我應(yīng)該使用哪種軟件開(kāi)發(fā)工具?

本技術(shù)白皮書(shū)介紹了各種USRP型號(hào)之間的主要差異,可以幫助您選擇合適的無(wú)線(xiàn)電。

軟件無(wú)線(xiàn)電簡(jiǎn)介

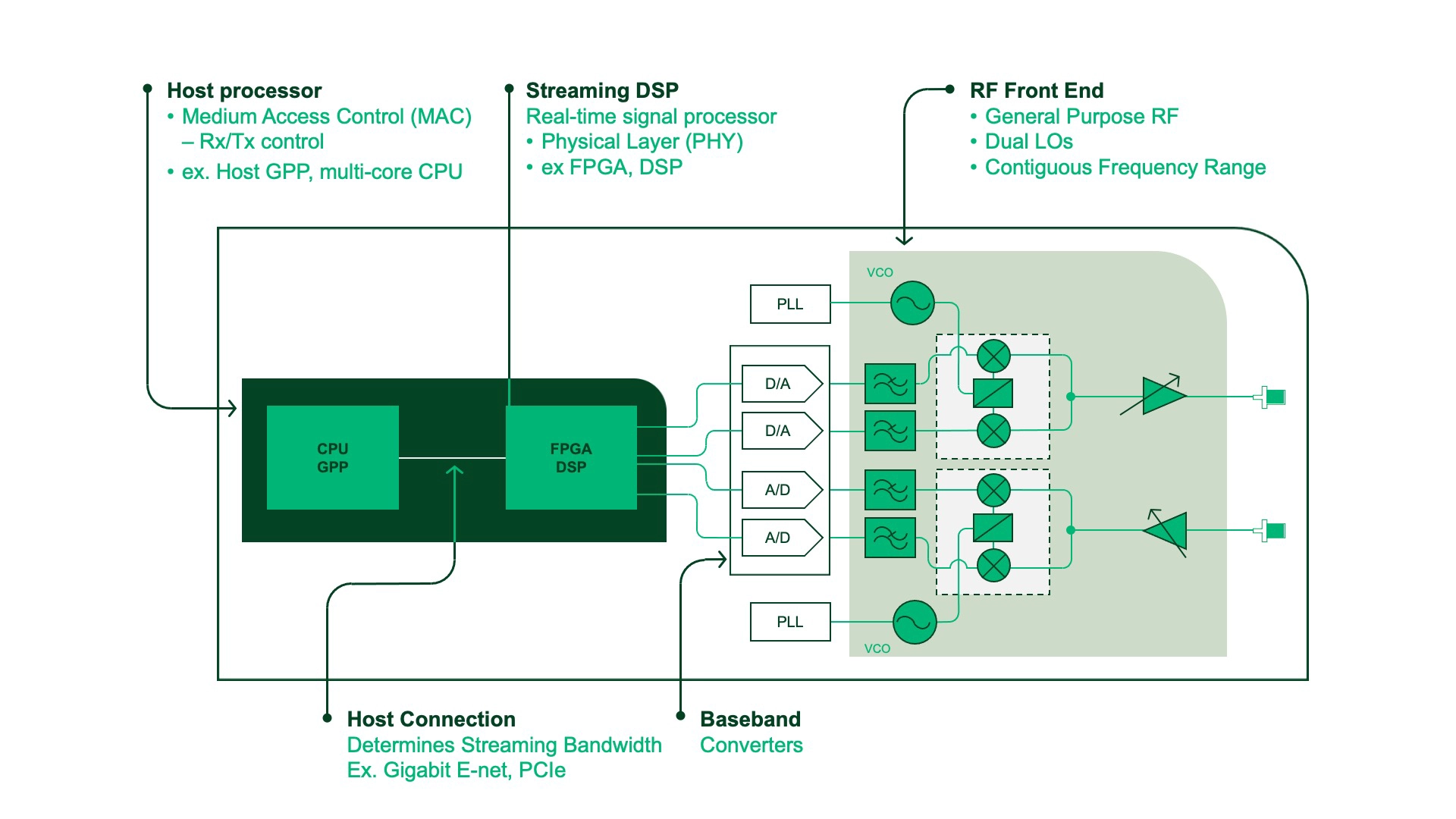

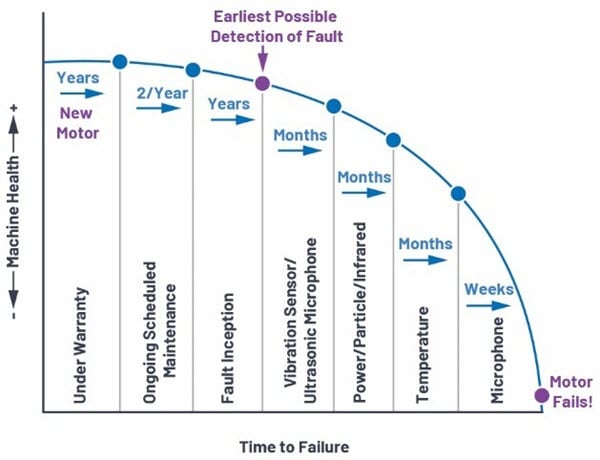

軟件無(wú)線(xiàn)電是一種無(wú)線(xiàn)設(shè)備,通常用于無(wú)線(xiàn)研究的原型驗(yàn)證和部署應(yīng)用程序。SDR通常用于通信、新一代雷達(dá)、電子戰(zhàn)(EW)、空口(OTA)測(cè)試和5G研究等領(lǐng)域。大部分SDR具有通用的硬件架構(gòu),其中包括不同性能的通用處理器(GPP)、FPGA以及RF前端。

圖1.SDR的標(biāo)準(zhǔn)硬件架構(gòu)

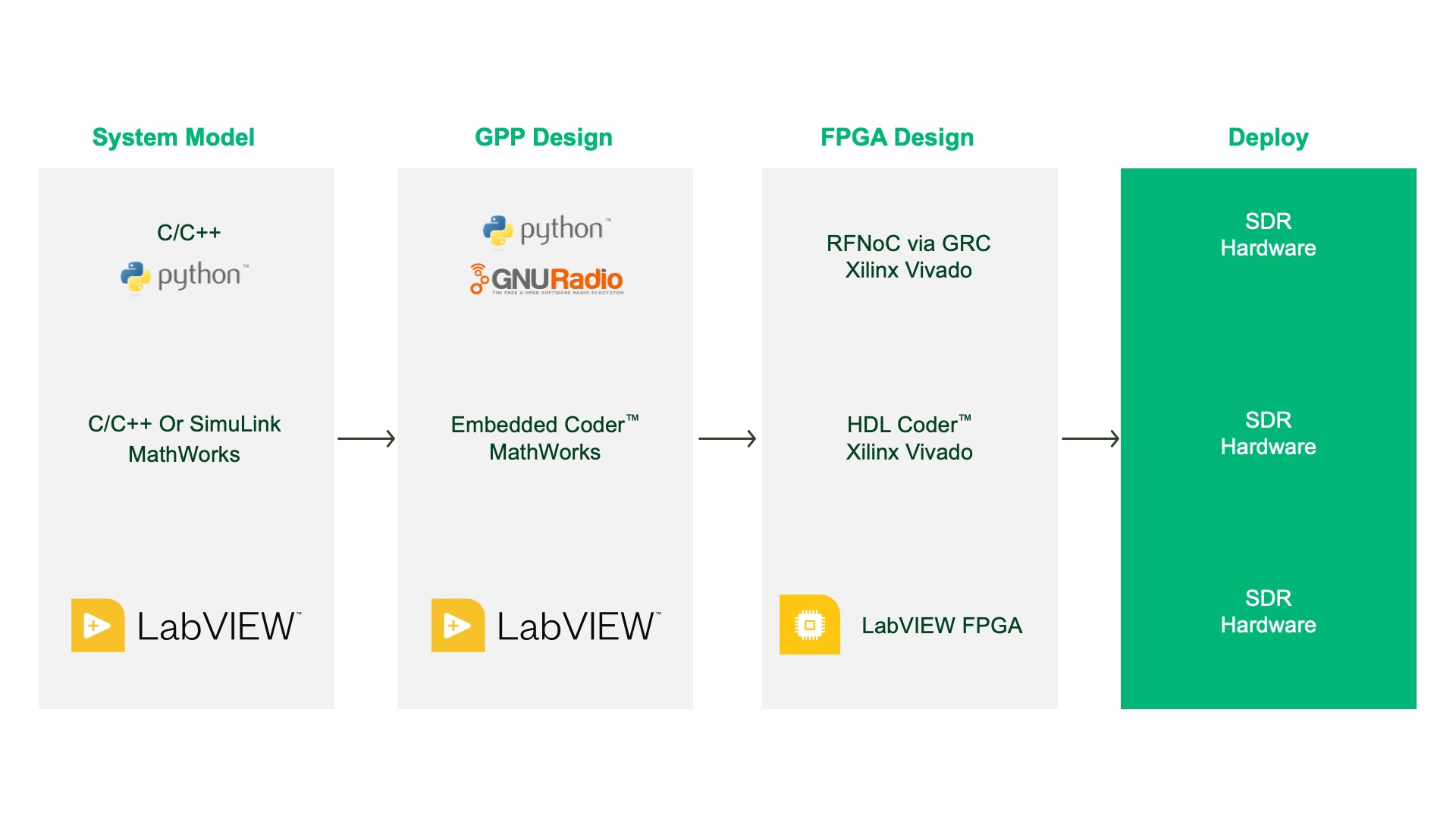

針對(duì)主機(jī)應(yīng)用程序代碼開(kāi)發(fā),工程師使用以下常見(jiàn)工具:

使用開(kāi)源硬件驅(qū)動(dòng)程序的C/C++或Python

Redhawk或GNU Radio等開(kāi)源SDR框架

軟件開(kāi)發(fā)工具和操作系統(tǒng)可以幫助確定哪一款無(wú)線(xiàn)電最適合您的應(yīng)用程序。

許多應(yīng)用程序需要使用FPGA設(shè)備進(jìn)行信號(hào)處理硬件加速。多款USRP具備這項(xiàng)功能,它們均提供了眾多FPGA開(kāi)發(fā)選項(xiàng),稍后將更詳細(xì)地介紹這一點(diǎn)。

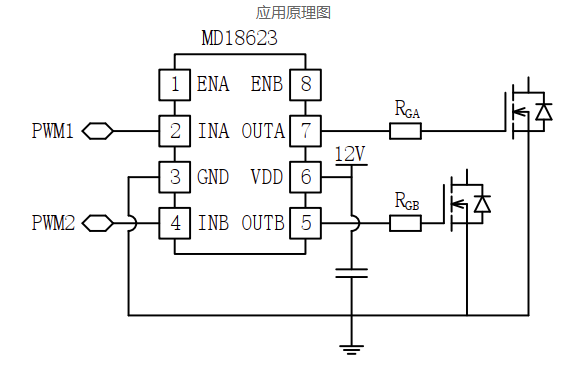

圖2概述了USRP上可用的軟件和FPGA開(kāi)發(fā)的通用工具流程。

圖2:SDR的軟件和FPGA選項(xiàng)

NI和Ettus Research USRP產(chǎn)品是一系列軟件無(wú)線(xiàn)電,旨在滿(mǎn)足廣泛的無(wú)線(xiàn)原型驗(yàn)證和部署需求。讓我們來(lái)了解各種硬件和軟件的注意事項(xiàng),以幫助您選擇合適的無(wú)線(xiàn)電。

硬件選項(xiàng)

在為您的應(yīng)用程序挑選合適的USRP設(shè)備時(shí),最好先問(wèn)自己一些與信號(hào)參數(shù)、大小、重量、功率、成本(SWaP-C)、性能和環(huán)境應(yīng)用要求相關(guān)的問(wèn)題。問(wèn)題1:我需要多大的中心頻率和帶寬?

這個(gè)問(wèn)題很容易回答,但下一個(gè)問(wèn)題就復(fù)雜多了:我打算如何將信號(hào)數(shù)據(jù)移至設(shè)備上,或?qū)⑵湟瞥鲈O(shè)備?

為此,我們需要關(guān)注數(shù)據(jù)接口的重要性。例如,USRP-290x型號(hào)通過(guò)USB連接到主機(jī),并且受到該接口的最大持續(xù)帶寬的限制;而NI Ettus USRP X410配備兩個(gè)雙路100 GbE接口,可傳輸更多的數(shù)據(jù)。

想要了解有關(guān)USRP接口帶寬注意事項(xiàng)的更多內(nèi)容,請(qǐng)查閱Ettus Research知識(shí)庫(kù)上USRP帶寬和采樣率。

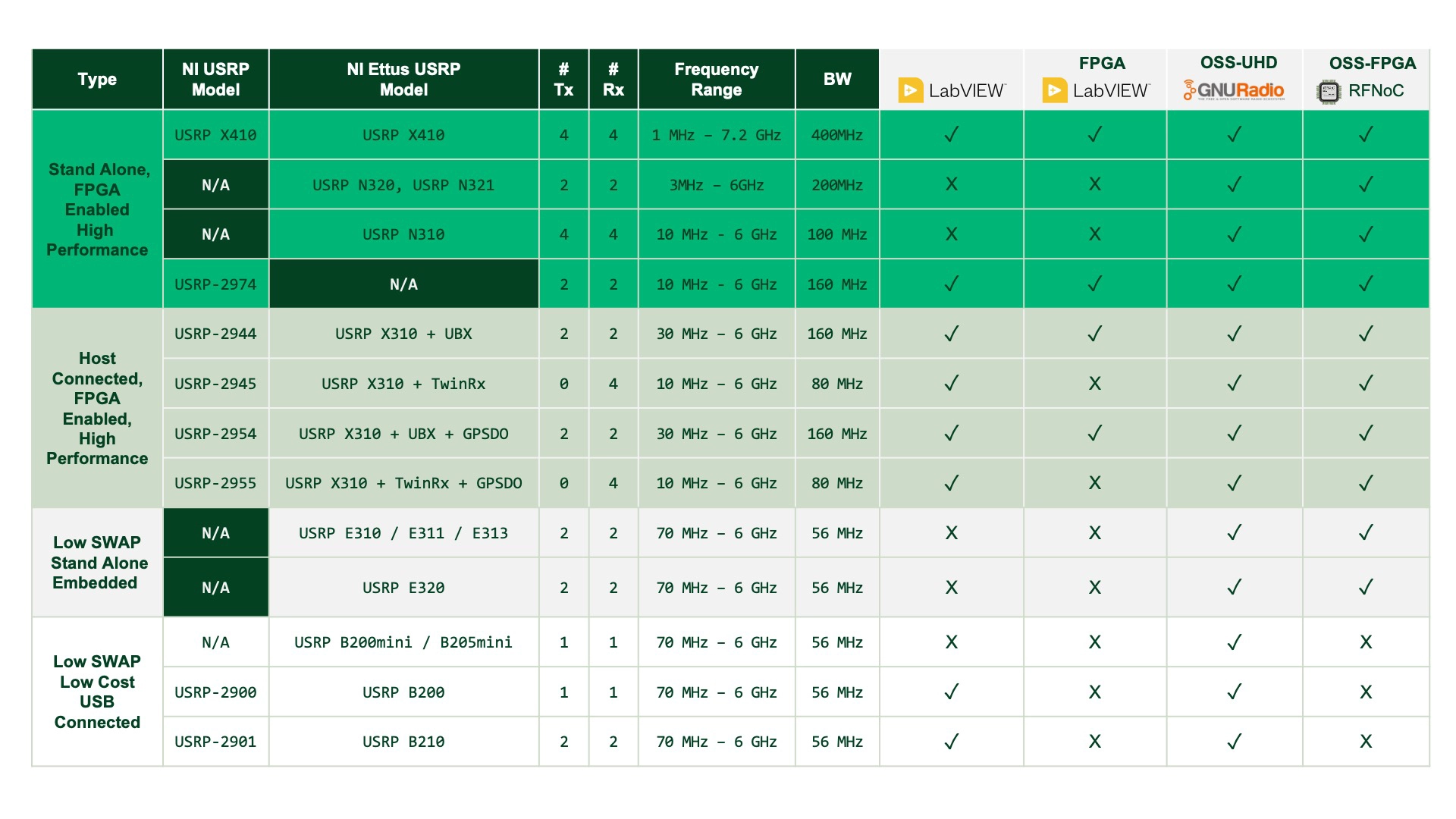

大多數(shù)USRP設(shè)備的最高頻率可達(dá)6 GHz,部分設(shè)備更高;但是NI Ettus USRP X410可在7 GHz頻帶內(nèi)運(yùn)行。在低頻端,部分無(wú)線(xiàn)電的頻率可低至75 MHz,有些甚至可低至直流頻率,具體情況取決于使用的模擬芯片組。查看圖15可了解每個(gè)型號(hào)的細(xì)分情況。

價(jià)格和性能的權(quán)衡

在選擇USRP設(shè)備時(shí)需要權(quán)衡利弊,特別是要權(quán)衡價(jià)格和性能。 如果您需要高性?xún)r(jià)比的無(wú)線(xiàn)電,并且沒(méi)有高級(jí)FPGA或高帶寬方面的需求,那么NI USRP 290x或Ettus Research B200mini都是不錯(cuò)的選擇。如果您需要最高的帶寬,高達(dá)7.2 GHz的頻率,NI Ettus USRP X410可能是最合適的選擇。 介于這兩款例舉的型號(hào)之間還有很多選擇。 下面的圖15介紹了所有型號(hào)的細(xì)分情況。

獨(dú)立的或已連接主機(jī)的SDR選項(xiàng)

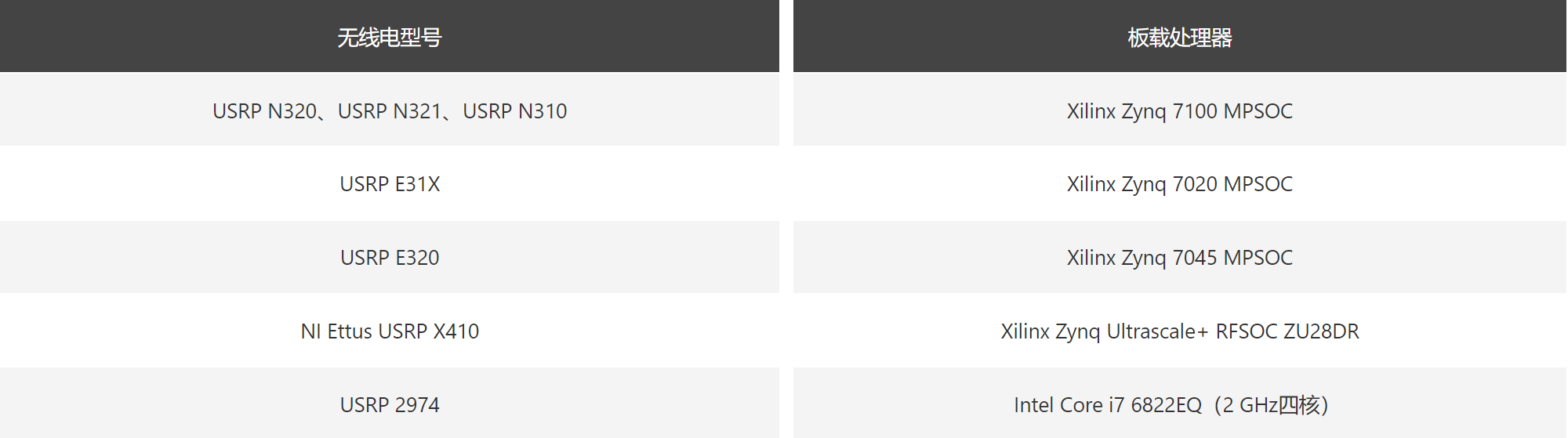

USRP被視為是一種計(jì)算機(jī)外設(shè),可將軟件與電磁頻譜相連。自第一個(gè)USRP問(wèn)世以后,應(yīng)用一直在發(fā)展,許多應(yīng)用需要板載嵌入式處理器。如果您應(yīng)用中的SDR分布在集中式控制系統(tǒng)之外或單獨(dú)部署,則您可能需要此獨(dú)立配置。如果獨(dú)立配置是必要的,則您需要決定Xilinx Zynq多處理器片上系統(tǒng)(MPSOC)或射頻片上系統(tǒng)(RFSOC)是否足夠,或者您是否需要強(qiáng)大的板載Intel X86處理器。圖1介紹了各種型號(hào)及其板載處理器的細(xì)分情況,可參考USRP規(guī)格文檔了解更多信息。

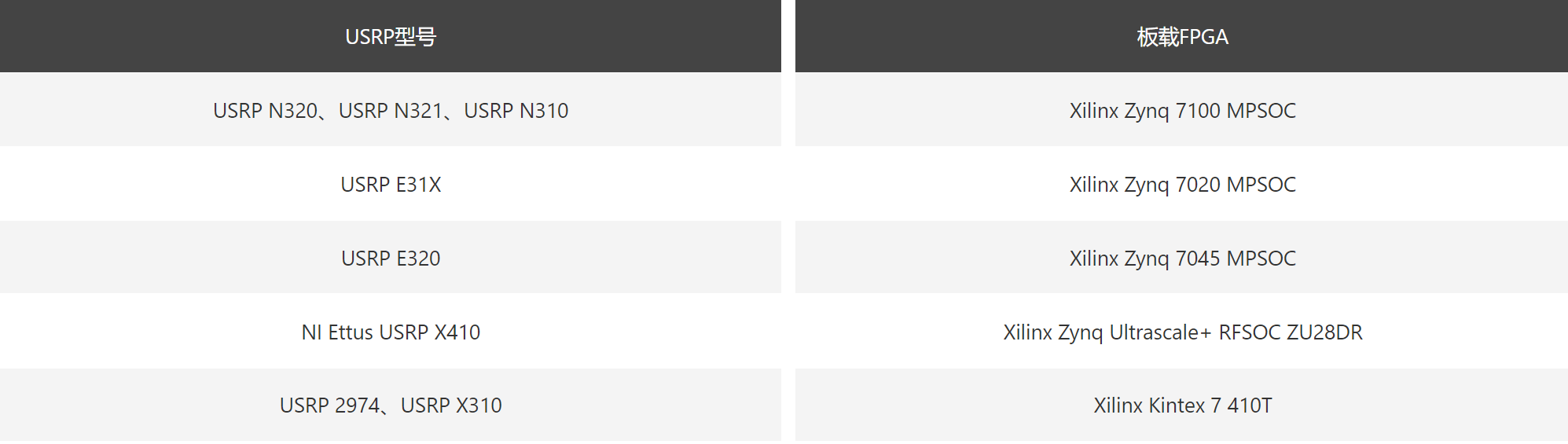

表1:搭載板載處理器的可獨(dú)立式USRP型號(hào)

有加固需求的嚴(yán)苛環(huán)境

盡管許多USRP用于實(shí)驗(yàn)室,但一些應(yīng)用需要在戶(hù)外或更嚴(yán)苛的環(huán)境下操作。如果您的應(yīng)用需要在更高的操作溫度下運(yùn)行,或者無(wú)法依靠氣冷系統(tǒng),您可以考慮為應(yīng)用使用Ettus Research品牌的嵌入式系列。此外,在Ettus Research品牌下,可以選擇配置USRP B205mini來(lái)適應(yīng)更高的溫度范圍,并使用工業(yè)級(jí)鋁制外殼組件,以實(shí)現(xiàn)低SWaP運(yùn)行。

多通道同步

許多應(yīng)用需要具有不同同步級(jí)別的多輸入多輸出(MIMO)配置。一些MIMO系統(tǒng)只需要共享時(shí)鐘來(lái)用于ADC和DAC;而其他系統(tǒng)則需要每個(gè)通道被鎖定到一個(gè)通用時(shí)鐘和本地振蕩器以實(shí)現(xiàn)全相位相干運(yùn)行。

常見(jiàn)的MIMO應(yīng)用適用于使用空間多路復(fù)用的通信。因?yàn)檫@只需要時(shí)鐘同步,大多數(shù)USRP有一個(gè)外部的10 MHz參考時(shí)鐘就足夠了。 有一款這樣的系統(tǒng)是由布里斯托大學(xué)和隆德大學(xué)合作打造的,他們使用基于SDR的大規(guī)模MIMO系統(tǒng)打破了無(wú)線(xiàn)頻譜效率的世界紀(jì)錄。 在此應(yīng)用中使用的大規(guī)模MIMO原型驗(yàn)證系統(tǒng)是由使用板載FPGA的NI USRP軟件無(wú)線(xiàn)電設(shè)備組成的。

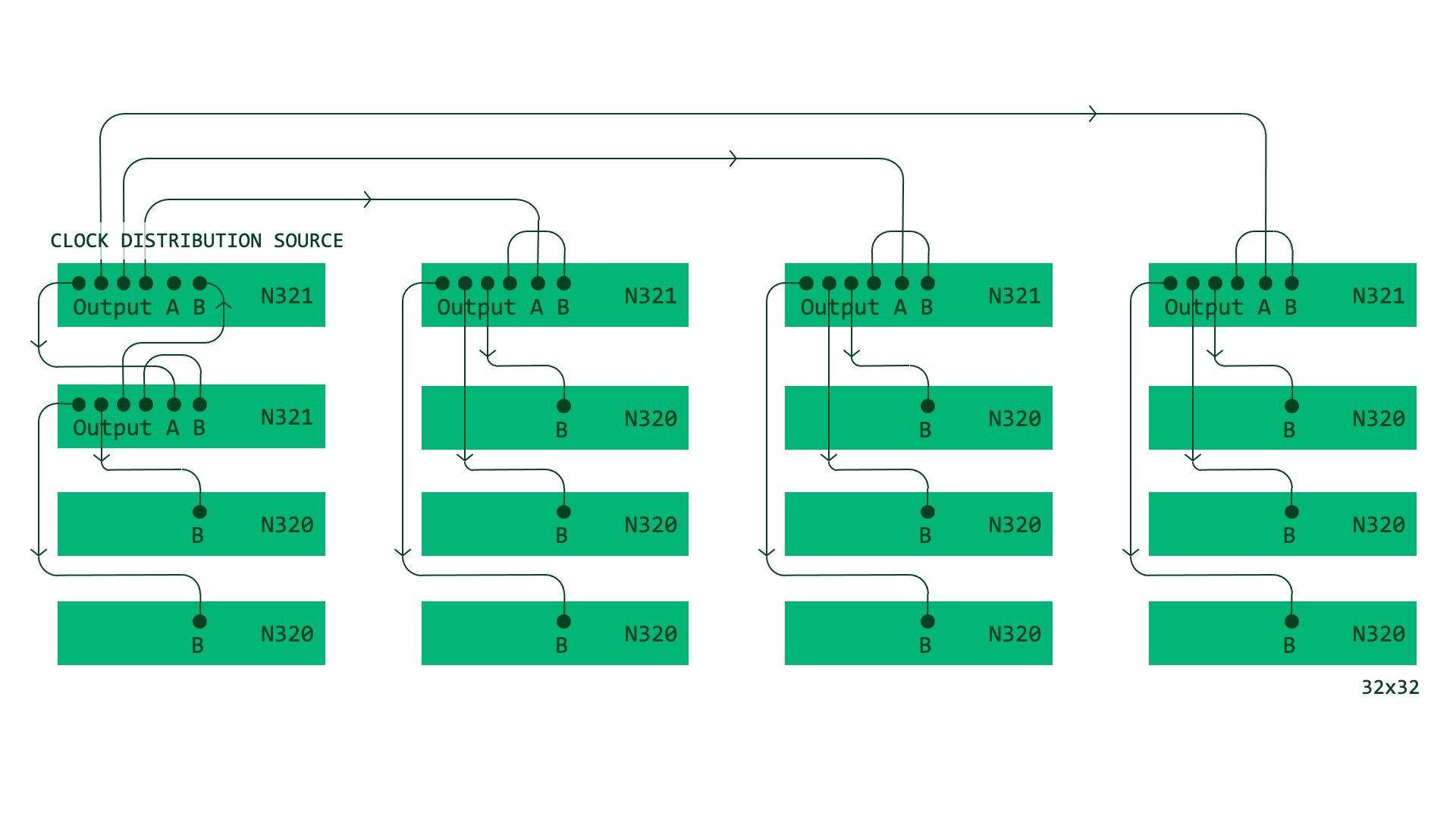

當(dāng)需要全相位相干運(yùn)行時(shí),您有兩種可以考慮的選擇。如果您需要最多四個(gè)通道的僅接收操作,具有兩個(gè)TwinRx子板的Ettus Research USRP X310可以設(shè)置為共享LO并以相位相干的方式運(yùn)行。如果需要超過(guò)四個(gè)通道,則可以考慮一下圖7中所示的Ettus Research USRP N320和N321。USRP N321配備了內(nèi)置LO分布硬件,允許最高128 x 128相位相干運(yùn)行:圖8顯示了一個(gè)32 x 32配置示例。

圖8:USRP N320和N321多通道相位相干系統(tǒng)

分布式多無(wú)線(xiàn)電同步

在一些應(yīng)用中,無(wú)線(xiàn)電需要同步,但它們并不位于一處。在這些情況下,全相位相干運(yùn)行是一項(xiàng)挑戰(zhàn);但是有了GPS馴服的振蕩器(GPSDO),可以通過(guò)基于GPS的同步獲取頻率和相位穩(wěn)定性。許多USRP型號(hào)出廠(chǎng)配備GPSDO。要了解更多信息,可查閱“利用NI USRP-293x軟件無(wú)線(xiàn)電實(shí)現(xiàn)全局同步和時(shí)鐘馴服。”

內(nèi)嵌信號(hào)處理和FPGA注意事項(xiàng)

有些應(yīng)用的處理要求最適合板載FPGA。這些應(yīng)用通常有寬信號(hào)帶寬或低/確定性延時(shí)需求。在這種情況下,挑選能夠?qū)PGA進(jìn)行編程的無(wú)線(xiàn)電很重要。許多USB和更低成本的USRP型號(hào),如USRP B200mini或N210,都是用更小的FPGA設(shè)備構(gòu)建的,因此沒(méi)有空間添加用戶(hù)代碼。許多更高端的無(wú)線(xiàn)電配備了Kintex 7類(lèi)設(shè)備,一直到基于Xilinx Zynq Ultrascale+ RFSOC的最先進(jìn)的NI Ettus USRP X410。基于Xilinx Zynq構(gòu)建的設(shè)備包含了更多內(nèi)核數(shù),例如板載SD-FEC、多臂處理器以及內(nèi)置ADC和DAC。

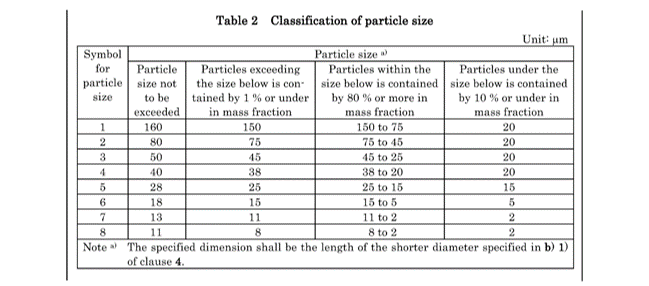

表2: 啟用FPGA的USRP的比較

軟件選項(xiàng)

可編程性是SDR的主要特征,它能讓人利用無(wú)線(xiàn)電外設(shè),并將其變?yōu)橐粋€(gè)先進(jìn)的無(wú)線(xiàn)系統(tǒng)。USRP是市面上最開(kāi)放和最通用的SDR,可幫助工程師使用各種軟件開(kāi)發(fā)工具基于主機(jī)和FPGA構(gòu)建系統(tǒng)。

主機(jī)編程注意事項(xiàng)

如上面圖2所示,有多種選項(xiàng)可以為基于SDR的系統(tǒng)的主機(jī)編程。

使用安裝了NI-USRP驅(qū)動(dòng)程序的LabVIEW進(jìn)行編程

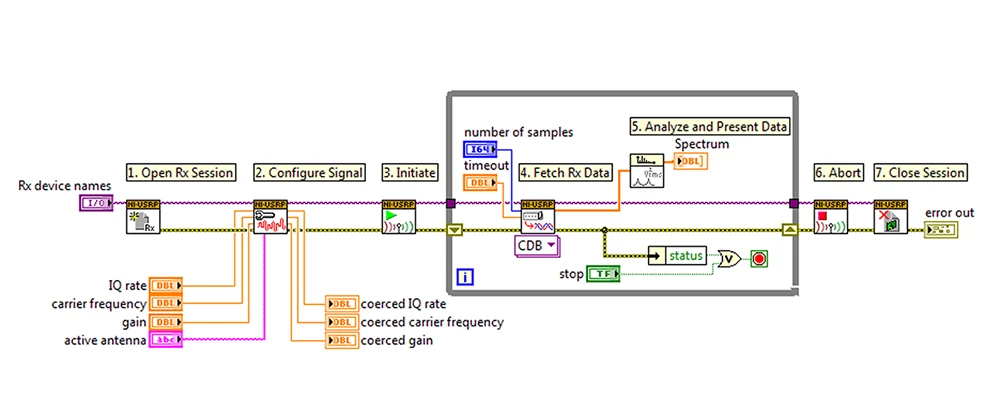

LabVIEW是圖形化的數(shù)據(jù)流編程環(huán)境,非常適合用于設(shè)計(jì)和實(shí)現(xiàn)通信算法。在最基本的層級(jí)上,LabVIEW使用NI-USRP驅(qū)動(dòng)程序來(lái)指定USRP硬件配置和收發(fā)正確格式化的基帶I/Q數(shù)據(jù),為主機(jī)端信號(hào)處理做好準(zhǔn)備。

如果LabVIEW是您首選的開(kāi)發(fā)環(huán)境,值得注意的是,盡管它確實(shí)提供一些基于Linux的操作系統(tǒng)支持,但它主要是一個(gè)基于Microsoft Windows的工具。此外,一些Ettus Research品牌的USRP型號(hào)和配置可能不受支持;可以參見(jiàn)下面的圖15。

圖11: 具有NI-USRP驅(qū)動(dòng)程序API的LabVIEW屏幕的結(jié)構(gòu)框圖

使用開(kāi)源工作流編程:USRP硬件驅(qū)動(dòng)程序(UHD)和GNU Radio

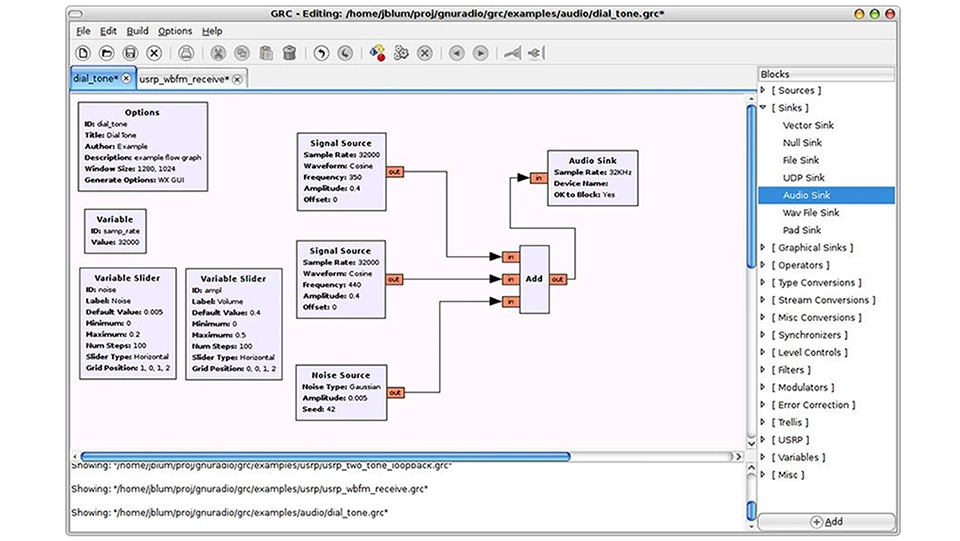

許多SDR用戶(hù)更喜歡使用基于C/C++和Python構(gòu)建的基于文本的開(kāi)源工具流來(lái)為USRP硬件編程。所有NI和Ettus Research USRP型號(hào)均支持USRP硬件驅(qū)動(dòng)程序(UHD),可輕松集成到開(kāi)源社區(qū)開(kāi)發(fā)的工具中,如GNU Radio。

GNU Radio是專(zhuān)為SDR開(kāi)發(fā)人員打造的開(kāi)源工具。雖然USRP不是GNU Radio支持的唯一無(wú)線(xiàn)電,但它是最受歡迎且經(jīng)過(guò)測(cè)試的。要了解更多關(guān)于GNU Radio的信息,請(qǐng)?jiān)L問(wèn)gnuradio.org,要查看所有現(xiàn)有社區(qū)共享的GNU Radio的IP,請(qǐng)?jiān)L問(wèn)cgran.org。

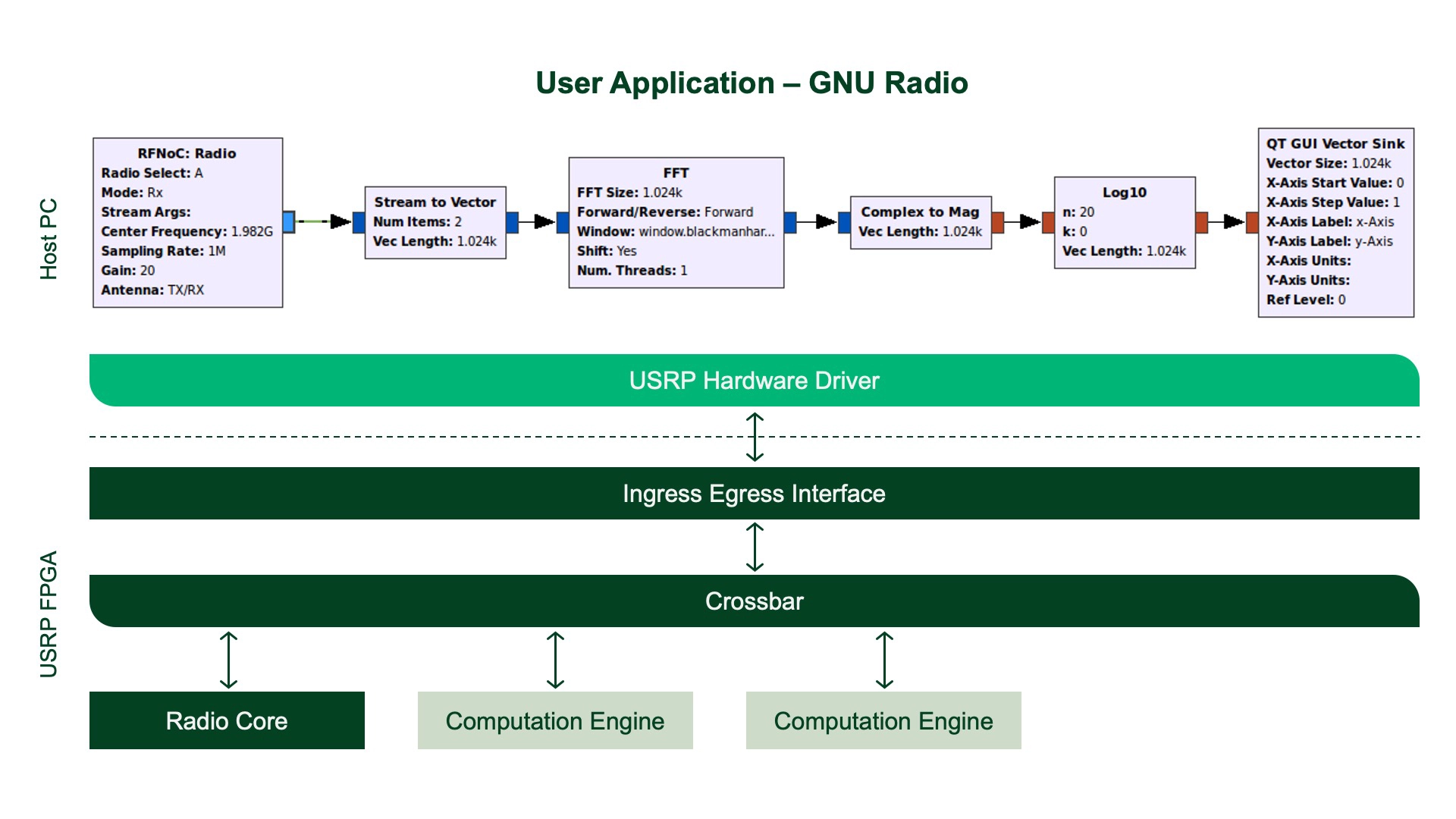

圖12:GNU Radio配套流程圖

使用MATLAB編程

如果MATLAB是您首選的編程工具,則MathWorks Communications Toolbox?可支持多個(gè)USRP型號(hào)。支持的型號(hào)包括B200、B200mini、X300、N200和N300系列。另外,工程師可以使用MATLAB腳本節(jié)點(diǎn)將MATLAB代碼直接嵌入LabVIEW中。

FPGA編程注意事項(xiàng)

許多USRP都配備了大型FPGA,有足夠的空閑容量,允許用戶(hù)嵌入特定于其應(yīng)用程序的內(nèi)聯(lián)信號(hào)處理。如硬件部分所述,一些USRP配備了Xilinx Zynq SOC設(shè)備,一些則配備了傳統(tǒng)的FPGA架構(gòu),如Kintex 7。可以通過(guò)兩種方法訪(fǎng)問(wèn)USRP上的FPGA:LabVIEW FPGA和片上射頻網(wǎng)絡(luò)(RFNoC)框架。

與許多FPGA開(kāi)發(fā)板或COTS FPGA板不同,USRP基于通用FPGA框架構(gòu)建,提供更高級(jí)的抽象能力。這消除了從基本FPGA板支持包構(gòu)建基于FPGA的系統(tǒng)時(shí)遇到的一些復(fù)雜性。

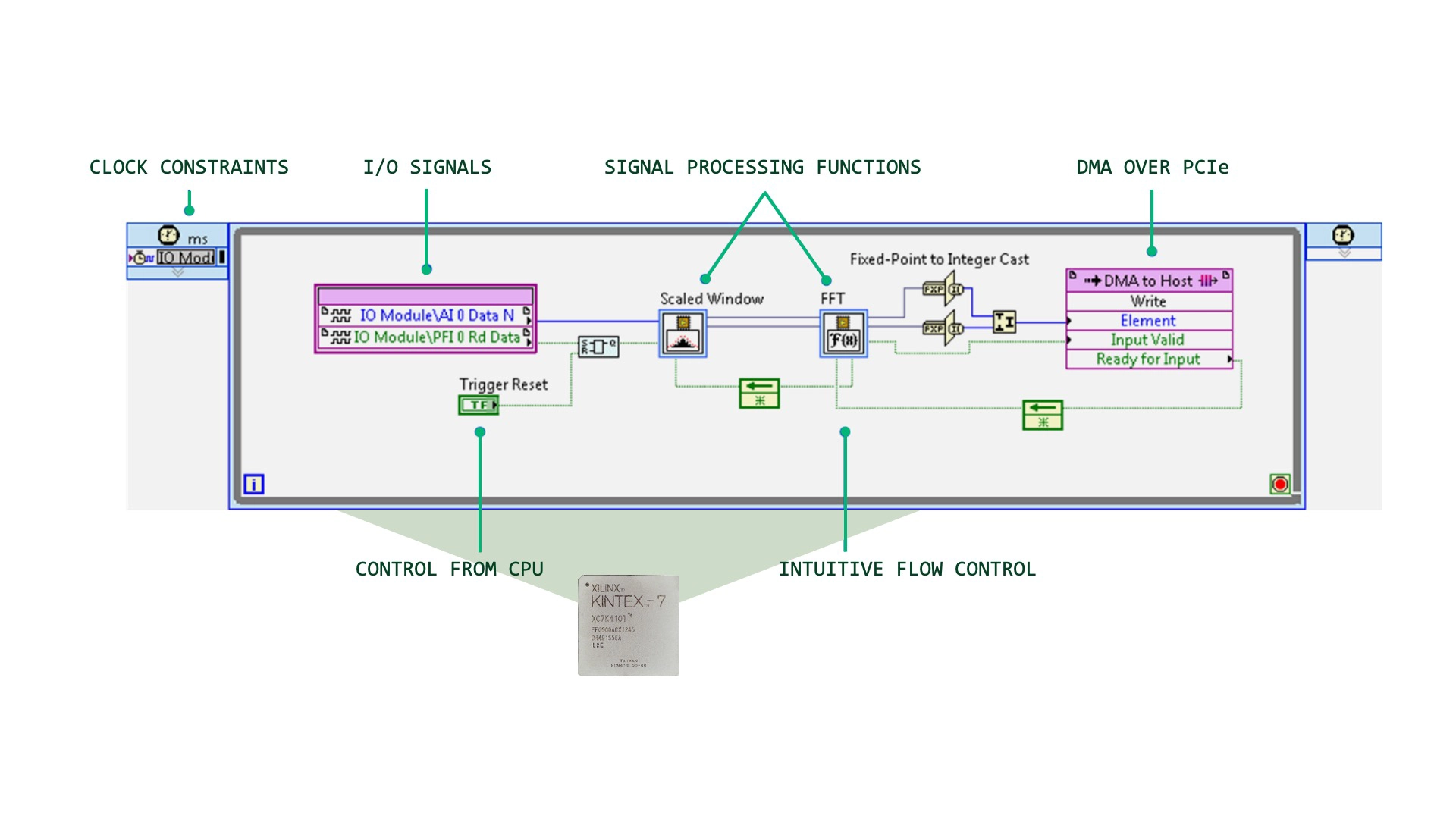

LabVIEW FPGA

LabVIEW FPGA是LabVIEW的附加擴(kuò)展模塊,支持在NI USRP RIO設(shè)備上為FPGA進(jìn)行圖形化編程。 雖然必須熟悉FPGA的概念,如定點(diǎn)數(shù)學(xué)和時(shí)鐘邏輯,但LabVIEW不僅可將硬件和數(shù)據(jù)接口抽象化,還可簡(jiǎn)化寄存器配置和數(shù)據(jù)移動(dòng)。LabVIEW FPGA的優(yōu)勢(shì)是能夠使用統(tǒng)一開(kāi)發(fā)工具鏈同時(shí)為主機(jī)和FPGA編程。

是否有想要利用的舊版IP?LabVIEW FPGA可以通過(guò)組件級(jí)IP(CLIP)節(jié)點(diǎn)導(dǎo)入外部VHDL或Verilog,允許導(dǎo)入非LabVIEW IP。此外,LabVIEW允許Xilinx Vivado項(xiàng)目導(dǎo)出,供專(zhuān)家用戶(hù)直接在Vivado工具內(nèi)使用。

如果LabVIEW FPGA是您選擇用于主機(jī)編程的工具,請(qǐng)注意,它僅限于在基于Windows的操作系統(tǒng)中使用。 許多Ettus Research設(shè)備在LabVIEW或LabVIEW FPGA下不受支持,例如USRP N300和USRP E300系列。請(qǐng)查看下方的圖15了解完整列表。

圖13:簡(jiǎn)單的LabVIEW FPGA結(jié)構(gòu)框圖

片上射頻網(wǎng)絡(luò)(RFNoC)框架

對(duì)于開(kāi)源USRP用戶(hù)而言,首選的FPGA編程方法是使用RFNoC框架。 LabVIEW FPGA等RFNoC是一種數(shù)據(jù)接口兼命令抽象框架,可簡(jiǎn)化將IP添加到USRP中的流程,而無(wú)需從頭重新構(gòu)建整個(gè)FPGA板支持包。顧名思義,數(shù)據(jù)作為壓縮報(bào)頭網(wǎng)絡(luò)包從無(wú)線(xiàn)電流經(jīng)FPGA。RFNoC框架的核心是一個(gè)交叉開(kāi)關(guān)矩陣接口,讓用戶(hù)只需將新IP導(dǎo)入交叉開(kāi)關(guān)矩陣,即可將數(shù)據(jù)路由到其他IP塊或讓數(shù)據(jù)傳入傳出主機(jī)。網(wǎng)絡(luò)交叉開(kāi)關(guān)矩陣設(shè)計(jì)降低了將數(shù)據(jù)和命令傳入傳出主機(jī)的復(fù)雜性。

如果您偏愛(ài)使用Vivado和RFNoC來(lái)為USRP的FPGA編程,請(qǐng)考慮為您的應(yīng)用使用USRP X300、USRP E300、USRP N300以及NI Ettus USRP X410系列。

圖14: 與GNU Radio集成的RFNoC概念結(jié)構(gòu)框圖

圖15:NI和Ettus Research USRP型號(hào)矩陣

結(jié)論

SDR是強(qiáng)大的無(wú)線(xiàn)研究、設(shè)計(jì)、原型驗(yàn)證和開(kāi)發(fā)工具。由于存在許多選項(xiàng),為應(yīng)用挑選合適的無(wú)線(xiàn)電需要考慮很多因素。然而,只要仔細(xì)評(píng)估本技術(shù)白皮書(shū)中列出的各種軟件和硬件因素,您一定能使用市場(chǎng)上最流行的開(kāi)放式SDR。

審核編輯:郭婷

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論