T1和E1發(fā)送波形:可編程部分

DS26518的寄存器從幅度和定時(shí)兩個(gè)方面給出了發(fā)射脈沖的調(diào)理。T1和E1發(fā)射脈沖可以分成幾個(gè)部分,每個(gè)部分都可以進(jìn)行調(diào)整以滿足波形要求。圖1所示為T1脈沖分區(qū),以及寄存器控制對(duì)這些分區(qū)的控制。圖2介紹了E1脈沖的分區(qū)及寄存器控制。T1和E1發(fā)送波形:幅度控制

DS26518發(fā)送脈沖的幅度控制可以用兩種方式實(shí)現(xiàn):- 調(diào)整DAC增益

利用L1TXLAE寄存器中DAC[3:0]可以同時(shí)對(duì)T1或E1中所有電平提供正向或負(fù)向調(diào)整。

- 部分波形電平調(diào)整

電平調(diào)整寄存器中的WLA[3:0]提供對(duì)特定波形區(qū)段的微調(diào),調(diào)整步進(jìn)值隨設(shè)定好的DAC增益變化。如果DAC增益提高10%,步進(jìn)值也相應(yīng)增加10%。

T1和E1發(fā)送波形:定時(shí)控制

DS26518發(fā)送脈沖電平的定時(shí)由幅度調(diào)整寄存器的CEA[2:0]控制,每個(gè)邊沿可以正向或負(fù)向調(diào)整1/32 TCLK。一般性建議

因?yàn)楦淖円粋€(gè)DAC增益寄存器就可以控制所有波形,所以控制發(fā)射脈沖幅度最簡(jiǎn)單的方法就是調(diào)整DAC的增益。首先調(diào)整DAC增益可以使寄存器調(diào)整量最小。VDD決定了DAC的最大輸出,如果VDD較低,將無法得到最大DAC增益。調(diào)整VDD也會(huì)影響線路驅(qū)動(dòng)輸出級(jí)的最大電壓。負(fù)數(shù)不用帶符號(hào)整數(shù)表示,最高位是符號(hào)位,低位代表幅度,與符號(hào)無關(guān)。例如,-3在WLA[3:0]寄存器中表示為1011b (第3位為1代表負(fù)數(shù),后面3位011是數(shù)值大小“3”),而不是1101b (4位帶符號(hào)整數(shù))。

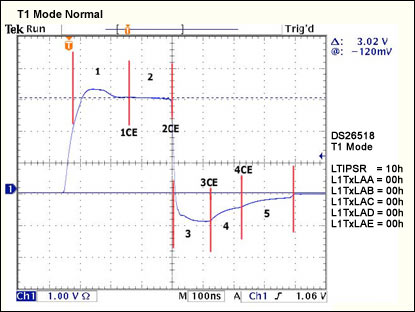

圖1. T1脈沖控制分區(qū)

T1脈沖控制分區(qū)

| Overshoot (1) | Register L1TXLAA WLA[4:0] |

| Clock Edge (1CE) | Register L1TXLAA CEA[2:0] |

| (1CE) = Clock Edge transition from Overshoot to Plateau | |

| Plateau (2) | Register L1TXLAB WLA[4:0] |

| Clock Edge (2CE) | Register L1TXLAB CEA[2:0] |

| (2CE) = Clock Edge transition from Plateau to Falling Edge | |

| Undershoot (3) | Register L1TXLAC WLA[4:0] |

| Clock Edge (3CE) | Register L1TXLAC CEA[2:0] |

| (3CE) = Clock Edge transition from Falling Edge to end of Undershoot (3) | |

| Undershoot (4) | Register L1TXLAD WLA[4:0] |

| Clock Edge (4CE) | Register L1TXLAD CEA[2:0] |

| (4CE) = Clock Edge transition from end of Undershoot (3) to end of Undershoot (4) | |

| Undershoot (5) | Register L1TXLAC WLA[4:0] |

圖2. E1脈沖控制分區(qū)

E1脈沖控制分區(qū)

| Overshoot (1) | Register L1TXLAA WLA[4:0] |

| Clock Edge (1CE) | Register L1TXLAA CEA[2:0] |

| (1CE) = Clock Edge transition from Overshoot to Plateau | |

| Plateau (2) | Register L1TXLAB WLA[4:0] |

| Clock Edge (2CE) | Register L1TXLAB CEA[2:0] |

| (2CE) = Clock Edge transition from Plateau to Falling Edge | |

注意:寄存器L1TXAC、L1TXAD和L1TXAE在E1模式中沒有使用。

LIU測(cè)試寄存器說明

表1給出了LIU 1的寄存器地址和說明,LIU 2至8的說明與LIU 1相同。表2給出了全部LIU測(cè)試寄存器的地址。

表1. LIU 1測(cè)試寄存器

| Address | Abbr. | Description |

| 1011h | L1TXLAA | LIU 1 Tx Level Adjust A (Test Register) |

| 1012h | L1TXLAB | LIU 1 Tx Level Adjust B (Test Register) |

| 1013h | L1TXLAC | LIU 1 Tx Level Adjust C (Test Register) |

| 1014h | L1TXLAD | LIU 1 Tx Level Adjust D (Test Register) |

| 1015h | L1TXLAE | LIU 1 Tx Level Adjust E (Test Register) |

表2. LIU測(cè)試寄存器地址

| LIU | Address Range |

| 1 | 1011–1015h |

| 2 | 1031–1035h |

| 3 | 1051–1055h |

| 4 | 1071–1075h |

| 5 | 1091–1095h |

| 6 | 10B1–10B5h |

| 7 | 10D1–10D5h |

| 8 | 10F1–10F5h |

LIU測(cè)試寄存器詳細(xì)說明

LIU 1的寄存器地址和說明如下,LIU 2至8的說明與LIU 1相同。| Register Name | L1TXLAA |

| Register Description | LIU Tx Level Adjust A (Overshoot Voltage) |

| Register Address | 1011H |

| Read/Write Function | R/W |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

第7位至第3位:發(fā)送波形輸出電平1調(diào)整(WLA[4:0])

從默認(rèn)的±360mV調(diào)整幅度。

第7位 = 符號(hào)位(“1”表示負(fù)數(shù))

第6位至第3位 = 數(shù)值(無符號(hào)),LSB步長為20mV

第2位至第0位:時(shí)鐘沿調(diào)整(CEA[2:0])

從默認(rèn)的±3 32個(gè)時(shí)鐘移動(dòng)時(shí)鐘沿。

<2> = 符號(hào)位(“1”表示負(fù)數(shù))

<1:0> = 時(shí)鐘沿移動(dòng)32個(gè)時(shí)鐘的倍數(shù)(無符號(hào))

| Register Name | L1TXLAB |

| Register Description | LIU Tx Level Adjust B (Plateau Voltage) |

| Register Address | 1012H |

| Read/Write Function | R/W |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

第7位至第3位:發(fā)送波形輸出電平2調(diào)整(WLA[4:0])

從默認(rèn)的±360mV調(diào)整幅度。

第7位 = 符號(hào)位(“1”表示負(fù)數(shù))

第6位至第3位 = 數(shù)值(無符號(hào)),LSB步長為20mV。

第2位至第0位:時(shí)鐘沿調(diào)整(CEA[2:0])

從默認(rèn)的±3 32個(gè)時(shí)鐘移動(dòng)時(shí)鐘沿。

<2> = 符號(hào)位(“1”表示負(fù)數(shù))

<1:0> = 時(shí)鐘沿移動(dòng)32個(gè)時(shí)鐘的倍數(shù)(無符號(hào))

| Register Name | L1TXLAB |

| Register Description | LIU Tx Level Adjust B (Plateau Voltage) |

| Register Address | 1012H |

| Read/Write Function | R/W |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

第7位至第3位:發(fā)送波形輸出電平3調(diào)整(WLA[4:0])

從默認(rèn)的±360mV調(diào)整幅度。

第7位 = 符號(hào)位(“1”表示負(fù)數(shù))

第6位至第3位 = 數(shù)值(無符號(hào)),LSB步長為20mV

第2位至第0位:時(shí)鐘沿調(diào)整(CEA[2:0])

從默認(rèn)的±3 32個(gè)時(shí)鐘移動(dòng)時(shí)鐘沿。

<2> = 符號(hào)位(“1”表示負(fù)數(shù))

<1:0> = 時(shí)鐘沿移動(dòng)32個(gè)時(shí)鐘的倍數(shù)(無符號(hào))

| Register Name | L1TXLAC |

| Register Description | LIU Tx Level Adjust C (Undershoot Voltage) |

| Register Address | 1013H |

| Read/Write Function | R/W |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

第7位至第3位:發(fā)送波形輸出電平4調(diào)整(WLA[4:0])

從默認(rèn)的±360mV調(diào)整幅度。

第7位 = 符號(hào)位(“1”為負(fù)數(shù))

第6位至第3位 = 數(shù)值大小(無符號(hào)),LSB步長為20mV

第2位至第0位:時(shí)鐘沿調(diào)整(CEA[2:0])

從默認(rèn)的±3 32個(gè)時(shí)鐘移動(dòng)時(shí)鐘沿。

<2> = 符號(hào)位(“1”表示負(fù)數(shù))

<1:0> = 時(shí)鐘沿移動(dòng)32個(gè)時(shí)鐘的倍數(shù)(無符號(hào))

| Register Name | L1TXLAE |

| Register Description | LIU Tx Level Adjust E (Undershoot Voltage #3) |

| Register Address | 1015H |

| Read/Write Function | R/W |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

第7位至第4位:輸出波形電平5調(diào)整(WLA[3:0])

從默認(rèn)的±180mV調(diào)整幅度。

第7位 = 符號(hào)位(“1”表示負(fù)數(shù))

第6位至第4位 = 數(shù)值(無符號(hào)),LSB步長為20mV

第3位至第0位:DAC增益調(diào)整(DAC[3:0])。

以下設(shè)置修改DAC增益。

| DAC[3:0] | DAC Gain Value |

| 0000 | Nominal (default) |

| 0001 | +2.67% |

| 0010 | +5.34% |

| 0011 | +8.67% |

| 0100 | +11.34% |

| 0101 | +14.0% |

| 0110 | +17.34% |

| 0111 | +20.97% |

| 1000 | -2.1% |

| 1001 | -4.0% |

| 1010 | -6.0% |

| 1011 | -8.0% |

| 1100 | -10.0% |

| 1101 | -12.0% |

| 1110 | -14.0% |

| 1111 | -15.34% |

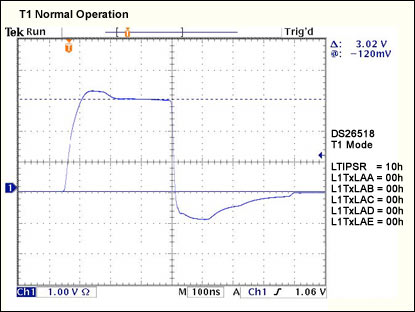

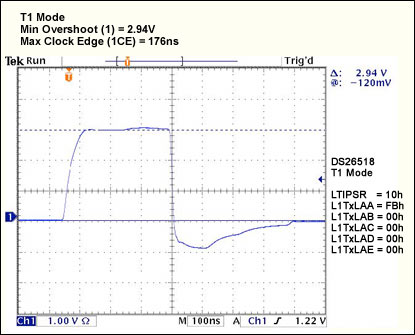

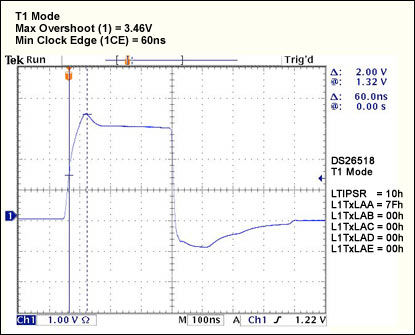

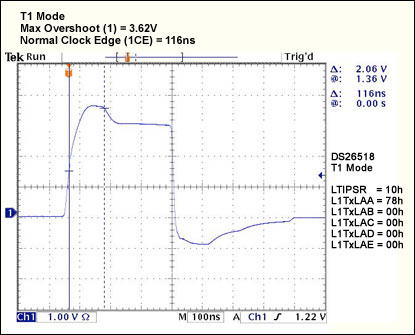

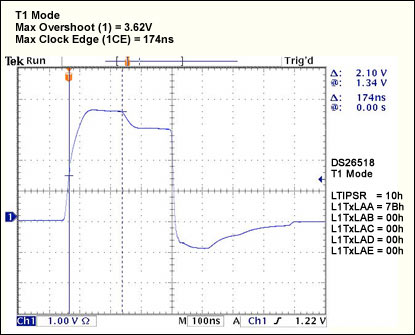

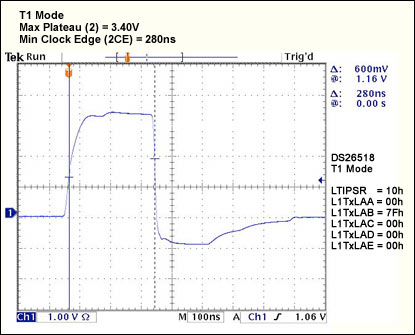

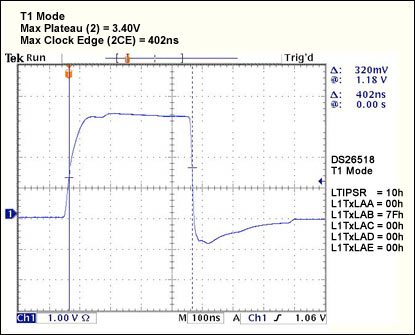

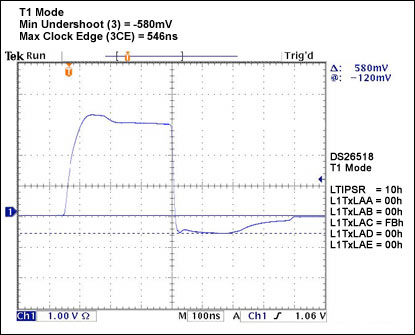

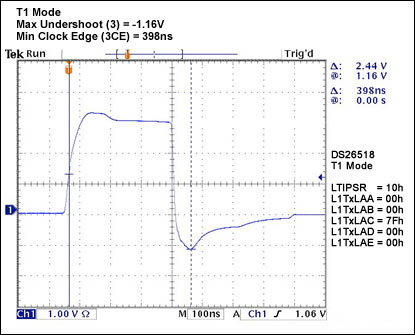

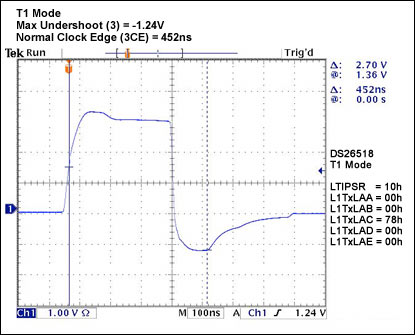

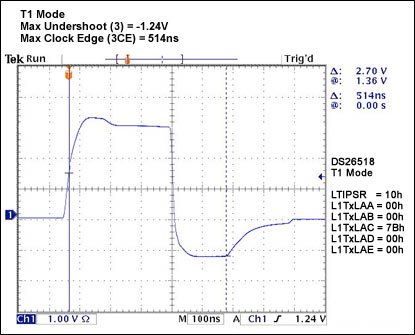

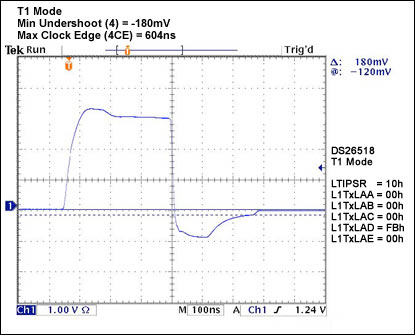

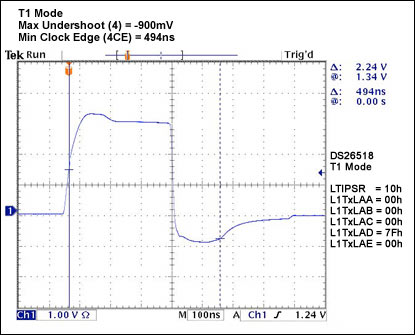

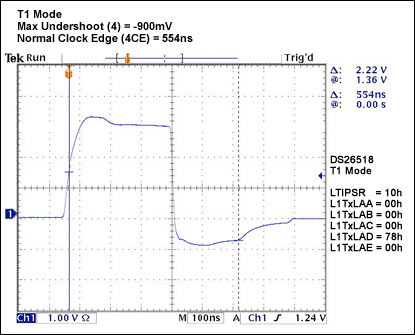

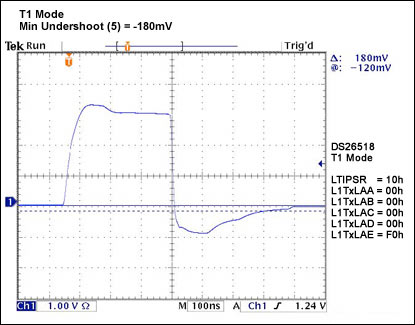

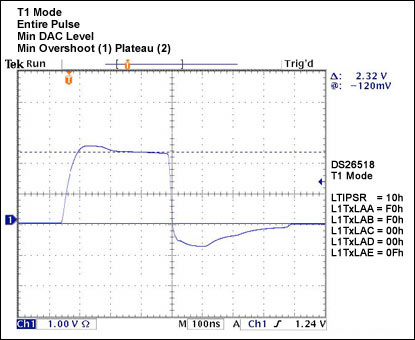

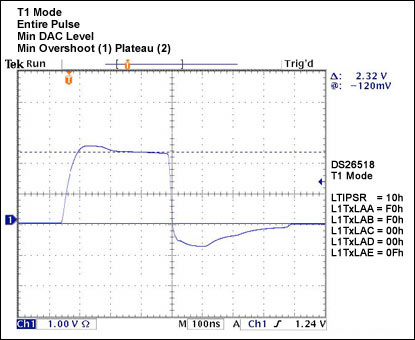

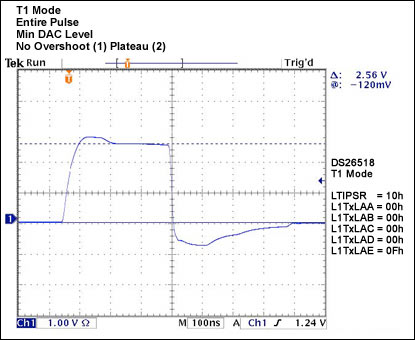

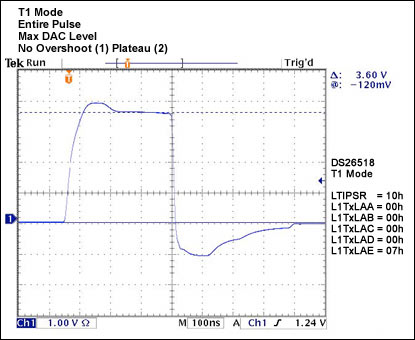

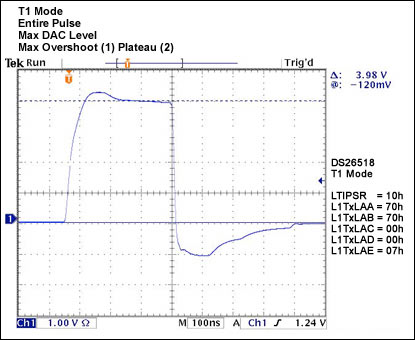

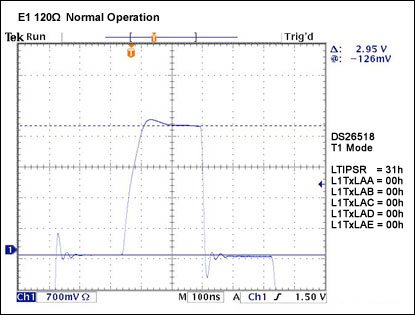

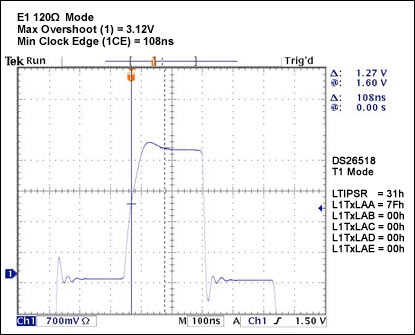

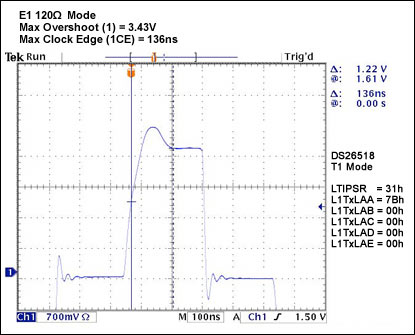

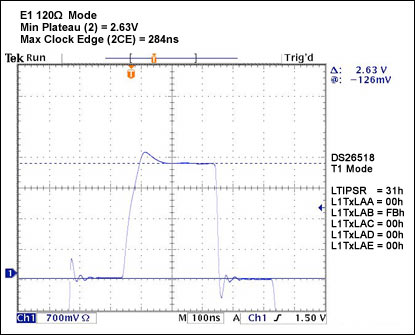

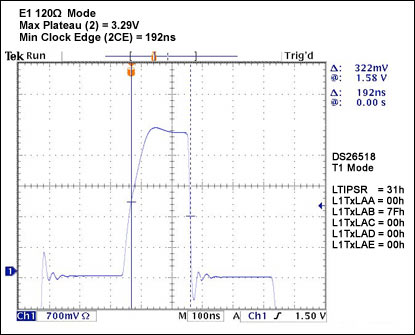

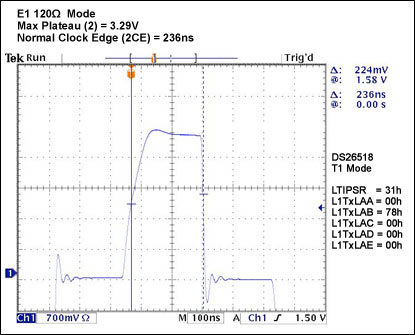

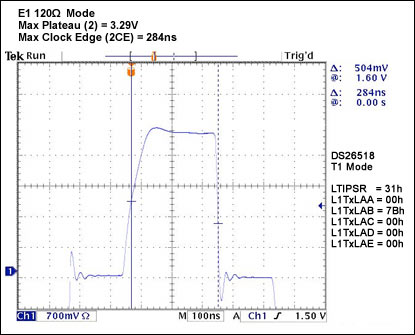

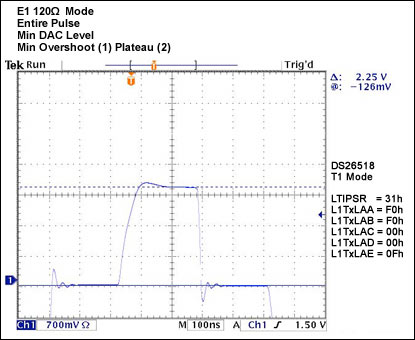

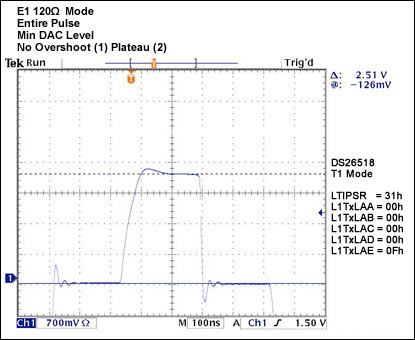

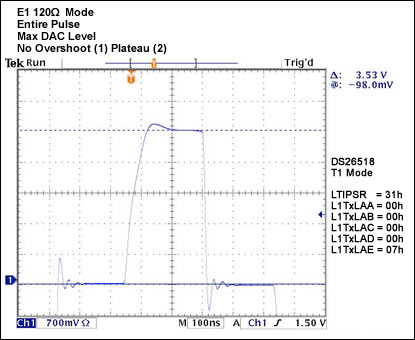

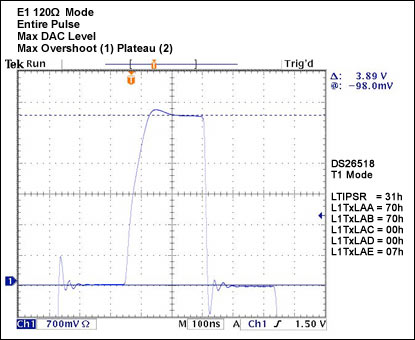

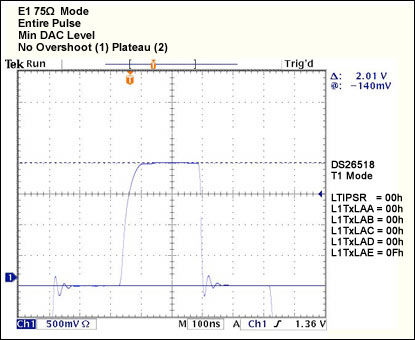

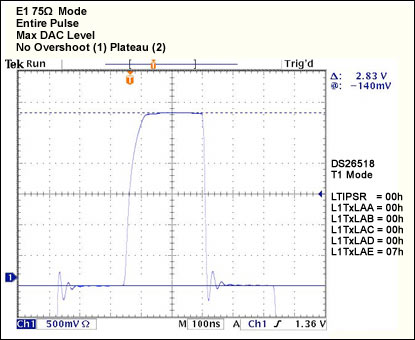

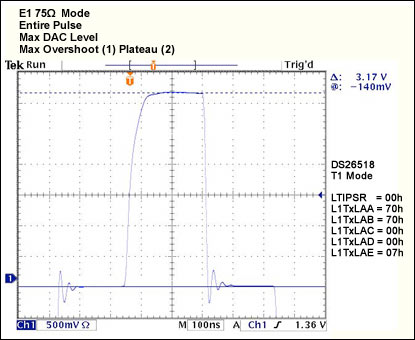

T1和E1發(fā)送波形數(shù)據(jù)

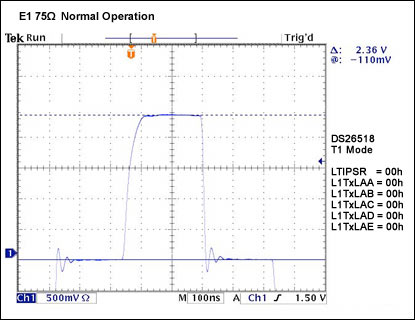

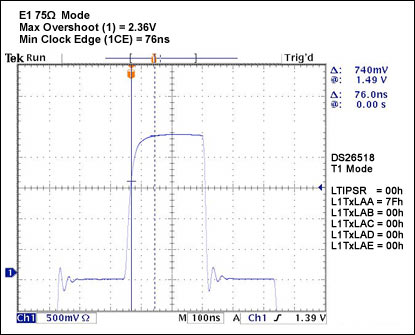

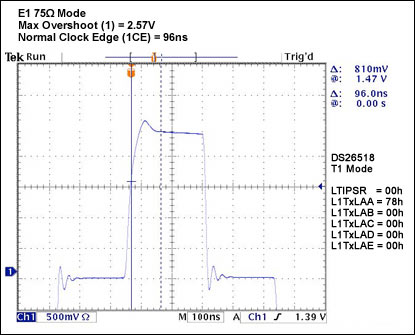

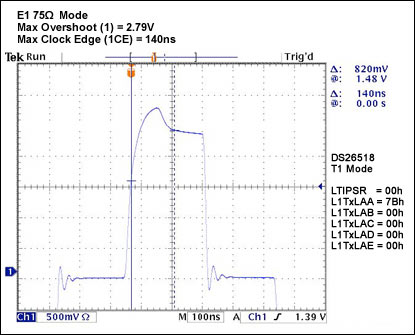

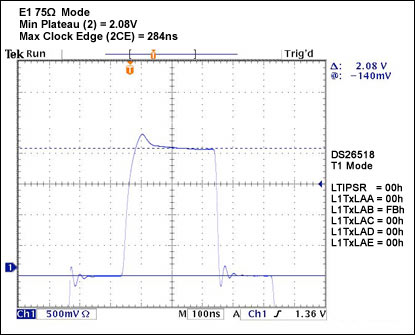

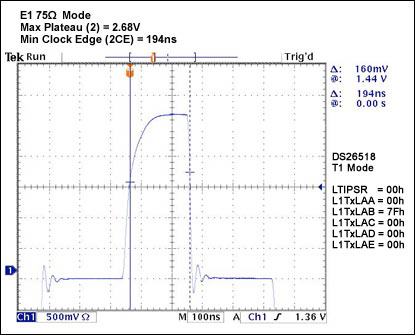

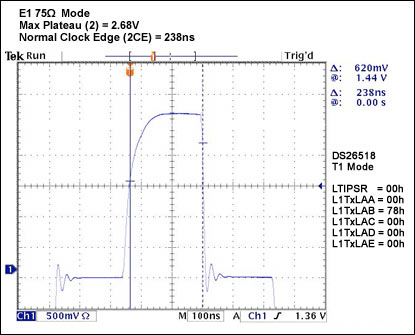

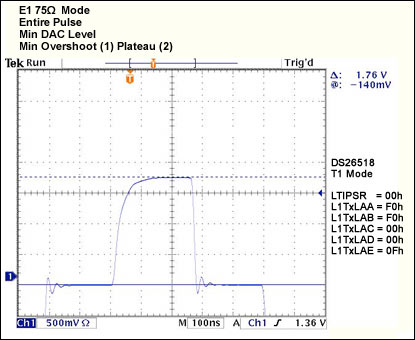

以下數(shù)據(jù)為DS26518的典型測(cè)試結(jié)果,這些數(shù)據(jù)僅供參考,幫助設(shè)計(jì)者了解如何利用電平調(diào)整寄存器,控制T1和E1發(fā)送脈沖的幅度和定時(shí),并可控制調(diào)整范圍。這些數(shù)據(jù)是在室溫、3.3V VDD條件下測(cè)試得到的。

圖3.

圖4.

圖5.

圖6.

圖7.

圖8.

圖9.

圖10.

圖11.

圖12.

圖13.

圖14.

圖15.

圖16.

圖17.

圖18.

圖19.

圖20.

圖21.

圖22.

圖23.

圖24.

圖25.

圖26.

圖27.

圖28.

圖29.

圖30.

圖31.

圖32.

圖33.

圖34.

圖35.

圖36.

圖37.

圖38.

圖39.

圖40.

圖41.

圖42.

圖43.

圖44.

圖45.

圖46.

圖47.

圖48.

圖49.

圖50.

圖51.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論