作者:韓佳巍??光啟智能研究院

摘要

GPU加速的計(jì)算系統(tǒng)可為諸多科學(xué)應(yīng)用提供強(qiáng)大的計(jì)算能力支撐,亦是業(yè)界推動(dòng)人工智能革命的重要手段。為了滿足大規(guī)模數(shù)據(jù)中心和高性能計(jì)算場景的帶寬拓展需求,光通信和光互連技術(shù)正在迅速而廣泛地滲入此類系統(tǒng)的各個(gè)網(wǎng)絡(luò)或鏈路層級(jí)。作為系列文章的第二篇,本文試圖對(duì)GPU網(wǎng)絡(luò)中光互連的光通信技術(shù)選項(xiàng)和長期技術(shù)需求做出簡要分析。

在前篇“面向GPU網(wǎng)絡(luò)的光互連(1):房間里有兩頭大象?”中,我們對(duì)GPU網(wǎng)絡(luò)中光互連的歷史趨勢(shì)、短期的需求和權(quán)衡做出了簡要梳理。在本篇中,讀者不妨以一個(gè)隨意涉獵者的身份、興之所至地由筆者繼續(xù)引導(dǎo),將GPU網(wǎng)絡(luò)中光互連的光通信技術(shù)、長期的技術(shù)需求等方面瀏覽一番。

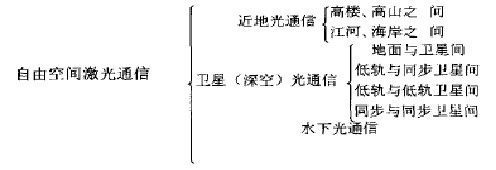

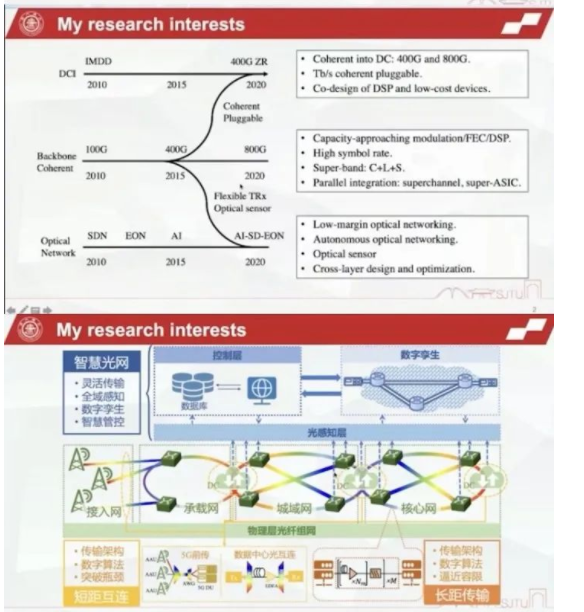

01光通信的群星閃耀時(shí)

面對(duì)多GPU互連的高性能計(jì)算(High-Performance Computing, HPC)系統(tǒng),本節(jié)嘗試將具有高度適用性的若干種光通信技術(shù)選項(xiàng)做出“點(diǎn)到為止”的概要性描述。這樣做,雖說是緣于筆者自身學(xué)養(yǎng)和全文篇幅的限制,但同時(shí)也有不妨礙讀者自己去進(jìn)一步深入閱讀相關(guān)文獻(xiàn)資料的好處。

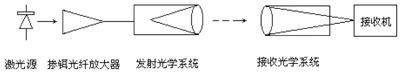

1.1垂直腔面發(fā)射激光器光纖鏈路技術(shù)

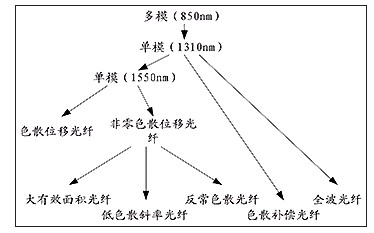

從歷史上來看,應(yīng)用于數(shù)據(jù)通信或計(jì)算機(jī)通信的低成本光互連是建立在垂直腔面發(fā)射激光器(Vertical-Cavity Surface-Emitting Laser, VCSEL)和多模光纖的技術(shù)基礎(chǔ)之上的[1]。VCSEL采用布拉格反射鏡作為激光腔的腔鏡,其橫向結(jié)構(gòu)通常為圓形對(duì)稱,輸出光束也為圓形對(duì)稱,可與多模光纖實(shí)現(xiàn)高效耦合。尤為值得一提的是,機(jī)架到機(jī)架的集群互連結(jié)構(gòu)便是廣泛采用了基于上述技術(shù)的并行光模塊。區(qū)別于電信場景中被廣泛使用的單模技術(shù),多模技術(shù)具有相對(duì)更為寬松的對(duì)準(zhǔn)公差。相較于邊發(fā)射單模激光器,多模VCSEL為人們測試光源提供了一個(gè)更為簡單且便宜的方案;同時(shí),多模VCSEL容易實(shí)現(xiàn)二維陣列集成,亦在功率效率方面具備明顯優(yōu)勢(shì)。因此,雖然多模光纖的傳輸距離(通常在100米至數(shù)百米范圍內(nèi),且隨著數(shù)據(jù)速率的增大而減小)受限于不同模式之間的路徑差異,但它依然是短距離數(shù)據(jù)通信和計(jì)算機(jī)通信的重要媒介。

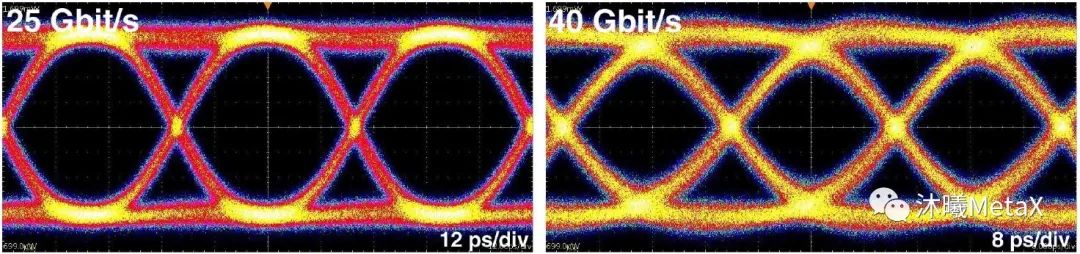

圖1. ?工作于25 Gbit/s和40 Gbit/s的高速原型VCSEL發(fā)射眼圖

(來源于參考資料[2])

盡管VCSEL光纖鏈路技術(shù)占據(jù)著最為龐大的互連市場份額,且已經(jīng)具備了低成本的制造基礎(chǔ)設(shè)施,但是其改進(jìn)空間仍然十分廣闊。當(dāng)前,許多中國大陸的VCSEL供應(yīng)商已可高標(biāo)準(zhǔn)地實(shí)現(xiàn)適用于100 Gbit/s以太網(wǎng)的25 Gbit/s非歸零碼VCSEL光纖鏈路技術(shù)(4×25 Gbit/s并行光路)。圖1為實(shí)驗(yàn)室實(shí)例演示中工作于25 Gbit/s和40 Gbit/s的VCSEL發(fā)射眼圖[2]。為了充分滿足數(shù)據(jù)中心或HPC系統(tǒng)中的光互連對(duì)于VCSEL鏈路的大量需求,人們正對(duì)高速率VCSEL的大規(guī)模制造方案做出廣泛討論和嘗試。

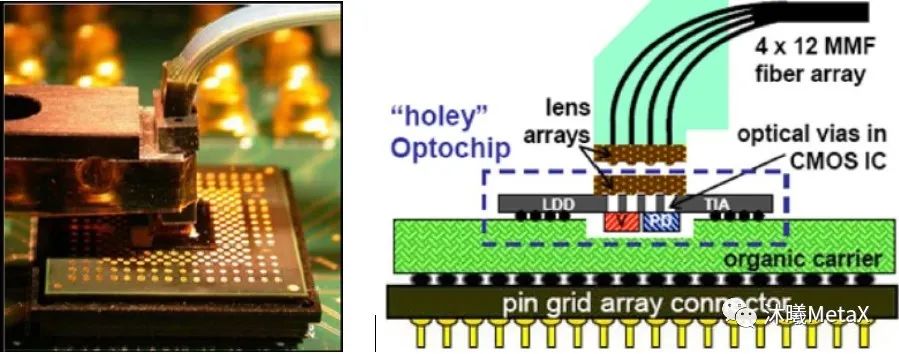

圖2. ?高密度光互連收發(fā)器制作原型

(來源于參考資料[3])

VCSEL光纖鏈路技術(shù)也正在向著更高速率、更低成本、更小功耗和更緊湊模塊的方向繼續(xù)演進(jìn)。圖2展示了一種高度緊湊的光模塊制作原型。該模塊采用倒裝芯片方式,將VCSEL陣列和光電二極管陣列附著在一個(gè)具有“光通孔”(硅基底中的孔洞)的CMOS芯片上,從而實(shí)現(xiàn)與一組多模光纖陣列的耦合。該光模塊在實(shí)現(xiàn)300 Gbit/s(24×12.5 Gbit/s)的同時(shí),可以達(dá)到的功耗和帶寬密度分別是8.2 pJ/bit和1 Tbps/cm2。

雖然VCSEL光纖鏈路長期以來(自1998年1 GbE被采用開始)是以850 nm作為標(biāo)準(zhǔn)波長的,但是人們對(duì)最佳波長的爭論卻一直在持續(xù)[4]。近幾年,在使用鋁鎵砷和銦鎵砷合金的基礎(chǔ)上,處于900-1100 nm波段范圍的長波長再次引起了學(xué)界和業(yè)界的廣泛興趣。該現(xiàn)象的促進(jìn)因素包括:潛在的速率、效能和可靠性的提升,背發(fā)射VCSEL的制作(砷化鎵基底在長波段范圍內(nèi)有著高度無損透明性,更適用于新型封裝)更加簡便,低成本粗波分復(fù)用收發(fā)器的使用,光電探測器在長波段范圍內(nèi)的響應(yīng)度略有優(yōu)勢(shì)(每單位光功率可生成較大電流),以及長波長對(duì)人眼更為安全等[5]。然而,由于損耗在長波段范圍內(nèi)相對(duì)較大,這類長波長在搭配塑料光纖使用時(shí)卻反倒具有一些劣勢(shì)(如下文1.2部分所述)。

上述長波長VCSEL光纖鏈路在功率變換效率和可靠性方面均取得了長足進(jìn)步。然而,人們又繼而發(fā)現(xiàn),在給定VCSEL結(jié)構(gòu)的條件下,VCSEL的失效機(jī)制在整個(gè)780-910 nm波段范圍內(nèi)并無顯著差別[6]。與此同時(shí),學(xué)界和業(yè)界對(duì)于850 nm光器件的研發(fā)也有著不俗表現(xiàn):僅以25-50 Gbit/s VCSEL為例,其功率損耗已經(jīng)能夠小于100 fJ/bit [7]。

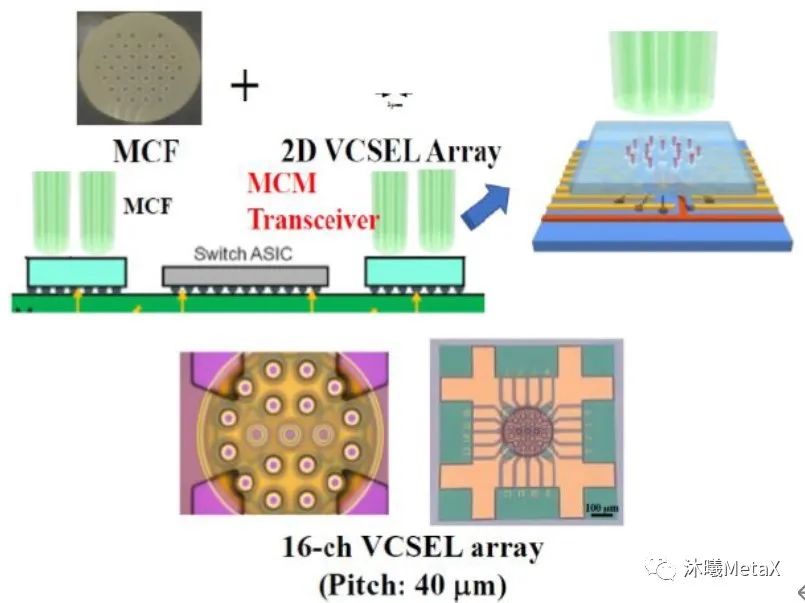

圖3. ?采用多芯多模光纖的光收發(fā)器原型

(來源于參考資料[8])

為了進(jìn)一步降低VCSEL光纖鏈路的總體成本,人們?cè)诳紤]如何減小光電收發(fā)器成本的同時(shí),也有必要采取措施來降低諸如光纖連接器、光纜、光纖管理等組件的成本。雖然更高的數(shù)據(jù)速率可在一定程度上降低鏈路成本,但是這還不足以應(yīng)對(duì)當(dāng)前的帶寬密度挑戰(zhàn)。一種方法是在一根光纖中擯棄使用單個(gè)多模纖芯、而是使用多個(gè)多模纖芯,從而實(shí)現(xiàn)更為顯著的數(shù)據(jù)速率提升[8]。如圖3所示,近期,日本國家情報(bào)通信研究機(jī)構(gòu)(NICT)在一根37芯光纖中采用了16芯作為空間信道與VCSEL陣列相匹配;而在使用800-1100 nm范圍內(nèi)多個(gè)波長的基礎(chǔ)上,粗波分復(fù)用收發(fā)器更是可以進(jìn)一步增加單根光纖的帶寬。最為關(guān)鍵的是,雖然上述方法或?qū)⑹芟抻诜庋b集成的異質(zhì)性特征和迅猛增加的光纖管理成本,但是目前以IBM、Nokia Bell Labs為代表的許多業(yè)界機(jī)構(gòu)都認(rèn)為它有著非常廣闊的探索和改進(jìn)空間[9, 10]。

1.2垂直腔面發(fā)射激光器光學(xué)印刷電路板技術(shù)

為了在封裝集成的程度和成本方面獲得更多收效,并在板卡距離互連場景中與銅線開展充分競爭,人們還將目光投向了基于塑料波導(dǎo)和VCSEL集成的光學(xué)印刷電路板(Printed Circuit Board, PCB)技術(shù)[11],認(rèn)為它可將低成本制造、模塊密度、可定制化集成等多個(gè)優(yōu)點(diǎn)匯集于一身。

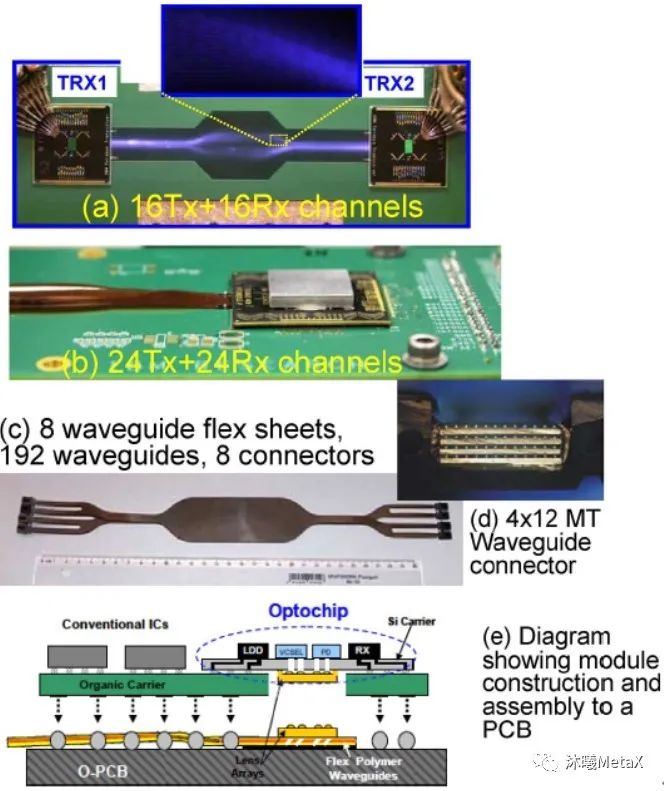

圖4. ?(a) PCB基底之上的塑料波導(dǎo),

適用于16個(gè)發(fā)射機(jī)、16個(gè)接收機(jī)信道的狀況;

(b)柔性基底之上的塑料波導(dǎo),適用于24個(gè)發(fā)射機(jī)、

24個(gè)接收機(jī)信道的狀況;(c)無源混洗電纜;

(d)四層波導(dǎo)連接器;(e)光模塊結(jié)構(gòu)和組裝的示意圖

(來源于參考資料[12])

VCSEL光學(xué)PCB技術(shù)的各個(gè)組成部分如圖4所示,具體包括:(a)在PCB上直接制作而成的塑料波導(dǎo),(b)柔性基底上的塑料波導(dǎo),(c)無源混洗電纜,(d)連接器。圖4(e)展示了于圖4(b)中所使用的光模塊結(jié)構(gòu)。VCSEL/光電二極管陣列和硅基驅(qū)動(dòng)/接收端電路被焊接于一體,并附著在一個(gè)硅基載板之上。硅基載板上的孔洞使得光束可以通過,而光路則是通過一個(gè)雙透鏡系統(tǒng)耦合入波導(dǎo)的。對(duì)于將光模塊附著在PCB這一步驟來說,雖然每個(gè)透鏡陣列需要在各自的對(duì)應(yīng)邊緣以更小容差(約為5 μm)附著在光組件上,但是上述雙透鏡系統(tǒng)仍可具備較大的偏調(diào)容差(1 dB損耗時(shí)大于20 μm)。

VCSEL光學(xué)PCB技術(shù)不僅為光互連輔以一種嶄新的光學(xué)手段,而且兼?zhèn)潆妼W(xué)PCB的技術(shù)特點(diǎn)。事實(shí)上,電學(xué)PCB仍舊基于低成本大批量制造方法,尚不具備面向特定用戶需求的可定制化特征。而光學(xué)PCB可將板卡之內(nèi)的光纖管理問題消弭于無形,并有利于實(shí)現(xiàn)物理接近GPU等處理芯片的高密度光收發(fā)器集成。為了進(jìn)一步推動(dòng)VCSEL光學(xué)PCB技術(shù)的應(yīng)用,人們一直嘗試去實(shí)現(xiàn)柔性基底組裝件之上的可替換波導(dǎo),并將該組裝件安裝在板上(與光纖并帶類似)。然而,隨著該項(xiàng)技術(shù)的不斷成熟,塑料波導(dǎo)將會(huì)被合并于PCB上方或內(nèi)部。盡管該項(xiàng)技術(shù)前景廣闊,但是人們?nèi)孕杩朔T多挑戰(zhàn),如進(jìn)一步改進(jìn)波導(dǎo)損耗和連接器損耗、實(shí)際實(shí)現(xiàn)相關(guān)的基礎(chǔ)制作設(shè)備等。

1.3硅基光子技術(shù)

自上世紀(jì)80年代中期開始,硅基光子便被廣泛認(rèn)為是光通信領(lǐng)域中最具前景的技術(shù)之一[13]。該技術(shù)將單模光纖、未經(jīng)調(diào)制的激光器、硅基調(diào)制器、硅基探測器等結(jié)合在一起使用;通過借助完善的CMOS制造來生產(chǎn)高度集成的裝配組件。硅基光子技術(shù)能以較低成本在CMOS中直接制造大部分原件,或可為光電集成能力提供最佳解決方案[14]。此外,通過大幅降低相關(guān)波分復(fù)用系統(tǒng)(即在同一光纖中傳輸多個(gè)波長)的成本,光纜和連接器的成本便可由更高的單光纖帶寬來分?jǐn)偂?/p>

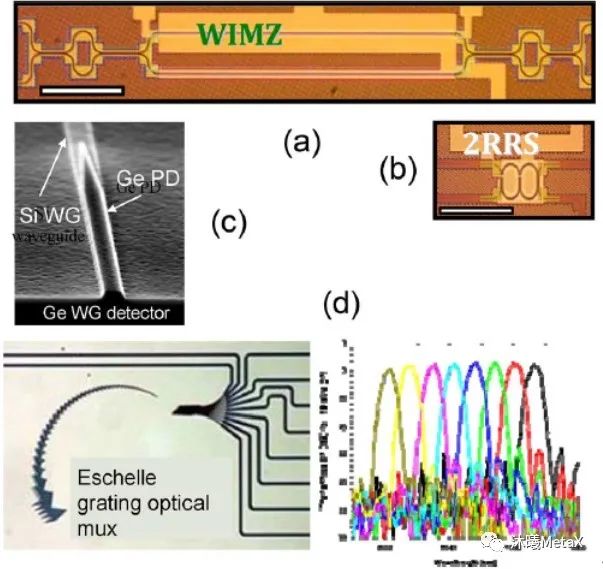

圖5. ?(a)波長不敏感的馬赫曾德爾調(diào)制器;

(b)雙微環(huán)諧振腔調(diào)制器;(c)集成的鍺光探測器和硅波導(dǎo);

(d)基于埃謝勒光柵的光復(fù)用/解復(fù)用器及其關(guān)聯(lián)的傳輸光譜

(來源于參考資料[12])

圖5(a)-(d)展示了硅基光子技術(shù)所需要的幾種技術(shù)元素:硅波導(dǎo)、集成的鍺探測器、基于馬赫曾德爾干涉儀的調(diào)制器、基于微環(huán)諧振腔的調(diào)制器、波分復(fù)用/解復(fù)用原件。自2014年起,硅基光子技術(shù)的產(chǎn)業(yè)化得以明顯完善,其商業(yè)產(chǎn)品的主要形式為有源纜線[15]。因?yàn)樵摷夹g(shù)需使用長波長(通常為1300 nm窗口或1500 nm窗口,以充分利用成熟的電信場景連續(xù)波單模激光器)和單模光纖,所以基于硅光子的各類收發(fā)器件和基于VCSEL的短波長/多模光纖技術(shù)并不相容。有源光纜對(duì)于數(shù)據(jù)中心或HPC系統(tǒng)具有良好的互用性,這使得硅基光子技術(shù)已經(jīng)開始在商用市場中展露鋒芒。此外,長距離光通信在大規(guī)模裝置的互連場景中很具吸引力,而這卻是多模光纖鏈路的短板;而硅基光子鏈路中的單模光纖在長波長范圍內(nèi)具有很低的信號(hào)失真和本征損耗,可有效增大高數(shù)據(jù)速率光鏈路的通信距離。

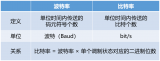

表1. 兩種不同的硅基光子調(diào)制器設(shè)計(jì)之比較

高度集成光電器件中的寄生效應(yīng)并不明顯,非常有利于降低高數(shù)據(jù)速率條件下的系統(tǒng)功耗。硅材料屬間接帶隙半導(dǎo)體材料,需要借助混合集成技術(shù)解決片上光源和光放大等難題。在設(shè)計(jì)調(diào)制器時(shí),硅基光子技術(shù)需充分利用硅材料中的光子、電子及光電子器件的工作機(jī)理和光電特性。調(diào)制器設(shè)計(jì)需在光帶寬、溫度靈敏度及控制、功耗、光損耗之間尋求平衡。我們?cè)谶@里試舉一例:表1對(duì)馬赫曾德爾和微環(huán)諧振腔兩種調(diào)制器設(shè)計(jì)作了性能比較。可以看出,前者具有相對(duì)較大的光帶寬、相對(duì)較小的溫度靈敏度,卻占用著相對(duì)較大的面積和較高的功耗。值得慶辛的是,未來GPU加速的大規(guī)模HPC機(jī)器或?qū)⑵毡椴捎盟浞桨福蓪⑵涔ぷ鳒囟确秶蠓档椭翈资當(dāng)z氏度。然而,為了追尋更大的市場影響力,硅基光子技術(shù)必須在更為典型的溫度范圍內(nèi)(如0-70 ℃)有所作為。

激光器光源可以封裝在芯片之上、或是芯片之外一個(gè)較為方便的位置,并通過光纖與芯片耦合[16]。雖然芯片之上的位置選項(xiàng)有利于實(shí)現(xiàn)更為集成化和低成本的封裝,但是它卻面臨著更為嚴(yán)峻的熱環(huán)境挑戰(zhàn)。相較而言,芯片之外的位置選項(xiàng)則能夠?yàn)榧す馄魈峁┮粋€(gè)獨(dú)立的空間環(huán)境,從而可以更加精確地控制溫度和波長;同時(shí),較低的環(huán)境溫度則更加有利于提升激光器的可靠性。進(jìn)一步地講,人們已開始考慮使用高功率的芯片外激光器:這類激光器可在不同的收發(fā)器之間實(shí)現(xiàn)分隔化使用,從而有效分?jǐn)偠嗦饭庑诺婪桨钢屑す馄鳌⒓す馄鞣庋b、冷卻系統(tǒng)等各項(xiàng)成本。

封裝是硅基光子技術(shù)探討中常被忽視的另一重要領(lǐng)域。盡管硅基光子芯片自身有著較低的成本,但是芯片和光纖的耦合、連續(xù)波激光器的使用等卻又無形中大幅增加了通信系統(tǒng)的成本。事實(shí)上,與滿足多模工作條件的封裝(約為10 μm)相比,滿足單模工作條件的封裝(通常小于1 μm)是非常昂貴的。另一方面,相較于多模VCSEL,單模邊發(fā)射激光器對(duì)反射光更為敏感。因此,人們還需在硅基光子通信中使用光隔離器,且將光反饋的數(shù)量保持在較低水平(約-30-40 dB)。

最后,人們還需考慮硅基光子鏈路的總體功耗情況。盡管低功率光鏈路具有極大潛力(例如具有100 fJ/bit的調(diào)制器[17]),但是試圖均衡考量性能、溫度、所有功耗源(包括溫度控制、連續(xù)波激光器、時(shí)鐘邏輯電路控制)等因素的鏈路設(shè)計(jì)方案仍十分受限。值得一提的是,對(duì)于硅基光子技術(shù)在光互連方面的應(yīng)用而言,學(xué)界和業(yè)界在近期普遍認(rèn)為其終極形式將會(huì)是基于高密度2.5D或3D芯片堆疊的光收發(fā)器集成 [18]。而這又為其他匹配技術(shù)的發(fā)展和成熟提出了新的挑戰(zhàn)。

1.4無源光連接器和線纜

除去上文所討論的幾種有源光收發(fā)器技術(shù)之外,人們還需借助無源光連接器和線纜將所有卡、板、機(jī)架上的光收發(fā)器連接起來。在VCSEL光纖鏈路中,這依賴于并行光纖并帶和連接器(如已在多模光纖鏈路中得以長期使用的多路并行光路)。在考慮未對(duì)準(zhǔn)容差的基礎(chǔ)上,連接器損耗通常不得大于0.5 dB。

而對(duì)于基于塑料波導(dǎo)的光鏈路來說,具備低損耗特征的長距離連接(如1 m的板到板距離)便成為一種迫切需求。人們也可在這類鏈路中使用低損耗光纖(如圖4(d)所示)。而由于圓形光纖纖芯或方形波導(dǎo)纖芯(根據(jù)尺寸選擇,或?yàn)榉菍?duì)稱結(jié)構(gòu))之間幾何結(jié)構(gòu)的不匹配,這些連接器會(huì)有大約0.5 dB的附加損耗。

硅基光子技術(shù)會(huì)對(duì)單模工作的光纖和連接器有所需求。基于更為嚴(yán)格的對(duì)準(zhǔn)公差需求,這類連接器通常有著0.25 dB的附加損耗(事實(shí)上,人們亦可使用具有更高成本的低損耗器件)。此外,因?yàn)榛覊m可較為容易地阻塞單模光纖纖芯(約為9 μm,而多模光纖纖芯通常為50 μm或62.5 μm),在連接器組裝過程中還需重點(diǎn)關(guān)注環(huán)境顆粒對(duì)單模光纖連接器的污染問題。

02長期的技術(shù)需求

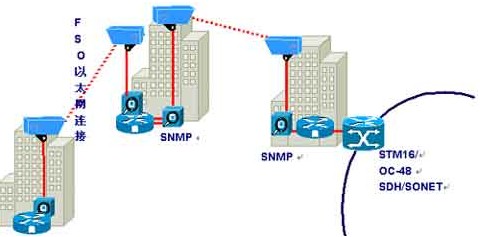

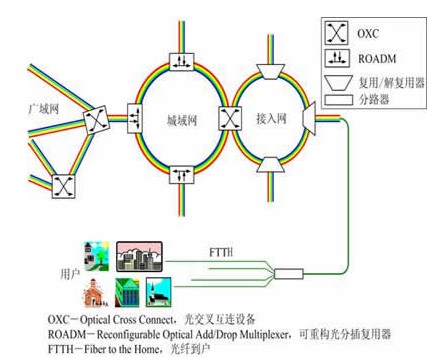

2.1從光互連到光交換

在光互連技術(shù)之外,光學(xué)技術(shù)的另一個(gè)重要角色則在于交換[19]。當(dāng)前,對(duì)于網(wǎng)絡(luò)功率預(yù)算而言,其大部分份額須分配給傳統(tǒng)的電分組交換。這意味著光交換或才是真正需要業(yè)界去付諸實(shí)踐、實(shí)現(xiàn)突破的領(lǐng)域。

面對(duì)光互連網(wǎng)絡(luò)的交換需求,人們需要對(duì)超級(jí)計(jì)算機(jī)內(nèi)的流量模式有著深入理解。事實(shí)上,能夠和任意流量模式相匹配的單個(gè)最佳拓?fù)浣Y(jié)構(gòu)是不存在的。盡管在超級(jí)計(jì)算機(jī)中部署光電路交換的實(shí)際價(jià)值尚未被人們完全理解,但是近幾年學(xué)界和業(yè)界對(duì)HPC應(yīng)用的研究卻已經(jīng)對(duì)光/電通信模式結(jié)構(gòu)的進(jìn)一步演進(jìn)指明了方向。

由光交叉互連而引入的信號(hào)損耗須在系統(tǒng)中得以修復(fù)。基于此,業(yè)界部分人士對(duì)采用光交換來應(yīng)對(duì)百億億次計(jì)算挑戰(zhàn)的實(shí)際效用仍持有懷疑態(tài)度。此外,較低的平均鏈路利用率也會(huì)對(duì)光交換的效能產(chǎn)生限制。因此,人們需要在改進(jìn)利用率和最小化數(shù)據(jù)隊(duì)列之間尋求技術(shù)均衡。在一個(gè)嚴(yán)格意義上的光交換網(wǎng)絡(luò)中,比特在電路進(jìn)行重構(gòu)時(shí)是無法流動(dòng)的,而存貯這些比特的光緩存技術(shù)還尚未實(shí)現(xiàn)。這就意味著,若數(shù)據(jù)包長度在若干個(gè)納秒范圍之內(nèi),則重構(gòu)時(shí)間必須極短(在1納秒之內(nèi))且光交換必須在納秒級(jí)別的時(shí)間尺度內(nèi)具有高度靈活性。

上述光交換能力的缺失使得人們對(duì)全光分組交換網(wǎng)絡(luò)的實(shí)際應(yīng)用有所疑問。既然光子還被限定在電路交換范圍之內(nèi),將光路交換和電路交換融合在一起的解決方案便成為了必然選項(xiàng)。在這種方案中,數(shù)據(jù)緩存和數(shù)據(jù)包交換均在電域?qū)崿F(xiàn),且人們需要將光電轉(zhuǎn)換的次數(shù)降至最低。基于微機(jī)電系統(tǒng)的光交換或可實(shí)現(xiàn)足夠的端口密度。目前,由于微機(jī)電系統(tǒng)交換機(jī)的端口成本仍舊較高(約為每端口數(shù)百美元),所以它在市場中并未得到廣泛使用。盡管HPC的市場規(guī)模并不足以大幅降低端口成本,但是微機(jī)電系統(tǒng)交換機(jī)在數(shù)據(jù)中心的使用或?qū)⒃龃笃湓贖PC市場中的吸引力。

2.2協(xié)同設(shè)計(jì)

總體看來,光互連和光交換必將在GPU加速的HPC系統(tǒng)中扮演重要角色。然而,這在很大程度上依賴于一些新光學(xué)技術(shù)和新工作方式的采用。從工業(yè)應(yīng)用角度出發(fā),硬件、軟件和應(yīng)用工程師需要通力合作、協(xié)同開發(fā)一類可在集成環(huán)境中得以實(shí)施的新型架構(gòu)和代碼庫。這種軟硬件協(xié)同設(shè)計(jì)已然成為當(dāng)前大規(guī)模HPC系統(tǒng)開發(fā)的關(guān)鍵。

為了促進(jìn)協(xié)同設(shè)計(jì),人們需減小系統(tǒng)集成商、設(shè)備供應(yīng)商和光學(xué)產(chǎn)品供應(yīng)商的市場區(qū)隔,并加速不同產(chǎn)業(yè)或技術(shù)實(shí)體之間的流通。事實(shí)上,當(dāng)前這種市場區(qū)隔依然十分頑固。光學(xué)供應(yīng)商在追尋更高的技術(shù)參數(shù)指標(biāo)時(shí),并未意識(shí)到新型設(shè)計(jì)或可推進(jìn)整體系統(tǒng)性能的突破。于是,系統(tǒng)集成商反而將注意力放在了具有漸進(jìn)式性能改進(jìn)和小幅降低成本特征的產(chǎn)品路線圖上。當(dāng)前,人們已經(jīng)對(duì)協(xié)同設(shè)計(jì)的必要性和重要性有了更為明晰的認(rèn)識(shí),讀者不妨對(duì)此持謹(jǐn)慎樂觀的態(tài)度。

03小結(jié)

GPU加速的HPC系統(tǒng)對(duì)光通信網(wǎng)絡(luò)的信息傳輸、接收和處理能力提出了更高要求。對(duì)VCSEL光纖鏈路技術(shù)、VCSEL光學(xué)PCB技術(shù)、硅基光子技術(shù)三類光通信選項(xiàng)來說,未來的趨勢(shì)主要在于:進(jìn)一步提升系統(tǒng)的數(shù)據(jù)處理容量和效率,由單個(gè)器件向大規(guī)模、高速率的集成芯片發(fā)展,從單一的收發(fā)功能向完整的可重構(gòu)系統(tǒng)發(fā)展,以及實(shí)現(xiàn)有源或無源器件的單片集成。

在本系列文章的第三篇,筆者將會(huì)對(duì)GPU網(wǎng)絡(luò)光互連的市場和產(chǎn)業(yè)趨勢(shì)、新興的工作負(fù)荷、策略和計(jì)劃做出介紹。

參考資料

[1] Anjin Liu et al., "Vertical-cavity surface-emitting lasers for data communication and sensing," Photonics Research?7, 121-136 (2019)

[2] N. Ledentsov Jr. et al., "Energy efficient 850-nm VCSEL based optical transmitter and receiver link capable of 56 Gbit/s NRZ operation," in 2019 SPIE 10938, Vertical-Cavity Surface-Emitting Lasers XXIII, 109380J

[3] F. Doany et al., "Dense 24 TX + 24 RX fiber-coupled optical module based on a holey CMOS transceiver IC," in 2010 60th Electronic Components and Technology Conference, 247-255

[4] M. V. Ramana Murty et al., "Development and characterization of 100 Gb/s data communication VCSELs," IEEE Photonics Technology Letters 33, 812-815 (2021)

[5] B. Wang et al., "4×112 Gbps/fiber CWDM VCSEL arrays for co-packaged interconnects," Journal of Lightwave Technology?38, 3439-3444 (2020)

[6] 劉安金, "單模直調(diào)垂直腔面發(fā)射激光器研究進(jìn)展," 中國激光 47, 0701005 (2020)

[7] E. Haglund et al., "30 GHz bandwidth 850 nm VCSEL with sub-100 fJ/bit energy dissipation at 25-50 Gbit/s," Electronics Letters, 51, 1096-1098 (2015)

[8] F. Koyama, "Recent progress of VCSEL photonics and their applications," in 2021 European Conference on Optical Communication, paper We1D.1

[9] P. Maniotis et al., "Toward lower-diameter large-scale HPC and data center networks with co-packaged optics," Journal of Optical Communications and Networking 13, A67-A77 (2021)

[10] C. Li et al., "Co-packaged optics with multimode fiber interface employing 2-D VCSEL matrix," Journal of Lightwave Technology?40, 3325-3330 (2022)

[11] F. Doany et al., "Terabit/sec-class board-level optical interconnects through polymer waveguides using 24-channel bidirectional transceiver modules," in 2011 IEEE Electronic Components and Technology Conference, 790-797

[12] M. A. Taubenblatt, "Optical interconnects for high-performance computing," Journal of Lightwave Technology 30, 448-457 (2012)

[13] R. Soref, "The past, present, and future of silicon photonics," IEEE Journal of Selected Topics in Quantum Electronics, 12, 1678-1687 (2006)

[14] D. Mahgerefteh et al., "Techno-economic comparison of silicon photonics and multimode VCSELs," Journal of Lightwave Technology?34, 233-242 (2016)

[15] S. Y. Siew et al., "Review of silicon photonics technology and platform development," Journal of Lightwave Technology?39, 4374-4389 (2021)

[16] D. Guckenberger et al., "Advantages of CMOS photonics for future transceiver applications," in 2010 36th European Conference on Optical Communication, 1-6

[17] H. Thacker et al., "Hybrid integration of silicon nanophotonics with 40 nm-COMS VLSI drivers and receivers," in 2011 IEEE Electronic Components and Technology Conference, 829-835

[18] R. Mahajan et al., "Co-packaged photonics for high performance computing: status, challenges and opportunities," Journal of Lightwave Technology?40, 379-392 (2022)

[19] S. J. Ben Yoo, "Prospects and challenges of photonic switching in data centers and computing systems," Journal of Lightwave Technology?40, 2214-2243 (2022)

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論