【摘 要】介紹了多采樣率數字信號處理(MRDSP)的基本理論和其中廣為應用的兩類高效的數字濾波器,以HSP50214和AD9856為范例,研究了MRDSP在軟件無線電中的兩種典型的硬件實現 。

關鍵詞:多采樣率數字信號處理 軟件無線電 數字上變頻器 數字下變頻器 數字抽取鏈 數字內插鏈

??? 多采樣率數字信號處理(Multirate Digital Signal Processing,MRDSP)是自20世紀70年代開始發展起來的數字信號處理領域的一門重要技術。1983年,R.E.Crochiere與L.R.Rabiner合寫的專著《Multirate Digital Signal Processing》〔1〕的出版標志著該學科的基礎理論已趨于成熟,但是,關于MRDSP的更深一層的應用至今仍在迅速地發展。所謂多采樣率,就是指在一個系統中存在著兩個或兩個以上的采樣率,其目的就是為了減少運算量和存儲量,以便于信號的存儲 、傳送和處理。隨著信號處理技術的發展,MRDSP已廣泛應用于信號處理的各領域。如今,隨著軟件無線電〔3〕〔4〕的興起,MRDSP已成為軟件無線電的關鍵技術之一。

1 多采樣率數字信號處理〔1〕〔2〕

1.1 多采樣率數字信號處理的基本內容

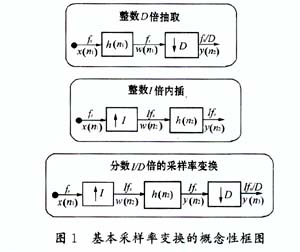

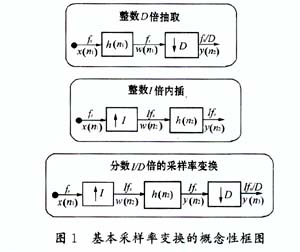

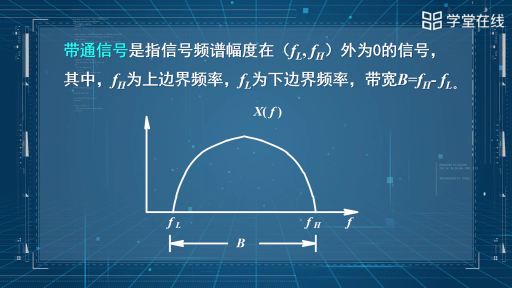

MRDSP的主要問題就是要設計一個有效的系統,使數字信號的采樣率提高或者降低任意倍。我們把降低信號采樣率的過程叫做抽取,亦稱采樣率壓縮,而把提高信號采樣率的過程叫做內插,亦稱采樣率擴張。基本的采樣率變換有整數D倍抽取、整數I倍內插和分數I/D倍的采樣率變換,如圖1所示。圖1中,信號序列的不同下標表示不同的采樣率,fs為信號的原始采樣率。圖中,“↓D”表示D倍抽取,即

每D個原始采樣抽取一個;“↑I”表示I倍零值內插,即每兩個相鄰原始采樣點之間均勻地插入I-1個零點。其中的濾波器是為了濾除抽取中的混疊信號頻譜和內插中的鏡像信號頻譜,它們分別稱為“抗混疊濾波器”和“去鏡像濾波器”。

圖1中,x(n1)、w(n1)、w(n2)、y(n2)、y(n3)表示的是數字信號序列(輸入、輸出或經過中間處理后的);h(n1)、h(n2)為數字濾波器(系數);其中的n1、n2、n3表示的是具有不同采樣率的數字信號或數字濾波器,而各自對應的采樣率即為箭頭上面所示。

圖1只是基本采樣率變換的概念性框圖,由于其中的濾波器運算均在系統采樣率最高處進行,所以,從運算量角度來說它們是低效的。實際中,總是采用采樣率變換的高效網絡結構,它主要有高效的直接式結構和高效的多相式結構等,其共同點是通過各種網絡的等效變換,將濾波器中的乘法運算安排在最低采樣率下;這樣,對于D倍抽取、I倍內插和I/D倍的采樣率變換可使其每秒乘法次數分別降低D、I和DI倍。由于對線性相位特性及穩定性的要求和容易實現高效結構的原因,采樣率變換系統中的濾波器通常都是FIR(Finite ImpulseResponse)濾波器。若FIR濾波器是對稱的,則在高效的直接式結構中可使乘法率再降低約一倍。為了進一步降低系統的運算量和存儲量,針對采樣率變換率為I/D的下述三種情形,我們經常用多級實現來代替單級實現:(1)D>>1,I=1;(2)I>>1,D=1;(3)D>>1,I>>1,I/D≈1。多級實現除了可以降低運算量和存儲量外,它還可以簡化濾波器的設計、減小濾波器系數的有限字長效應的影響等,但其代價是需要增加額外的控制結構。

1.2 兩類高效的數字濾波器

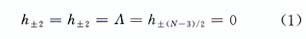

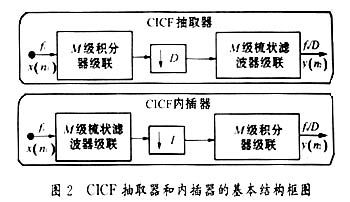

在實際的可編程硬件采樣率變換系統中,用得更多的FIR濾波器則是兩類高效的數字濾波器:半帶濾波器(Half-Band Filter,HBF)和級聯積分梳狀濾波器(Cascaded Integrator-Comb Filter,CICF)。由于各自濾波器系數的特殊性,它們在節省運算量和存儲量方面顯得特別有效 。設某一HBF的階數為N,則

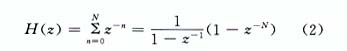

即除h0以外的所有偶序號的濾波器系數均為0。所以,應用HBF可以使系統的運算量和存儲量同時再降低約一半。由于其頻響特性的特殊性,HBF只能用于變換因子為2的抽取或內插過程。CICF〔5〕則更簡單,所有的濾波器系數均為1,因而CICF又稱為簡單整系數濾波器。在濾波器的實現時,CICF將只有加法而沒有乘法,更無需專門的存儲器用于存儲濾波器的系數。濾波器的結構也相當規整,我們可以容易地寫出一個N階CICF的系統函數

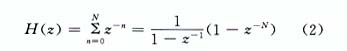

可見,一個CICF可以看作由一個積分器與一個梳狀濾波器的級聯,這就是CICF名字的由來。根據式(2)我們可以算出CICF的第一旁瓣峰值相對于主瓣峰值僅衰減約13.46dB。為了加大阻帶衰減 ,我們通常將幾級CICF級聯起來。圖2為M級CICF級聯的D倍抽取器和I倍內插器的結構框圖。由于在多級實現的抽取系統的首級和內插系統的末級,信號的歸一化帶寬較小,阻帶特性容易滿足 ,而且在這些變換級中信號的采樣率過高,使得乘法運算極不經濟,首要任務就是把信號的采樣率降下來。因此,CICF經常用于抽取系統的首級或內插系統的末級。

2 多采樣率數字信號處理在軟件無線電中的硬件實現

2.1 軟件無線電中的多采樣率數字信號處理

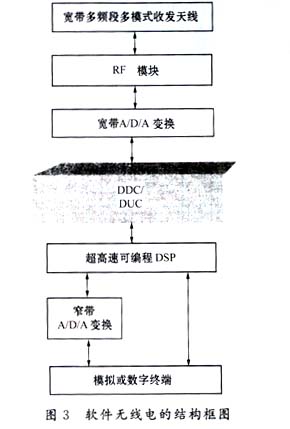

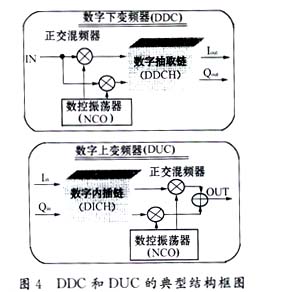

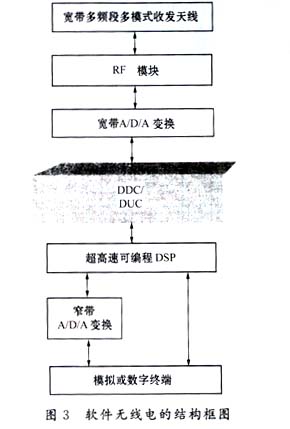

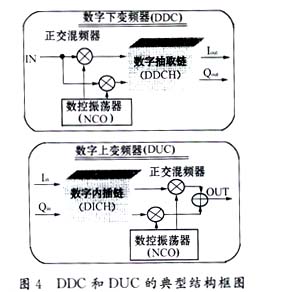

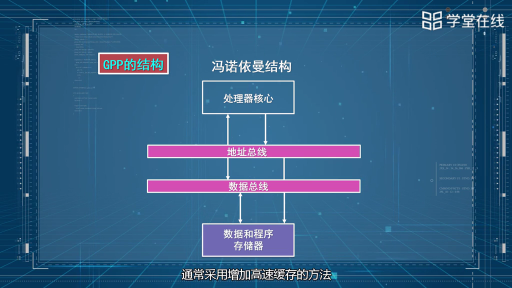

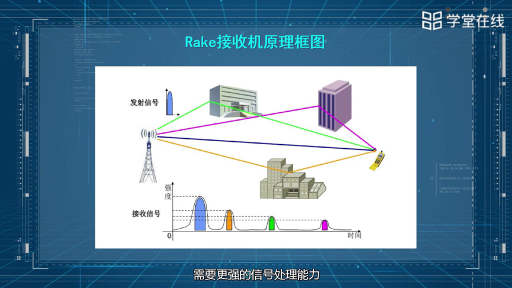

軟件無線電正代表著包括無線通信在內的幾乎所有的無線電電子信息系統的發展總趨勢,其核心思想就是將A/D/A(模數/數模變換)變換器盡量靠近天線,在對信號充分數字化的基礎上依靠軟件來定義無線電的各項功能。理想的軟件無線電應是對射頻信號直接進行數字化,即數字射頻軟件無線電;而在現階段則由于各種關鍵器件,特別是ADC(模數變換器)和DSP(數字信號處理器)發展水平的限制,數字中頻軟件無線電正成為理想軟件無線電的一種經濟、適用的折中選擇。無論是數字射頻還是數字中頻軟件無線電,數字下變頻器(Digital Downconverter,DDC)和數字上變頻器(Digital Upconverter,DUC)通常都是必不可少的關鍵器件,如圖3所示。其原因有二:一是為了降低輸入DSP的信號的采樣率,以減輕DSP的運算負荷;二是通常信號的帶寬僅為幾百kHz以下,沒有必要采用過高的采樣率,這就使得采樣率的降低成為可能。DDC和DDC主要有三大功能:變頻(上變頻或下變頻)、采樣率變換(壓縮或擴張)和低通濾波。其中的采樣率變換和低通濾波在實際系統中是以多級級聯的形式由同一個功能模塊來完成的,這里我們將該模塊在DDC和DDC中分別稱為數字抽取鏈(Digital Decimation Chain,DDCH)和數字內插鏈(Digital Interpolation Chain,DICH)。DDCH和DICH在本質上說就是采樣率變換的多級實現,因此其理論基礎是MRDSP。圖4為DDC和DDC的典型結構框圖。由圖可見,DDC和DUC在結構上具有互易性。在下面的討論中我們將會發現,其中的DDCH和DICH也有同樣的關系。

軟件無線電中的硬件數字抽取鏈和數字內插鏈應當具有方便的通用可編程性,我們可以根據自己的需要用FPGA或ASIC等進行專門設計,但更為經濟、快捷的途徑則是采用現成的商用數字下變頻器和數字上變頻器器件。商用DDC和DUC把變頻和DDCH或DICH甚至是部分的解調或調制等功能模塊都集成在同一塊芯片上,節省了許多的設計開發時間和成本。盡管不同廠商的DDC和DUC千差萬別,但它們的基本結構都是一樣的(如圖4所示),其最核心的功能模塊就是DDCH和DICH。這里,我們挑選了目前單通道DDC和DUC中兩種結構典型、性能先進并倍受青睞的商用器件進行討論:一是Intersil公司(即99年8月份更名前的Harris公司)的SP50214B可編程下變頻器(PDC),二是Analog Devices公司的AD9856正交上變頻器(QDUC)。由于討論的是MRDSP的硬件實現,所以我們僅研究這兩種器件中的DDCH和DICH。

2.2 DDCH與DICH的兩種典型的硬件實現

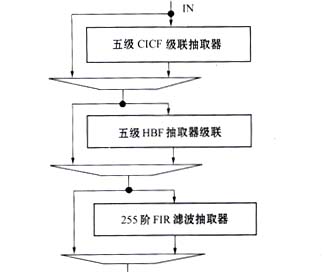

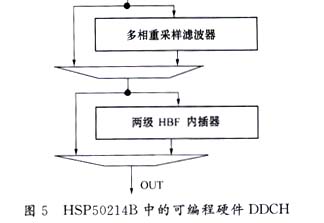

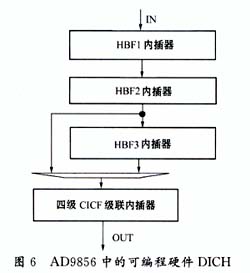

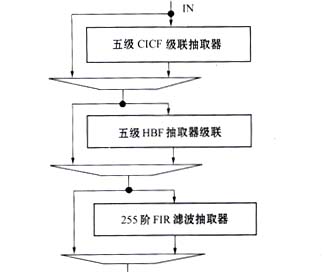

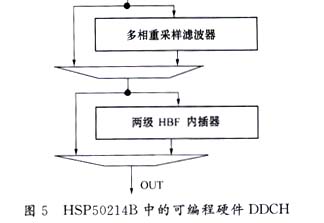

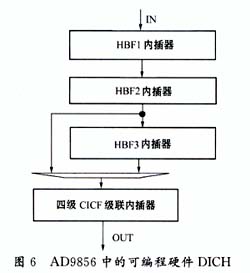

DDC中的DDCH和DUC中的DICH均有完全相同的正交兩路,這是為了數字信號處理的方便和信號采樣率的進一步降低;我們這里僅選其中的任意一路進行研究。圖5為HSP50214B中可編程DDCH的具體硬件實現結構,圖6為AD9856中的可編程DICH的具體硬件實現結構。

??? 如前所述,由于半帶濾波器(HBF)與級聯積分梳狀濾波器(CICF)在節省運算量和存儲量方面均具有獨到的優勢,所以幾乎所有商品化的DDC和DUC產品均采用了這兩類濾波器,HSP50214和AD9856也不例外。正如我們所預料的,CICF均以級聯的形式被分別安排在數字抽取鏈的首級和數字內插鏈的末級,用以承擔較大的抽取因子和內插因子;并且,CICF濾波器結構規則,無需另外設計,比較容易修改抽取因子,可編程性能好。其中,上述數字抽取鏈中的CICF為5級級聯,可承受的抽取因子為4~32之間的整數;數字內插鏈中的CICF為4級級聯,可承受的內插因子為2~63之間的整數。HBF則在實現采樣率變化因子為2時特別有效。雖然采用HBF的抽取器的抽取因子較小且不可變,但我們可以通過若干級HBF抽取器級聯,通過選取不同的級數以達到改變HBF級抽取因子的目的。這里的數字抽取鏈采用了5級HBF抽取器級聯的形式,而數字內插鏈則采用了3級HBF級聯的形式。考慮到數字下變頻器還必須較好地完成對信號的濾波整形功能,而HBF與CICF在這方面又存在缺陷,所以,面向濾波整形功能的普通FIR濾波器在數字抽取鏈中通常又是必不可少的。濾波整形FIR級在數字抽取鏈中一般都是位于CICF和HBF級之后,以便在較低的采樣率下更加有效地實現,而且在CICF和HBF完成主要的采樣率變化功能的情況下,該級通常不承擔或只完成較小的抽取因子;所有這些都是為了使得可編程FIR抽取濾波器具有更高的可用階數,更有效地完成濾波整形功能。AD9856之所以沒有采用可編程FIR級是出于假設進入數字上變頻器的基帶信號已經能夠滿足信號頻譜的技術要求。由于無法預知接收信號所處的頻段和所需的確切采樣率,所以作為接收用的數字下變頻器還必須考慮到實際中常有的采樣率變換非整數倍的情況。為此,HSP50214B中的數字抽取鏈還包含了面向采樣率變換為分數倍的“重采樣”級,由于該級的內插部分采用了多相結構,所以在此稱為“多相重采樣濾波器”。而作為發射用的數字上變頻器通常是不需要重采樣級的。為了恢復前面由于抽取而損失的時間分辨率和進一步降低可編程FIR級的采樣率,以更充分地利用濾波整形功能,HSP50214B還在整個DDCH的最后部分增加了兩級HBF內插級,這是HSP50214B在設計方面的獨到之處。另外,比較圖5和圖6我們可以看出,HSP50214B中數字抽取鏈的每一級都可以被使能或旁路,這就更增加了其可編程性;而AD9856則只有HBF3內插器可以被使能或旁路。

本文介紹的DDCH和DICH都同時具有先進性和典型性,我們希望這些內容對軟件無線電設計者和使用者能有所啟發。

1 R.E.Crochiere and L.R.Rabiner.Multirate DigitalSignal Processing.Englewood Cliffs,NJ:Prentice Hall,1983

2 宗孔德.多抽樣率信號處理.北京:清華大學出版社,1996

3 J.Mitola.The Software Radio Architecture.IEEECo-mmunications Magazine,May 1995

4 R.J.Lackey,D.W.Upmal.Speakeasy:The MilitarySoftware Radio.IEEECommunications Magazine,May 1995

5 E.B.Hogenauer.An EconomicalClass ofDigitalFil-ters for Decimation and Interpolation.IEEETransactions on Acoustic,Speech Signal Processing.April,1981

6 程水英,陳鵬舉,武傳華.HSP50214BPDC及其在軟件無線電中的應用.電子技術應用,2000(12)

7 http://www.analog.com AD9856 Data Sheet.REV.A,1999

關鍵詞:多采樣率數字信號處理 軟件無線電 數字上變頻器 數字下變頻器 數字抽取鏈 數字內插鏈

??? 多采樣率數字信號處理(Multirate Digital Signal Processing,MRDSP)是自20世紀70年代開始發展起來的數字信號處理領域的一門重要技術。1983年,R.E.Crochiere與L.R.Rabiner合寫的專著《Multirate Digital Signal Processing》〔1〕的出版標志著該學科的基礎理論已趨于成熟,但是,關于MRDSP的更深一層的應用至今仍在迅速地發展。所謂多采樣率,就是指在一個系統中存在著兩個或兩個以上的采樣率,其目的就是為了減少運算量和存儲量,以便于信號的存儲 、傳送和處理。隨著信號處理技術的發展,MRDSP已廣泛應用于信號處理的各領域。如今,隨著軟件無線電〔3〕〔4〕的興起,MRDSP已成為軟件無線電的關鍵技術之一。

1 多采樣率數字信號處理〔1〕〔2〕

1.1 多采樣率數字信號處理的基本內容

MRDSP的主要問題就是要設計一個有效的系統,使數字信號的采樣率提高或者降低任意倍。我們把降低信號采樣率的過程叫做抽取,亦稱采樣率壓縮,而把提高信號采樣率的過程叫做內插,亦稱采樣率擴張。基本的采樣率變換有整數D倍抽取、整數I倍內插和分數I/D倍的采樣率變換,如圖1所示。圖1中,信號序列的不同下標表示不同的采樣率,fs為信號的原始采樣率。圖中,“↓D”表示D倍抽取,即

每D個原始采樣抽取一個;“↑I”表示I倍零值內插,即每兩個相鄰原始采樣點之間均勻地插入I-1個零點。其中的濾波器是為了濾除抽取中的混疊信號頻譜和內插中的鏡像信號頻譜,它們分別稱為“抗混疊濾波器”和“去鏡像濾波器”。

圖1中,x(n1)、w(n1)、w(n2)、y(n2)、y(n3)表示的是數字信號序列(輸入、輸出或經過中間處理后的);h(n1)、h(n2)為數字濾波器(系數);其中的n1、n2、n3表示的是具有不同采樣率的數字信號或數字濾波器,而各自對應的采樣率即為箭頭上面所示。

圖1只是基本采樣率變換的概念性框圖,由于其中的濾波器運算均在系統采樣率最高處進行,所以,從運算量角度來說它們是低效的。實際中,總是采用采樣率變換的高效網絡結構,它主要有高效的直接式結構和高效的多相式結構等,其共同點是通過各種網絡的等效變換,將濾波器中的乘法運算安排在最低采樣率下;這樣,對于D倍抽取、I倍內插和I/D倍的采樣率變換可使其每秒乘法次數分別降低D、I和DI倍。由于對線性相位特性及穩定性的要求和容易實現高效結構的原因,采樣率變換系統中的濾波器通常都是FIR(Finite ImpulseResponse)濾波器。若FIR濾波器是對稱的,則在高效的直接式結構中可使乘法率再降低約一倍。為了進一步降低系統的運算量和存儲量,針對采樣率變換率為I/D的下述三種情形,我們經常用多級實現來代替單級實現:(1)D>>1,I=1;(2)I>>1,D=1;(3)D>>1,I>>1,I/D≈1。多級實現除了可以降低運算量和存儲量外,它還可以簡化濾波器的設計、減小濾波器系數的有限字長效應的影響等,但其代價是需要增加額外的控制結構。

1.2 兩類高效的數字濾波器

在實際的可編程硬件采樣率變換系統中,用得更多的FIR濾波器則是兩類高效的數字濾波器:半帶濾波器(Half-Band Filter,HBF)和級聯積分梳狀濾波器(Cascaded Integrator-Comb Filter,CICF)。由于各自濾波器系數的特殊性,它們在節省運算量和存儲量方面顯得特別有效 。設某一HBF的階數為N,則

即除h0以外的所有偶序號的濾波器系數均為0。所以,應用HBF可以使系統的運算量和存儲量同時再降低約一半。由于其頻響特性的特殊性,HBF只能用于變換因子為2的抽取或內插過程。CICF〔5〕則更簡單,所有的濾波器系數均為1,因而CICF又稱為簡單整系數濾波器。在濾波器的實現時,CICF將只有加法而沒有乘法,更無需專門的存儲器用于存儲濾波器的系數。濾波器的結構也相當規整,我們可以容易地寫出一個N階CICF的系統函數

可見,一個CICF可以看作由一個積分器與一個梳狀濾波器的級聯,這就是CICF名字的由來。根據式(2)我們可以算出CICF的第一旁瓣峰值相對于主瓣峰值僅衰減約13.46dB。為了加大阻帶衰減 ,我們通常將幾級CICF級聯起來。圖2為M級CICF級聯的D倍抽取器和I倍內插器的結構框圖。由于在多級實現的抽取系統的首級和內插系統的末級,信號的歸一化帶寬較小,阻帶特性容易滿足 ,而且在這些變換級中信號的采樣率過高,使得乘法運算極不經濟,首要任務就是把信號的采樣率降下來。因此,CICF經常用于抽取系統的首級或內插系統的末級。

2 多采樣率數字信號處理在軟件無線電中的硬件實現

2.1 軟件無線電中的多采樣率數字信號處理

軟件無線電正代表著包括無線通信在內的幾乎所有的無線電電子信息系統的發展總趨勢,其核心思想就是將A/D/A(模數/數模變換)變換器盡量靠近天線,在對信號充分數字化的基礎上依靠軟件來定義無線電的各項功能。理想的軟件無線電應是對射頻信號直接進行數字化,即數字射頻軟件無線電;而在現階段則由于各種關鍵器件,特別是ADC(模數變換器)和DSP(數字信號處理器)發展水平的限制,數字中頻軟件無線電正成為理想軟件無線電的一種經濟、適用的折中選擇。無論是數字射頻還是數字中頻軟件無線電,數字下變頻器(Digital Downconverter,DDC)和數字上變頻器(Digital Upconverter,DUC)通常都是必不可少的關鍵器件,如圖3所示。其原因有二:一是為了降低輸入DSP的信號的采樣率,以減輕DSP的運算負荷;二是通常信號的帶寬僅為幾百kHz以下,沒有必要采用過高的采樣率,這就使得采樣率的降低成為可能。DDC和DDC主要有三大功能:變頻(上變頻或下變頻)、采樣率變換(壓縮或擴張)和低通濾波。其中的采樣率變換和低通濾波在實際系統中是以多級級聯的形式由同一個功能模塊來完成的,這里我們將該模塊在DDC和DDC中分別稱為數字抽取鏈(Digital Decimation Chain,DDCH)和數字內插鏈(Digital Interpolation Chain,DICH)。DDCH和DICH在本質上說就是采樣率變換的多級實現,因此其理論基礎是MRDSP。圖4為DDC和DDC的典型結構框圖。由圖可見,DDC和DUC在結構上具有互易性。在下面的討論中我們將會發現,其中的DDCH和DICH也有同樣的關系。

軟件無線電中的硬件數字抽取鏈和數字內插鏈應當具有方便的通用可編程性,我們可以根據自己的需要用FPGA或ASIC等進行專門設計,但更為經濟、快捷的途徑則是采用現成的商用數字下變頻器和數字上變頻器器件。商用DDC和DUC把變頻和DDCH或DICH甚至是部分的解調或調制等功能模塊都集成在同一塊芯片上,節省了許多的設計開發時間和成本。盡管不同廠商的DDC和DUC千差萬別,但它們的基本結構都是一樣的(如圖4所示),其最核心的功能模塊就是DDCH和DICH。這里,我們挑選了目前單通道DDC和DUC中兩種結構典型、性能先進并倍受青睞的商用器件進行討論:一是Intersil公司(即99年8月份更名前的Harris公司)的SP50214B可編程下變頻器(PDC),二是Analog Devices公司的AD9856正交上變頻器(QDUC)。由于討論的是MRDSP的硬件實現,所以我們僅研究這兩種器件中的DDCH和DICH。

2.2 DDCH與DICH的兩種典型的硬件實現

DDC中的DDCH和DUC中的DICH均有完全相同的正交兩路,這是為了數字信號處理的方便和信號采樣率的進一步降低;我們這里僅選其中的任意一路進行研究。圖5為HSP50214B中可編程DDCH的具體硬件實現結構,圖6為AD9856中的可編程DICH的具體硬件實現結構。

??? 如前所述,由于半帶濾波器(HBF)與級聯積分梳狀濾波器(CICF)在節省運算量和存儲量方面均具有獨到的優勢,所以幾乎所有商品化的DDC和DUC產品均采用了這兩類濾波器,HSP50214和AD9856也不例外。正如我們所預料的,CICF均以級聯的形式被分別安排在數字抽取鏈的首級和數字內插鏈的末級,用以承擔較大的抽取因子和內插因子;并且,CICF濾波器結構規則,無需另外設計,比較容易修改抽取因子,可編程性能好。其中,上述數字抽取鏈中的CICF為5級級聯,可承受的抽取因子為4~32之間的整數;數字內插鏈中的CICF為4級級聯,可承受的內插因子為2~63之間的整數。HBF則在實現采樣率變化因子為2時特別有效。雖然采用HBF的抽取器的抽取因子較小且不可變,但我們可以通過若干級HBF抽取器級聯,通過選取不同的級數以達到改變HBF級抽取因子的目的。這里的數字抽取鏈采用了5級HBF抽取器級聯的形式,而數字內插鏈則采用了3級HBF級聯的形式。考慮到數字下變頻器還必須較好地完成對信號的濾波整形功能,而HBF與CICF在這方面又存在缺陷,所以,面向濾波整形功能的普通FIR濾波器在數字抽取鏈中通常又是必不可少的。濾波整形FIR級在數字抽取鏈中一般都是位于CICF和HBF級之后,以便在較低的采樣率下更加有效地實現,而且在CICF和HBF完成主要的采樣率變化功能的情況下,該級通常不承擔或只完成較小的抽取因子;所有這些都是為了使得可編程FIR抽取濾波器具有更高的可用階數,更有效地完成濾波整形功能。AD9856之所以沒有采用可編程FIR級是出于假設進入數字上變頻器的基帶信號已經能夠滿足信號頻譜的技術要求。由于無法預知接收信號所處的頻段和所需的確切采樣率,所以作為接收用的數字下變頻器還必須考慮到實際中常有的采樣率變換非整數倍的情況。為此,HSP50214B中的數字抽取鏈還包含了面向采樣率變換為分數倍的“重采樣”級,由于該級的內插部分采用了多相結構,所以在此稱為“多相重采樣濾波器”。而作為發射用的數字上變頻器通常是不需要重采樣級的。為了恢復前面由于抽取而損失的時間分辨率和進一步降低可編程FIR級的采樣率,以更充分地利用濾波整形功能,HSP50214B還在整個DDCH的最后部分增加了兩級HBF內插級,這是HSP50214B在設計方面的獨到之處。另外,比較圖5和圖6我們可以看出,HSP50214B中數字抽取鏈的每一級都可以被使能或旁路,這就更增加了其可編程性;而AD9856則只有HBF3內插器可以被使能或旁路。

本文介紹的DDCH和DICH都同時具有先進性和典型性,我們希望這些內容對軟件無線電設計者和使用者能有所啟發。

參考文獻

2 宗孔德.多抽樣率信號處理.北京:清華大學出版社,1996

3 J.Mitola.The Software Radio Architecture.IEEECo-mmunications Magazine,May 1995

4 R.J.Lackey,D.W.Upmal.Speakeasy:The MilitarySoftware Radio.IEEECommunications Magazine,May 1995

5 E.B.Hogenauer.An EconomicalClass ofDigitalFil-ters for Decimation and Interpolation.IEEETransactions on Acoustic,Speech Signal Processing.April,1981

6 程水英,陳鵬舉,武傳華.HSP50214BPDC及其在軟件無線電中的應用.電子技術應用,2000(12)

7 http://www.analog.com AD9856 Data Sheet.REV.A,1999

電子發燒友App

電子發燒友App

評論