完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

傳統的數字電壓表設計通常以大規模ASIC(專用集成電路)為核心器件,并輔以少量中規模集成電路及顯示器件構成。這種電壓表的設計簡單、精確度高,但是由于采用了ASIC器件使得它欠缺靈活性,其系統功能固定,難以更新擴展。而應用FPGA設計的電壓表,采用FPGA芯片控制通用A/D轉換器,可使速度、靈活性大大...

目前,基于IP的EDA設計流程面臨著兩大挑戰。首先,必須提供方法技術,用于測試包含IP組件設計的可靠性和質量;另一方面,必須保護IP供應商和設計者的知識產權。第三方IP核的使用確實可以提高芯片設計效率,但是供應商將IP核交付到客戶的過程卻并非直截了當。對于客戶來說,為了測試驗證IP核,它必須具備一定...

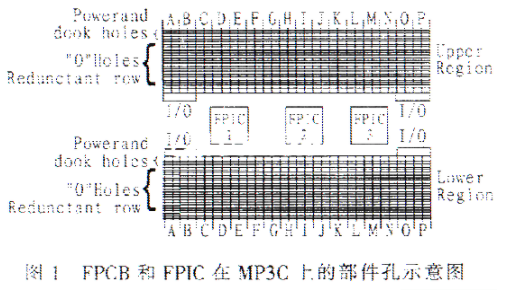

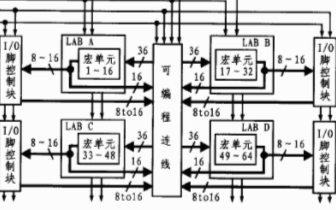

MP3C系統是Aptix公司的產品,是一種價格低、驗證速度快、基于層次化和模塊化的硬件驗證平臺,可以逐步驗證每一個邏輯模塊直到驗證整個系統功能。MP3C硬件中的現場可編程互連電路板(FPCB)和現場可編程互連元件(FPIC)是Aptix公司的專利技術,圖1給出了FPCB和FPIC在MP3C上的部件孔...

Anadigm公司推出的第二代現場可編模擬陣列(FPAA)系列AN221E04,使設計者能在工業,汽車電子,醫療,通信,自動測試設備和儀表系統中實現信號調節,濾波,數據采集,閉環控制和其它模擬方面的應用。...

Stratix II是ALTERA公司生產的一款高性能FPGA器件。它采用TSMC的90 nm低k絕緣工藝技術生產,等價邏輯單元(LE)高達180 k,嵌入式存儲器容量達到9 MB。該器件不但具有極高的性能和密度,而且還針對器件總功率進行了優化,同時可以支持高達1 Gbps的高速差分I/O信號,因而...

一個完整的RFID系統包括:讀寫器、天線、標簽和PC機。讀寫器完成對標簽(Tag)的讀寫操作。通過RS232或RS485總線完成PC機的命令接收和EPC卡號的上傳。圖l是讀寫器的系統組成框圖。讀寫器組成包括與PC機的串口通信部分、單片機和FPGA組成的數字部分、射頻部分。RF單元實現和標簽的通信,數...

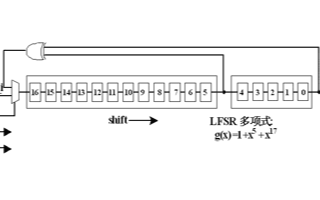

近年來,擴頻通信技術在移動通信、個人通信、室內無線通信以及衛星通信中得到越來越廣泛的應用。對于DS-CDMA(Direct Sequence-Code Division Multiple Access,直接序列-碼分多址)移動通信系統,因其具有較好的抗干擾性能而成為軍事通信、民用通信以及宇宙通信的一...

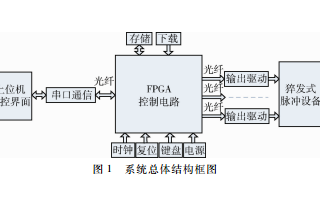

脈沖功率技術是一種功率壓縮技術,以較低的輸入功率將能量緩慢存儲起來,隨后在極短時間內釋放,以獲得極高的峰值輸出功率。該技術是應國防科技需要而發展起來的一門新興科學技術,是獲得高電壓、大電流等極端電磁參數的重要手段,被廣泛應用在科學研究和工業生產等諸多領域中。...

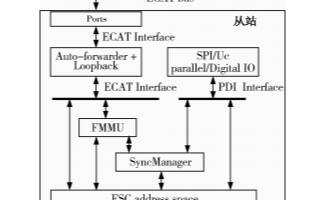

EtherCAT主要優勢在于高速、高實時性以及精確時鐘同步。這些優勢的實現基于EtherCAT設計的幾個關鍵技術:飛讀飛寫(processing on the fly)、FMMU(Fieldbus Memory Management Unit)、DC(Distribute Clock)。以上幾個關鍵...

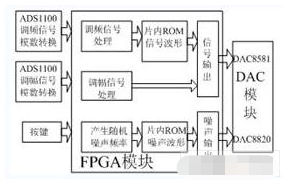

振動臺的作用之一是將被測物件置于振動臺上測量其受迫振動時的表現,一般振動臺的振動是由振動分析儀控制的,但是由于振動臺體積形狀和考慮到成本等原因,不利于振動分析儀的研發,所以設計振動模擬器對振動分析儀的研發有重要的現實意義。...

其中讀頭是整個系統的核心部分,控制整個識別過程中與標簽之間的通信,并提供與后臺計算機的接口。天線用來發送射頻信號給電子標簽,并把電子標簽響應的數據接收回來。電子標簽存儲著目標的信息,它進入識別區域時被天線發送的射頻信號激活,然后向讀頭返回應答,從而完成一次識別。...

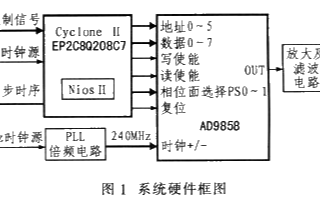

一般的雷達信號源實現主要有三種方式:第一種方式是采用DDS和MCU控制器件結合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結合的方式:第三種是由FPGA等可編程器件實現DDS的方式。第一種方式利用專用DDS器件可以產生具有較好的雜散抑制和諧波抑制性能的雷達波形。...

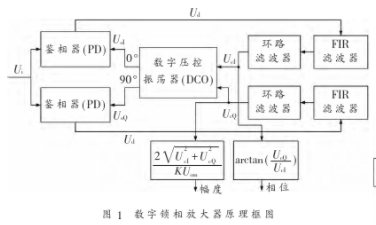

數字鎖相放大器因其具有動態范圍大、測量誤差小、不受運放溫漂和直流偏置影響的優勢,近年來逐漸取代了模擬鎖相放大器,但常見的數字鎖相放大器價格昂貴且不便于攜帶,不易于在特殊環境使用。...

隨著微電子技術的迅猛發展,可編程邏輯器件從20世紀70年代發展至今,其結構、工藝、集成度、功能、速度、性能等方面都在不斷的改進和提高;另外,電子設計自動化EDA技術的發展又為可編程邏輯器件的廣泛應用提供了有力的工具。...

在Kintex-7 FPGA上搭建MicroBlaze軟核,并由MicroBlaze配置PAL視頻模塊TL2867F和各IP核,將模塊輸出的一路4通道D1時分復用的復合視頻,拆分成4路獨立的BT656嵌入式同步視頻,再將4路視頻進行BT656解碼分離出同步信號和像素數據。...

可綜合模塊最終生成的bit文件會燒錄進芯片運行,而仿真模塊編譯過后是在仿真軟件(例如modelsim)上運行的。仿真模塊是基于可綜合模塊進行例化,并通過仿真軟件的模擬,可以初步驗證我們寫的可綜合模塊的實現現象。...

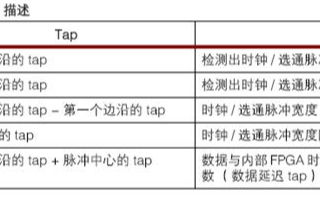

大多數存儲器接口都是源同步接口,從外部存儲器器件傳出的數據和時鐘/ 選通脈沖是邊沿對齊的。在 Virtex-4 器件采集這一數據,需要延遲時鐘/ 選通脈沖或數據。利用直接時鐘控制技術,數據經延遲,并與內部 FPGA 時鐘實現中心對齊。在這個方案中,內部 FPGA時鐘采集傳出的數據。存儲器傳出的時鐘/...

隨著工藝幾何尺寸越來越小,電子器件趨向于采用多種電壓供電,因此越來越易受到電壓和溫度波動的影響,而且在所有電子系統設計中進行系統管理的重要性也不斷增強。表面上好象無關的一系列任務其實都是以確保系統的正常運作為目標,系統管理任務的重點就是使系統正常運行的時間長、識別并傳送報警條件,以及記錄數據和報警的...

SPI-4.2(System Packet Interface)是 OIF(Optical Internetworking Forum)定義的局部高速總線標準,用于 PHY層芯片到鏈路層芯片的 10Gbps信號傳輸。主要應用有 OC-192 ATM、Packet over SONET/SDH(POS...

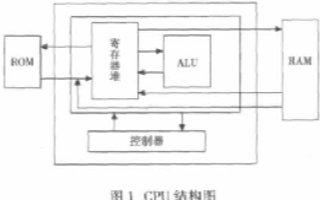

SoC(SystemonaChip)以其高集成度,低功耗等優點越來越受歡迎。開發人員不必從單個邏輯門開始去設計ASIC,而是應用己有IC芯片的功能模塊,稱為核(core),或知識產權(IP)宏單元進行快速設計,效率大為提高。CPU的IP核是SoC技術的核心,開發出具有自主知識產權的CPUIP核對我國...