完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

先談?wù)劦诙c(diǎn)關(guān)于思維習(xí)慣。我發(fā)現(xiàn)有些人會(huì)有這樣一種習(xí)慣,先用一段式狀態(tài)機(jī)實(shí)現(xiàn)功能,仿真ok后,再將其轉(zhuǎn)成三段式,他們對(duì)這種開(kāi)發(fā)方式的解釋是一段式更直觀,可以更便捷的構(gòu)建功能框架,但是大家都說(shuō)三段式性能會(huì)更好...

fpga 會(huì)從 0 開(kāi)始讀,地址不斷自增,直到讀取到有效的同步字 sync word(0xAA995566),才認(rèn)為接下來(lái)的內(nèi)容是一個(gè)有效的 bin 文件內(nèi)容的開(kāi)始。讀到有效 sync word 后不會(huì)再繼續(xù)讀搜尋其他的 bin 文件。如 UG470 文檔 page81 描述:...

LMZ31506 簡(jiǎn)單開(kāi)關(guān)器等電源模塊可以將 DC/DC 轉(zhuǎn)換器、功率 MOSFET、屏蔽電感器和無(wú)源器件集成到薄型 QFN 封裝中。這可以減少設(shè)計(jì)時(shí)間,因?yàn)樗袞|西都已經(jīng)集成到一個(gè)封裝中,并且只需要最少的外部組件。...

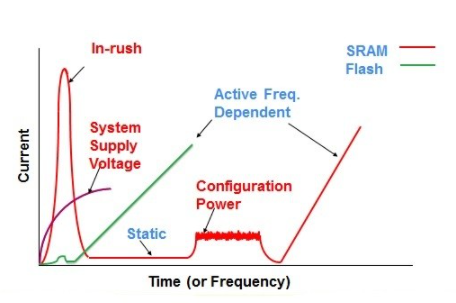

當(dāng)今以 DSP 為中心的系統(tǒng)設(shè)計(jì)面臨著越來(lái)越大的壓力,需要在各種應(yīng)用中最大限度地降低功耗。通過(guò)降低總功耗而不僅僅是靜態(tài)功耗,當(dāng)今基于閃存的 FPGA 技術(shù)在實(shí)現(xiàn)下一代高速、DSP 密集型系統(tǒng)設(shè)計(jì)方面發(fā)揮著關(guān)鍵作用,這些設(shè)計(jì)必須以不斷縮小的外形尺寸提供高算法性能和最低可能的功耗。...

現(xiàn)場(chǎng)可編程門陣列(FPGA)可以實(shí)現(xiàn)任意數(shù)字邏輯,從微處理器到視頻生成器或加密礦機(jī),一應(yīng)俱全。FPGA由許多邏輯模塊組成,每個(gè)邏輯模塊通常由觸發(fā)器和邏輯功能以及連接邏輯模塊的路由網(wǎng)絡(luò)組成。...

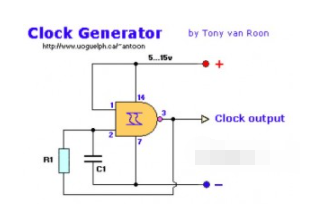

您可以在此電路中使用 IC 7400 或 4011。7400 是晶體管-晶體管邏輯 (TTL) 類型,而 4011 是互補(bǔ)金屬氧化物半導(dǎo)體 (CMOS) 類型。IC 4011 比 7400 便宜,但 7400 比 4011 快。...

XADC具有兩個(gè)12位的ADC,具有獨(dú)立的跟蹤和保持放大器,模擬多路復(fù)用器(最多17個(gè)外部模擬輸入通道)以及片上散熱和片上電壓傳感器。可以將兩個(gè)ADC配置為同時(shí)采樣兩個(gè)外部輸入模擬通道。采樣保持放大器支持一系列模擬輸入信號(hào)類型,包括單端輸入,雙端輸入和差分輸入。模擬輸入可以支持信號(hào)帶寬在1M SPS...

always 模塊的敏感表為電平敏感信號(hào)的電路可幾乎可以完成對(duì)所有組合邏輯電路的建模。always模塊的敏感列表為所有判斷條件信號(hào)和輸入信號(hào),但一定要注意敏感列表的完整性(注意通配符*的使用)。...

表1-1列出了7系列FPGA封裝中的管腳定義。注意:表1-12有單獨(dú)列出的專用通用用戶I/O,也有標(biāo)記IO_LXXY_ZZZ#或者I/O_XX_ZZZ_#標(biāo)識(shí)的多功能I/O,其中ZZZ代表一種或幾種附加的功能。如果多功能I/O不用做特殊用途,它們可以當(dāng)作普通I/O使用,這一點(diǎn)我們?cè)谟布O(shè)計(jì)時(shí)要注意。...

DC-SCM架構(gòu)定義了與CPU板互操作的輸入/輸出端口。DC-SCM服務(wù)器在HPM(主機(jī)處理器模塊)板上只有基本的中央計(jì)算元件(CPU)、高速存儲(chǔ)器和IO連接器,其他所有組件均在模塊化DC-SCM(安全、控制、管理)板上。...

調(diào)用內(nèi)部鎖相環(huán)由輸入的12M時(shí)鐘得到120MHZ工作時(shí)鐘,驅(qū)動(dòng)DDS控制模塊,輸出作為DAC的轉(zhuǎn)換時(shí)鐘。...

對(duì)于現(xiàn)今的FPGA芯片供應(yīng)商,在提供高性能和高集成度獨(dú)立FPGA芯片和半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)產(chǎn)品的同時(shí),還需要提供性能卓越且便捷易用的開(kāi)發(fā)工具。...

自動(dòng)電壓調(diào)節(jié)器(AVR)通常也稱為穩(wěn)壓器,它通過(guò)補(bǔ)償輸入電壓的波動(dòng)來(lái)調(diào)節(jié)供電電壓電平,在許多工業(yè)和住宅應(yīng)用中都很常見(jiàn)。例如,AVR被用于船舶發(fā)電機(jī)組、應(yīng)急電源和石油鉆井平臺(tái),以在電力需求波動(dòng)期間穩(wěn)定電壓電平。...

? ? Xilinx zynq系列FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)評(píng)估 本篇目錄 1. 內(nèi)存占用 ??? 1.1?FPGA程序中內(nèi)存的實(shí)現(xiàn)方式 ????1.2?Zynq的BRAM內(nèi)存大小 ????1.3?一個(gè)卷積操作占用的內(nèi)存 2. PipeCNN可實(shí)現(xiàn)性 ??? PipeCNN論文解析:用OpenCL實(shí)現(xiàn)FP...

FIFO是隊(duì)列機(jī)制中最簡(jiǎn)單的,每個(gè)接口上只有一個(gè)FIFO隊(duì)列,表面上看FIFO隊(duì)列并沒(méi)有提供什么QoS保證,甚至很多人認(rèn)為FIFO嚴(yán)格意義上不算做一種隊(duì)列技術(shù),實(shí)則不然,F(xiàn)IFO是其它隊(duì)列的基礎(chǔ)...

面對(duì)我國(guó)航天型號(hào)任務(wù)發(fā)展與需求的快速變化,空間站、深空探測(cè)、北斗導(dǎo)航等軟件密集型系統(tǒng)迅速擴(kuò)大,智能化、網(wǎng)絡(luò)化需求越來(lái)越多。...

遷移預(yù)覽部分列出了從源庫(kù)中標(biāo)識(shí)的元件類型組——作為元件類型() 或建議的文件夾結(jié)構(gòu)() 并包括這些元件 ( Components ) 的基于參數(shù)的網(wǎng)格視圖。網(wǎng)格中的參數(shù)值可以即時(shí)編輯,無(wú)需打開(kāi)和編輯源庫(kù)。下方的詳細(xì)信息區(qū)域包括來(lái)自當(dāng)前選定元件的附加信息——零部件選擇、模型和數(shù)據(jù)表等。...

但是作為從 Web 里誕生的框架,和 React Native/ Weex 不同的是,前者是先有了 Web 下的 React 和 Vue 實(shí)現(xiàn)之后才有的客戶端支持,而對(duì)于 Flutter 則是反過(guò)來(lái),先有客戶端實(shí)現(xiàn)之后才支持 Web 平臺(tái),這里其實(shí)可以和 Weex 做個(gè)簡(jiǎn)單對(duì)照。...

通過(guò)邏輯內(nèi)部定位發(fā)現(xiàn)丟包地點(diǎn)為下行SSRAM讀寫(xiě)處,即下行業(yè)務(wù)包寫(xiě)入SSRAM,再讀出后包內(nèi)容出錯(cuò)導(dǎo)致報(bào)文丟棄。FPGA外掛SSRAM結(jié)構(gòu)框圖見(jiàn)圖1,進(jìn)入FPGA內(nèi)部的上行業(yè)務(wù)和下行業(yè)務(wù)都需要通過(guò)各自的SSRAM進(jìn)行緩存來(lái)實(shí)現(xiàn)一些功能。...

對(duì)于testbench而言,端口應(yīng)當(dāng)和被測(cè)試的module一一對(duì)應(yīng)。端口分為input,output和inout類型產(chǎn)生激勵(lì)信號(hào)的時(shí)候,input對(duì)應(yīng)的端口應(yīng)當(dāng)申明為reg, output對(duì)應(yīng)的端口申明為wire,inout端口比較特殊,下面專門講解。...