完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

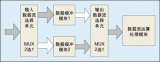

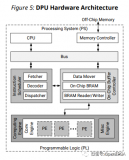

由于FPGA可以對算法進(jìn)行并行化,所以FPGA 非常適合在可編程邏輯中實(shí)現(xiàn)數(shù)學(xué)運(yùn)算。...

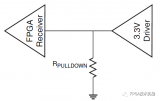

Xilinx 7系列FPGA IO Bank分為HP Bank和HR Bank,HP IO接口電壓范圍為1.2V~1.8V,可以實(shí)現(xiàn)高性能,HR IO接口電壓范圍為1.2V~3.3V。...

在FPGA設(shè)計(jì)中,當(dāng)復(fù)位整個(gè)系統(tǒng)或功能模塊時(shí),需要將先關(guān)寄存器被清零或者賦初值,以保證整個(gè)系統(tǒng)或功能運(yùn)行正常。在大部分的設(shè)計(jì)中,我們經(jīng)常用“同步復(fù)位”或“異步復(fù)位”直接將所有的寄存器全部復(fù)位,這部分可能大家都習(xí)以為常。但實(shí)際上,是否需要每個(gè)寄存器都進(jìn)行復(fù)位呢?這是一個(gè)值得探討的問題。...

在FPGA設(shè)計(jì)中,復(fù)位電路是非常重要的一部分,它能夠確保系統(tǒng)從初始狀態(tài)開始啟動(dòng)并保證正確運(yùn)行。本文將分別介紹FPGA中三種常用復(fù)位電路:同步復(fù)位、異步復(fù)位和異步復(fù)位同步釋放,以及相應(yīng)的Verilog代碼示例。...

Xilinx和數(shù)據(jù)接口相關(guān)的常用約束有Period、OFFSET_IN_BEFORE、OFFSET_IN_AFTER、OFFSET_OUT_BEFORE 和 OFFSET_OUT_AFTER;...

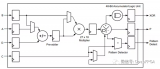

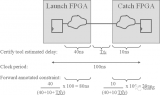

SoC的頂層的約束適用于FPGA到其各自時(shí)鐘域中的各個(gè)Flip_Flop,如果定義了跨時(shí)鐘域,也適用于FPGA之間。當(dāng)我們可以確保每個(gè)FPGA邊界都有一個(gè)IOFF,它與SoC中相應(yīng)的元素對齊時(shí),這一點(diǎn)對于性能而言非常重要。...

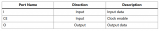

EFX_GBUFCE既可以讓GPIO走全局時(shí)鐘網(wǎng)絡(luò)也可以用于為時(shí)鐘添加使能控制,當(dāng)并不是隨時(shí)需要該時(shí)鐘時(shí)可以把時(shí)鐘禁止以節(jié)省功耗。...

FPGA 名為現(xiàn)場可編程門陣列,是一種硬件可重構(gòu)的集成電路芯片,現(xiàn)場可編程性是FPGA的最大特點(diǎn)。...

本次針對的 MNIST 數(shù)據(jù)集是一個(gè)非常小的數(shù)據(jù)集,圖像大小為 28×28。此外,該模型是一個(gè)非常輕量級的網(wǎng)絡(luò)模型。如果將這些做成更真實(shí)的數(shù)據(jù)模型,計(jì)算規(guī)模會(huì)發(fā)生如下變化。...

FPGA原型在數(shù)字芯片設(shè)計(jì)中非常重要,因?yàn)橄啾扔梅抡嫫鳎蛘呒铀倨鞯葋砼芊抡妫現(xiàn)PGA的運(yùn)行速度,更接近真實(shí)芯片,可以配合軟件開發(fā)者來進(jìn)行底層軟件的開發(fā)。這一流片前的軟硬件的協(xié)同開發(fā),是其最不可替代的地方。...

當(dāng)SoC的規(guī)模在一片F(xiàn)PGA中裝不下的時(shí)候,我們通常選擇多片F(xiàn)PGA原型驗(yàn)證的平臺(tái)來承載整個(gè)SoC系統(tǒng)。...

量化是權(quán)重或激活(每層的輸入和輸出)中比特的減少,通常在 fp32 中構(gòu)建。...

憑借更高的邏輯密度、更快的接口、更大的內(nèi)部存儲(chǔ)和先進(jìn)的互連,最新推出的MachXO5T-NX系列將萊迪思在控制FPGA領(lǐng)域長期以來的優(yōu)勢,擴(kuò)展到了企業(yè)網(wǎng)絡(luò)、機(jī)器視覺和工業(yè)物聯(lián)網(wǎng)等領(lǐng)域更廣泛的控制功能設(shè)計(jì)和應(yīng)用中,再次鑄就了安全控制FPGA的新里程碑。...

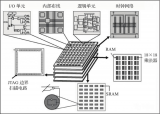

早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內(nèi)部buffer、LE、RAM構(gòu)建而成,LE由LUT(查找表)和D觸發(fā)器構(gòu)成,RAM也往往容量非常小。...

蜂鳴器是一種一體化結(jié)構(gòu)的電子訊響器,采用直流電壓供電,廣泛應(yīng)用于計(jì)算機(jī)、打印機(jī)、復(fù)印機(jī)、報(bào)警器、電子玩具、汽車電子設(shè)備、電話機(jī)、定時(shí)器等電子產(chǎn)品中作發(fā)聲器件。...

SLAM(同步定位和地圖繪制)在自動(dòng)駕駛、AGV 和無人機(jī)等各種應(yīng)用中引起了人們的廣泛關(guān)注。...

多片F(xiàn)PGA原型驗(yàn)證系統(tǒng)的拓?fù)溥B接方式各不相同,理想的多片F(xiàn)PGA原型驗(yàn)證系統(tǒng)應(yīng)該可以靈活配置,可以使用其相應(yīng)的EDA工具...

FPGA 為系統(tǒng)設(shè)計(jì)提供了極其靈活的可編程平臺(tái)。包含 IP 內(nèi)核、硬件平臺(tái)、演示設(shè)計(jì)、驅(qū)動(dòng)程序和軟件的綜合解決方案包使設(shè)計(jì)人員能夠縮短開發(fā)周期,同時(shí)降低設(shè)計(jì)的復(fù)雜性。...

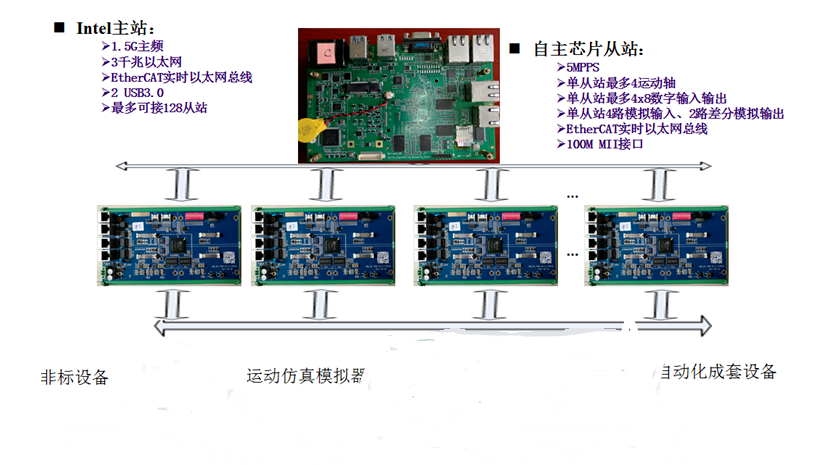

PLC的主機(jī)部分由中央處理器、輸入/輸出接口(I/0接口)通信、擴(kuò)展接口、儲(chǔ)存器、設(shè)備接口和電源等部分構(gòu)成。其中,基于京微齊力FPGA HME-M7和舜銘存儲(chǔ)鐵電存儲(chǔ)器PB85RS2MC的PLC系統(tǒng)已成為最佳解決方案。...

隨著FPGA對時(shí)序和性能的要求越來越高,高頻率、大位寬的設(shè)計(jì)越來越多。在調(diào)試這些FPGA樣機(jī)時(shí),需要從寫代碼時(shí)就要小心謹(jǐn)慎,否則寫出來的代碼可能無法滿足時(shí)序要求。...