完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

上文XILINX FPGA IP之Clocking Wizard詳解說(shuō)到時(shí)鐘IP的支持動(dòng)態(tài)重配的,本節(jié)介紹通過(guò)DRP進(jìn)行MMCM PLL的重新配置。...

鎖相環(huán)基本上是每一個(gè)fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時(shí)鐘資源對(duì)xilinx fpga的底層時(shí)鐘資源做過(guò)說(shuō)明,但是對(duì)于fpga的應(yīng)用來(lái)說(shuō),使用Clocking Wizard IP時(shí)十分方便的。...

在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。...

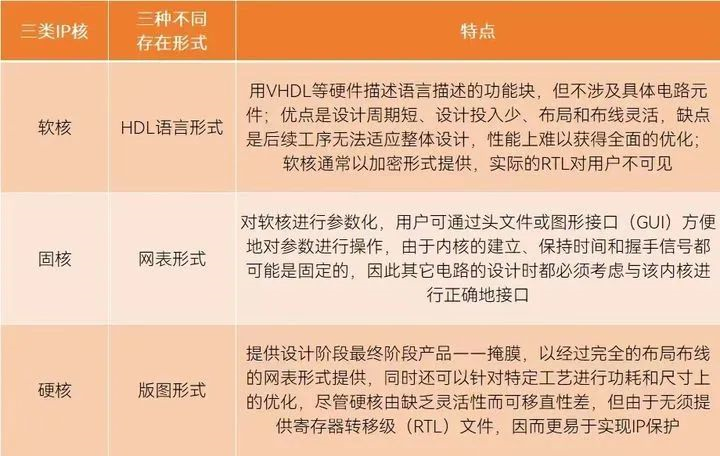

現(xiàn)今的FPGA設(shè)計(jì)規(guī)模越來(lái)越龐大,功能越來(lái)越復(fù)雜,因此FPGA設(shè)計(jì)的每個(gè)部分都從頭開(kāi)始著手是不切實(shí)際的。...

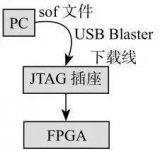

我們所說(shuō)的FPGA配置電路,一方面要完成從PC上把bit文件下載到FPGA或存儲(chǔ)器的任務(wù),另一方面則要完成FPGA上電啟動(dòng)時(shí)加載配置數(shù)據(jù)的任務(wù)。...

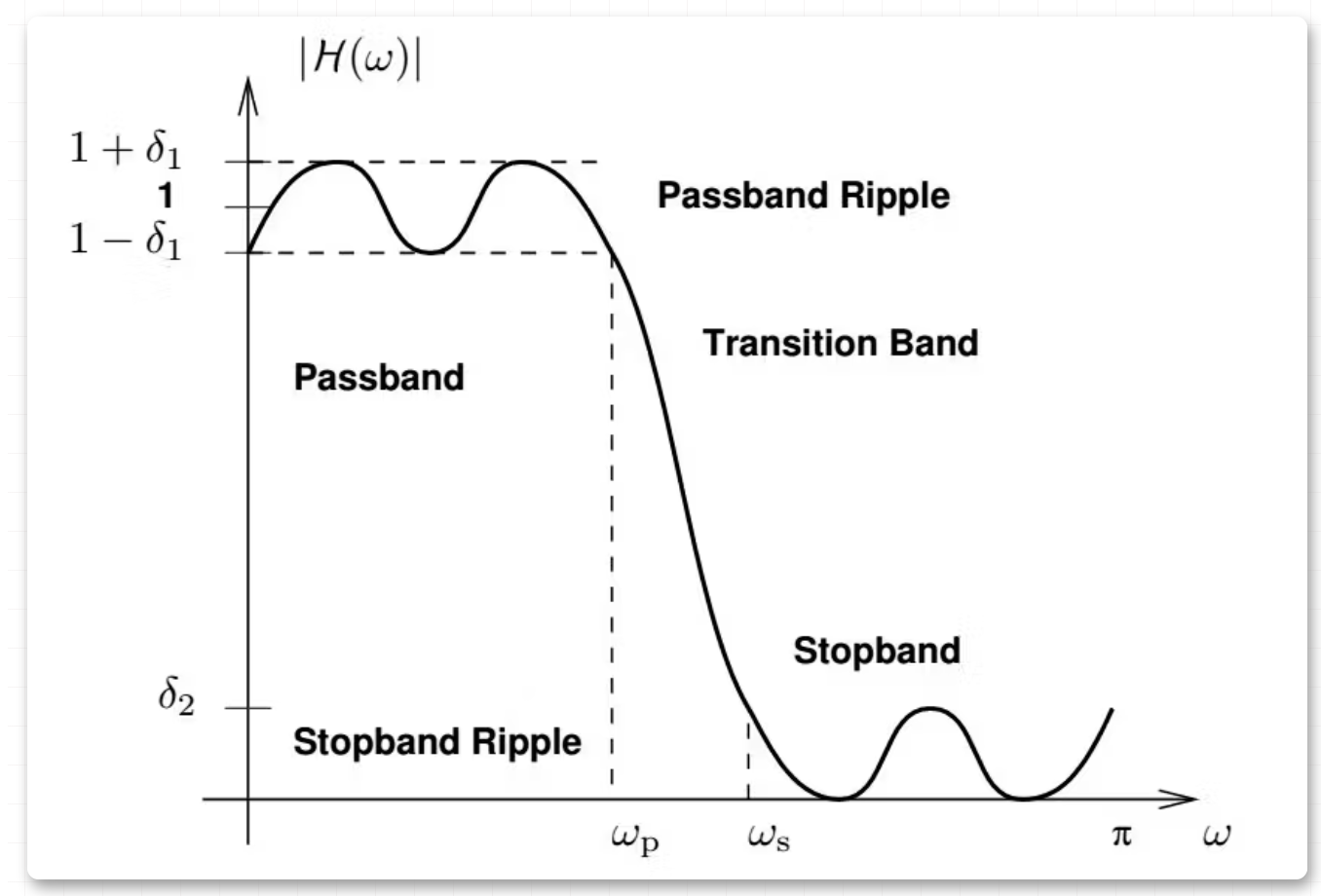

不起眼的 FIR 濾波器是 FPGA 數(shù)字信號(hào)處理中最基本的模塊之一,因此了解如何將具有給定抽頭數(shù)及其相應(yīng)系數(shù)值的基本模塊組合在一起非常重要。...

在FPGA設(shè)計(jì)中,時(shí)序約束的設(shè)置對(duì)于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的基礎(chǔ)知識(shí)。...

FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),F(xiàn)PGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間。...

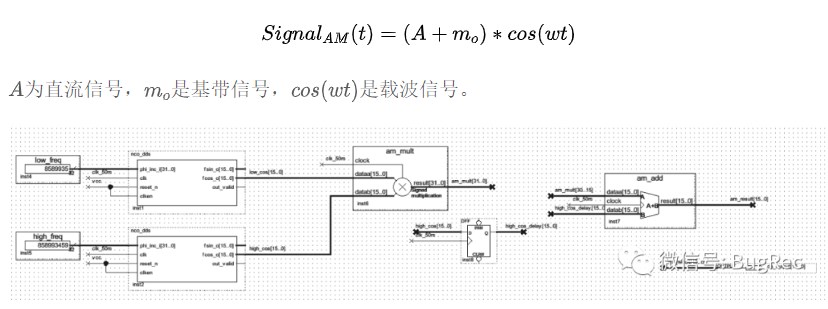

首先,為什么是AM信號(hào)的調(diào)制過(guò)程,是因?yàn)樵诙虝r(shí)間情況下,AM信號(hào)的實(shí)現(xiàn)相對(duì)簡(jiǎn)單,而且上述提到的幾個(gè)模塊都可以得到使用和驗(yàn)證。...

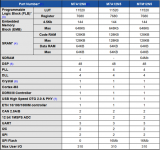

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實(shí)現(xiàn)某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過(guò)編程來(lái)實(shí)現(xiàn)一定的邏輯功能。...

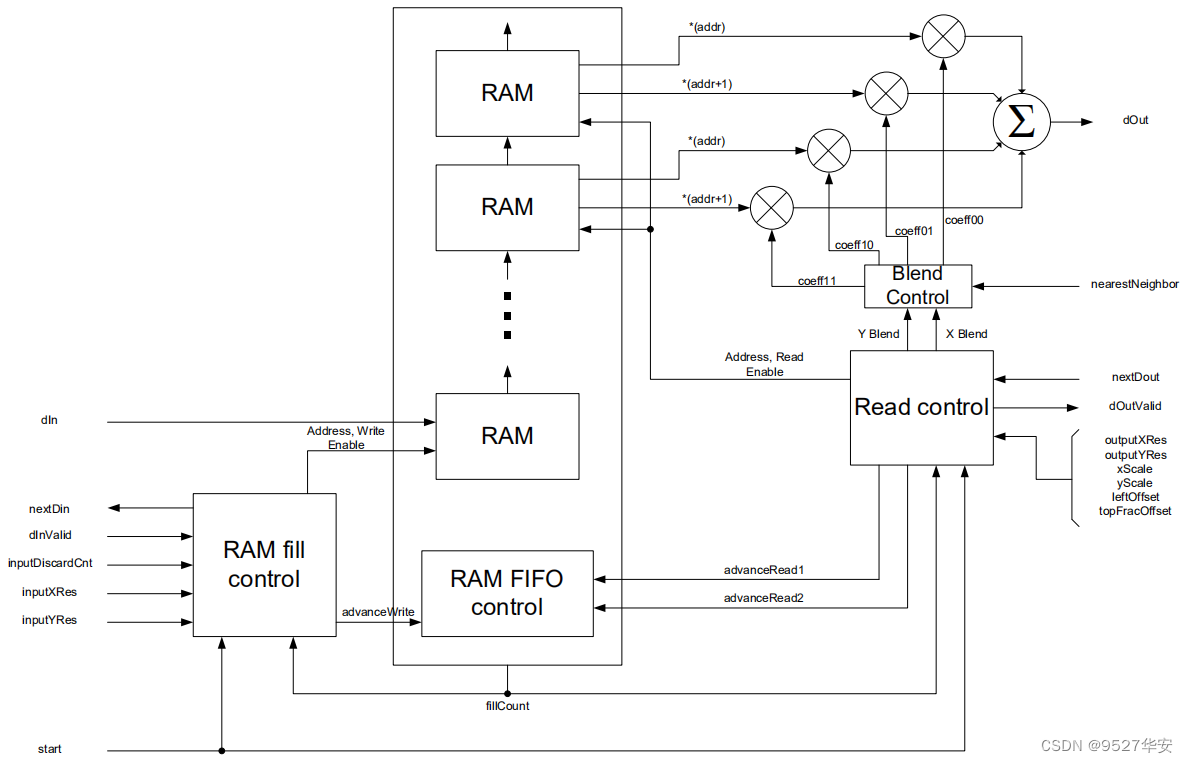

本設(shè)計(jì)將常用的雙線性插值和鄰域插值算法融合為一個(gè)代碼中,通過(guò)輸入?yún)?shù)選擇某一種算法...

設(shè)計(jì)中用了個(gè)localparam,定義某個(gè)參數(shù),想在tb中修改這個(gè)localparam的值,除了就是例化的時(shí)候引入進(jìn)去,還有啥辦法可以修改這個(gè)值?force這個(gè)語(yǔ)句只能對(duì)信號(hào)起作用。...

多片F(xiàn)PGA之間的互連,經(jīng)常提到多路復(fù)用的概念,也經(jīng)常提到TDM的概念...

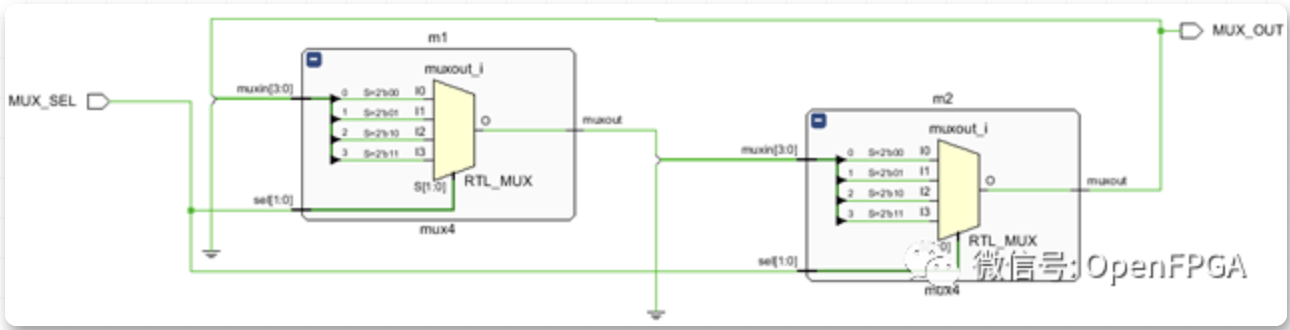

多片F(xiàn)PGA之間的互連,經(jīng)常提到多路復(fù)用的概念,也經(jīng)常提到TDM的概念,正確理解多路復(fù)用在多片F(xiàn)PGA原型驗(yàn)證系統(tǒng)中的機(jī)理,尤其是時(shí)序機(jī)制,對(duì)于我們正確看待和理解多片F(xiàn)PGA原型系統(tǒng)的性能有很好的促進(jìn)作用。下圖是一個(gè)使用多路復(fù)用器后接采樣FF的多路復(fù)用解決方案的示例。...

本文詳細(xì)描述了FPGA實(shí)現(xiàn)圖像去霧的實(shí)現(xiàn)設(shè)計(jì)方案,采用暗通道先驗(yàn)算法實(shí)現(xiàn),并利用verilog并行執(zhí)行的特點(diǎn)對(duì)算法進(jìn)行了加速;...

新一代SoC FPGA憑借其強(qiáng)大的并行處理數(shù)據(jù)的能力和實(shí)時(shí)性的特點(diǎn)在AIoT領(lǐng)域發(fā)揮著獨(dú)特的作用。隨著集成電路的發(fā)展,SoC FPGA的性能不斷提高,同時(shí)較為先進(jìn)的控制理論和控制算法的成熟。...

由傳輸門和兩個(gè)反相器組成一個(gè)循環(huán)電路(鎖存器),再由前后兩級(jí)鎖存器按主從結(jié)構(gòu)連接而成。...

AD轉(zhuǎn)換就是模數(shù)轉(zhuǎn)換,顧名思義,就是把模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)。我們所用的模數(shù)轉(zhuǎn)換芯片是ADC0809。...

本文列出了FPGA設(shè)計(jì)中常見(jiàn)的十個(gè)錯(cuò)誤。我們收集了 FPGA 工程師在其設(shè)計(jì)中犯的 10 個(gè)最常見(jiàn)錯(cuò)誤,并提供了解決方案的建議和替代方案。...