完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

可編程邏輯陣列(Programmable Logic Array, PLA):PLA是最早的可編程邏輯器件之一,由與非門陣列和或門陣列組成,通過編程配置來實現特定的邏輯功能。...

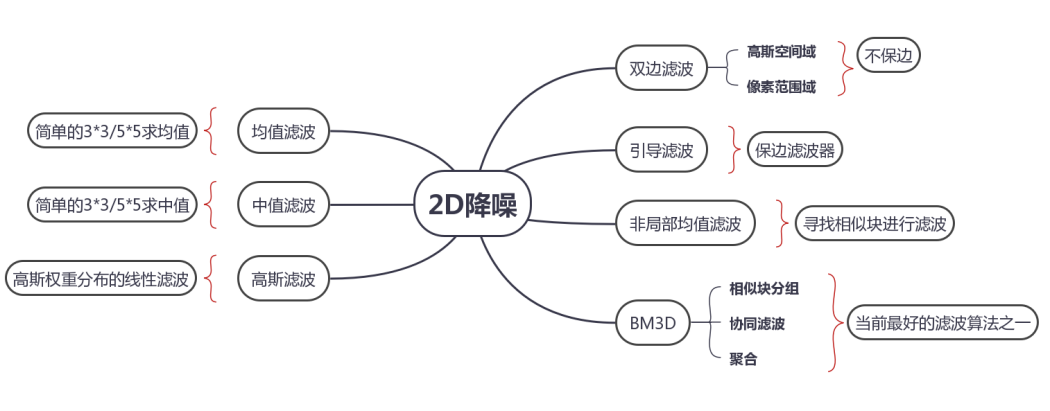

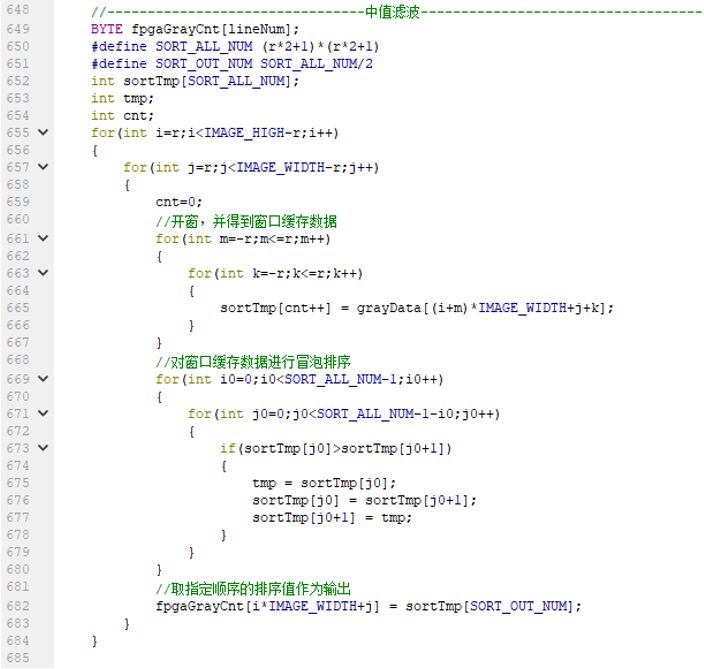

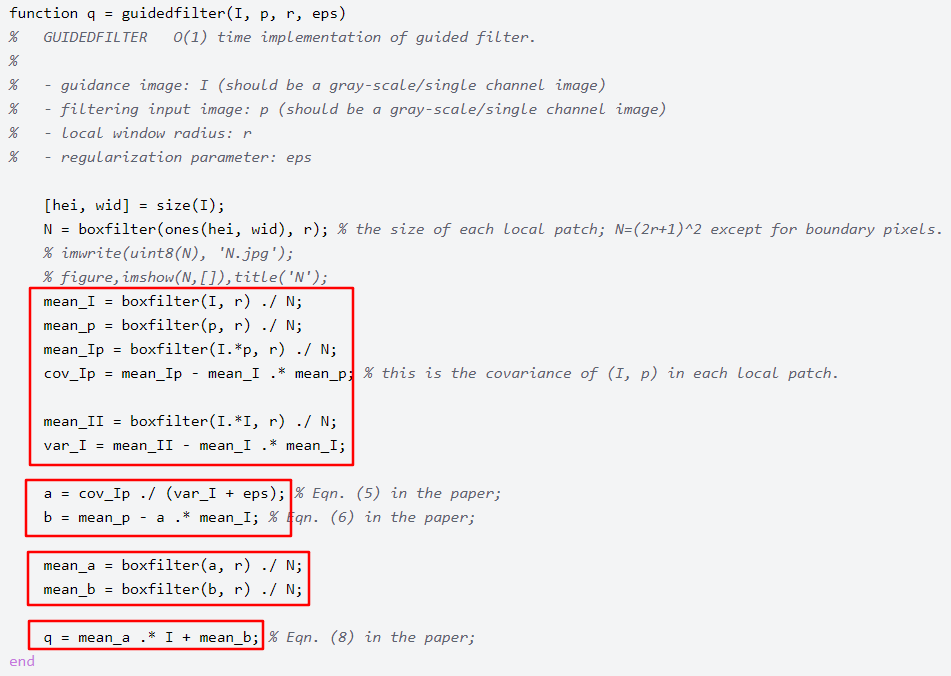

圖像降噪處理主要分為2D(空域)與3D降噪(時域/多幀),而2D降噪由于相關的實現算法豐富,效果各異,初學入門有著豐富的研究價值。...

VGA接口是一種D型接口,上面共有15針孔,分成三排,每排五個。其中比較重要的是3根RGB彩色分量信號和2根掃描同步信號HSYNC和VSYNC針。...

里面ChatGPT的回答,第一章作為基礎部分,就一筆帶過了。主要就是一些器件介紹,語法和設計方法,這部分也是最容易掌握的部分。...

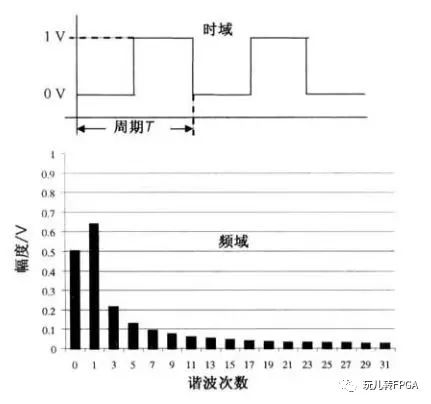

假設方波頻率為f0。橫軸諧波次數為0的柱狀圖代表直流分量的幅值,也就是方波的平均電壓(與占空比有關),諧波次數為1代表頻率為f0的正弦波分量的幅值,3代表,3*f0的正弦波分量幅值,以此類推。...

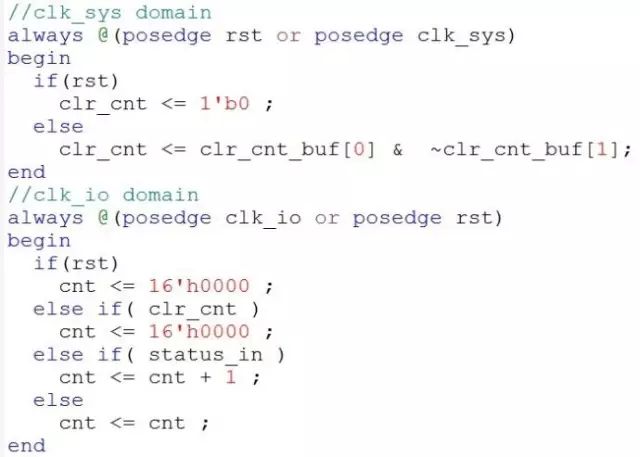

能不復位盡量不用復位,如何判斷呢?如果某個模塊只需要上電的時候復位一次,工作中不需要再有復位操作,那么這個模塊可以不用復位,用上電初始化所有寄存器默認值...

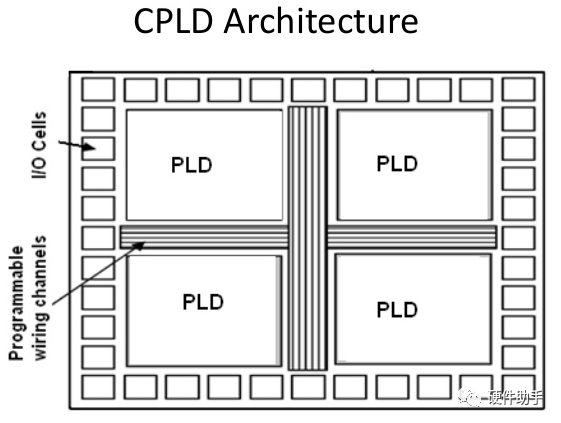

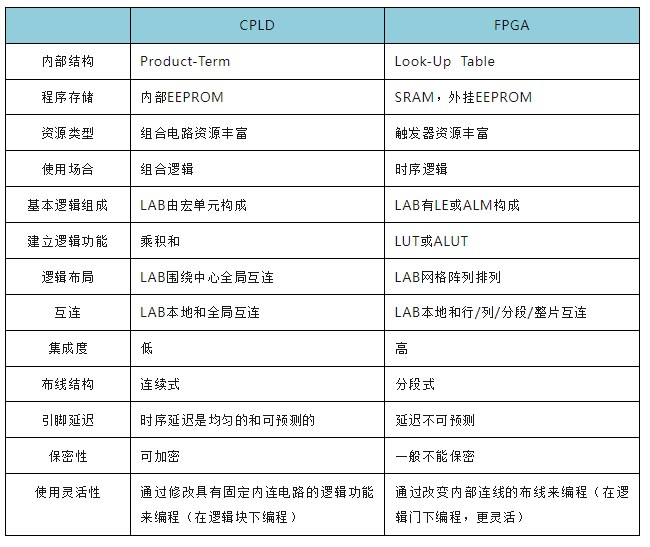

CPLD是復雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)的簡稱,兩者的功能基本相同,編程等過程也基本相同(燒寫文件不一樣,但是是由軟件自動產生的),只是芯片內部的實現...

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。...

新款 VP1902 具有 16 個 PCIe Gen5 x4 硬核 IP 模塊,而 VU19P 則具有 8 個 PCIe Gen4 x8。HPIO 到 XPIO 的升級應該會使芯片之間的延遲降低 36%。甚至還有一個很大的時鐘速度更新。這些新的升級意義重大,而不僅僅是擁有更多的可編程邏輯單元。...

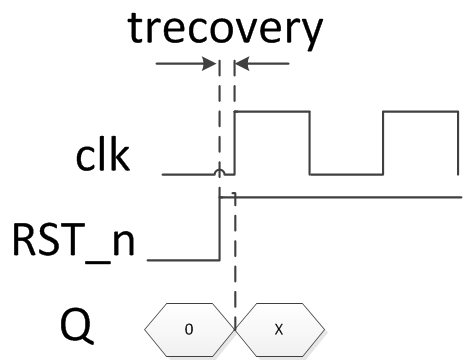

同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進行靜態時序分析,即不依賴于測試向量和動態仿真,而只根據每個邏輯門的最大延遲來檢查所有可能的時序違規路徑。...

LiteX 框架為創建 FPGA 內核/SoC、探索各種數字設計架構和創建完整的基于 FPGA 的系統提供了方便高效的基礎架構。...

現有一塊ADC連接到FPGA上,需要在FPGA上實現高速數據的讀取,那么第一步自然就是完成可靠的硬件連線...

CPLD規模雖小,其原理和設計方法和FPGA確是一樣的。輕視在CPLD上的投入,就有可能存在設計隱患,導致客戶使用產品時出現故障,從而給公司帶來不可挽回的信譽損失。...

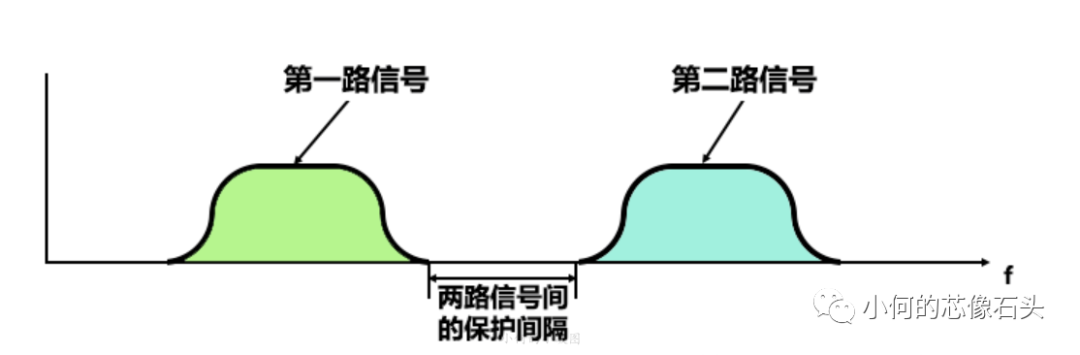

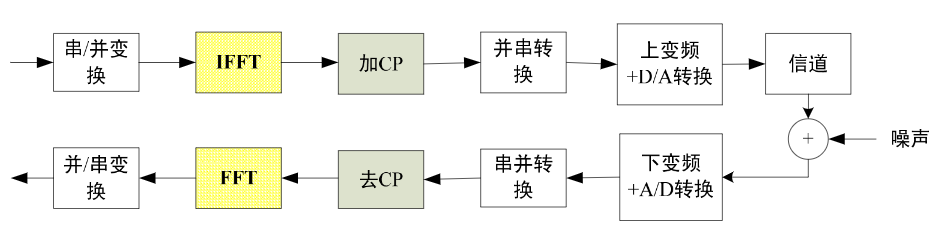

介紹除了OFDM外,一個完整通信鏈路中所需的其他環節,給出發射機鏈路和接收機鏈路的整體框圖,最后結合802.11a介紹相關技術指標。...

fromwiki:調制是將傳送資料對應于載波變化的動作,可以是載波的相位、頻率、幅度、或是其組合。...