完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

Allegro提供了一個(gè)集成、方便、強(qiáng)大的層疊設(shè)計(jì)與阻抗計(jì)算控制的工具,叫做Cross Section。如下圖所示,可以非常直觀地進(jìn)行材料選擇,參數(shù)確定,然后得到最終阻抗結(jié)果。 其中各選項(xiàng)的含義:...

按電路模塊進(jìn)行布局,實(shí)現(xiàn)同一功能的相關(guān)電路稱為一個(gè)模塊,電路模塊中的元件應(yīng)采用就近集中原則,同時(shí)數(shù)字電路和模擬電路分開。...

本文說(shuō)明如何利用ADAS3022來(lái)替換模擬前端(AFE)級(jí),從而降低復(fù)雜性,解決多通道數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)中遇到的諸多難題。 這種高性能器件具有多個(gè)輸入范圍,非常適合高精度工業(yè)、儀器、電力線和醫(yī)療數(shù)據(jù)采集卡應(yīng)用,可以降低成本和加快產(chǎn)品面市,同時(shí)占用空間很小,易于使用,在1 MSPS速率下提供真正的16位...

選 擇PCB板材必須在滿足設(shè)計(jì)需求、可量產(chǎn)性、成本中間取得平衡點(diǎn)。簡(jiǎn)單而言,設(shè)計(jì)需求包含電氣和結(jié)構(gòu)可靠性這兩部分。通常在設(shè)計(jì)非常高速的PCB板子(大 于GHz的頻率)時(shí)這板材問(wèn)題會(huì)比較重要。...

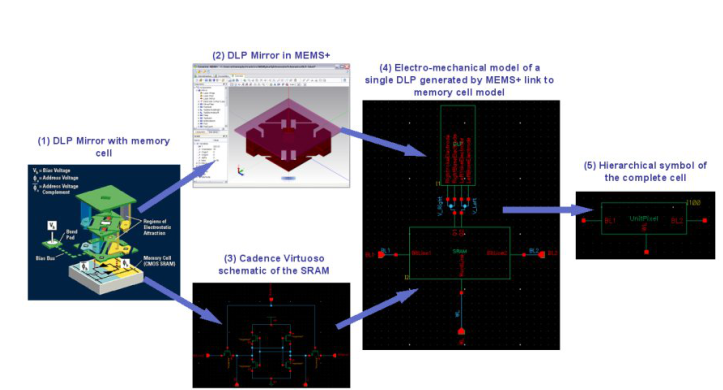

伴隨著傳感技術(shù)在汽車和消費(fèi)電子產(chǎn)品的迅速普及,微機(jī)電系統(tǒng)(MEMS)在最近幾年已進(jìn)入主流。為了控制及信號(hào)調(diào)理,基于MEMS 的傳感器必然需要密切耦合的電子電路。電子電路要么獨(dú)立于MEMS,要么和MEMS 在一個(gè)裸片中嵌入到模擬/混合信號(hào)集成電路中。...

本文主要對(duì)EDA技術(shù)的簡(jiǎn)單介紹及特點(diǎn)分析。EDA在20世紀(jì)60年代中期從計(jì)算機(jī)輔助設(shè)計(jì)(CAD)、計(jì)算機(jī)輔助制造(CAM)、計(jì)算機(jī)輔助測(cè)試(CAT)和計(jì)算機(jī)輔助工程(CAE)的概念發(fā)展而來(lái)的。EDA技術(shù)就是以計(jì)算機(jī)為工具,設(shè)計(jì)者在EDA軟件平臺(tái)上,用硬件描述語(yǔ)言VerilogHDL完成設(shè)計(jì)文件,然后...

本文主要介紹了一種基于EDA技術(shù)的出租車計(jì)費(fèi)系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn),采用EDA技術(shù)的層次化設(shè)計(jì)方法設(shè)計(jì)出租車計(jì)費(fèi)器,用VHDL編寫各個(gè)功能模塊,實(shí)現(xiàn)底層設(shè)計(jì);用原理圖輸入方式描述各模塊間的關(guān)系,實(shí)現(xiàn)頂層設(shè)計(jì)。...

Agilent ADS(Advanced Design System)軟件是在HP EESOF系列EDA軟件基礎(chǔ)上發(fā)展完善起來(lái)的大型綜合設(shè)計(jì)軟件,是美國(guó)安捷倫公司開發(fā)的大型綜合設(shè)計(jì)軟件,是為系統(tǒng)和電路工程師提供的可開發(fā)各種形式的射頻設(shè)計(jì),對(duì)于通信和航天/防御的應(yīng)用,從最簡(jiǎn)單到最復(fù)雜,從離散射頻/微波...

所謂探索性數(shù)據(jù)分析,是指對(duì)已有的數(shù)據(jù)(特別是調(diào)查或觀察得來(lái)的原始數(shù)據(jù))在盡量少的先驗(yàn)假定下進(jìn)行探索,通過(guò)作圖、制表、方程擬合、計(jì)算特征量等手段探索數(shù)據(jù)的結(jié)構(gòu)和規(guī)律的一種數(shù)據(jù)分析方法。...

PrimeTime 進(jìn)行靜態(tài)時(shí)序分析時(shí)把整個(gè)芯片按照時(shí)鐘分成許多時(shí)序路徑。路徑的起點(diǎn)是時(shí)序單元的輸出引腳或是設(shè)計(jì)的輸入端口,路徑的終點(diǎn)是時(shí)序單元的輸入引腳或是設(shè)計(jì)的輸出端口。根據(jù)起點(diǎn)和終點(diǎn)的不同,可將邏輯電路分解為圖1中用虛線表示的四種路徑,分別代表了以下四種類型: 路徑1起始于輸入端口,終止于時(shí)序...

不同低功耗技術(shù)的EDA支持是支離破碎的,結(jié)果設(shè)計(jì)師不得不通過(guò)一系列特殊手段定義低功耗功能。更重要的是,設(shè)計(jì)的可預(yù)測(cè)性和驗(yàn)證變得極其困難。同時(shí),由于設(shè)計(jì)上的復(fù)雜度以及以前缺乏EDA自動(dòng)化手段的原因,工程設(shè)計(jì)團(tuán)隊(duì)面臨著手工分析和運(yùn)用這些技巧的難題,而且也沒(méi)把握在不影響性能的條件下滿足功耗預(yù)算目標(biāo)。...

利用VHDL語(yǔ)言設(shè)計(jì)一個(gè)簡(jiǎn)單的數(shù)字電路。原理框圖如圖1所示,該電路用于計(jì)數(shù)電路之前的控制信號(hào)產(chǎn)生,功能要求是對(duì)外部電路產(chǎn)生送入的clk(8Hz)信號(hào)進(jìn)行計(jì)數(shù),輸出信號(hào)送入控制電路周期性地產(chǎn)生3個(gè)信號(hào)控制后級(jí)計(jì)數(shù)電路,這三個(gè)信號(hào)分別是:...

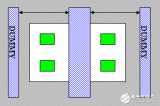

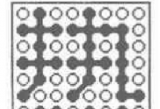

在IC版圖設(shè)計(jì)中除了要體現(xiàn)電路的邏輯或功能確保LVS驗(yàn)證正確外,還要增加一些與LVS(電路匹配)無(wú)關(guān)的圖形,以減小中間過(guò)程中的偏差,我們通常稱這些圖形為dummy layer。 dummy layer的用途: 1、保證可制造性,防止芯片在制造過(guò)程中由于曝光過(guò)渡或不足而導(dǎo)致的蝕刻失敗:如在tapeou...

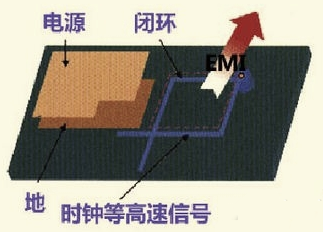

在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號(hào)線,走線需要進(jìn)行屏蔽處理,如果沒(méi)有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。...

一個(gè)良好的布局設(shè)計(jì)可優(yōu)化效率,減緩熱應(yīng)力并盡量小走線與元件之間噪聲作用。這切都 源于設(shè)計(jì)人員對(duì)電中流傳導(dǎo)路徑以及信號(hào)的理解。...

在驗(yàn)證領(lǐng)域,虛擬探針增強(qiáng)了硬件加速仿真作為數(shù)據(jù)中心資源對(duì)硬件設(shè)計(jì)人員和軟件開發(fā)人員的吸引力。...

焊盤(除表面貼焊盤外)的重疊,意味孔的重疊,在鉆孔工序會(huì)因?yàn)樵谝惶幎啻毋@孔導(dǎo)致斷鉆頭,導(dǎo)致孔的損傷。...

EDA工具層出不窮,目前進(jìn)入我國(guó)并具有廣泛影響的EDA軟件有:EWB、PSPICE、OrCAD、PCAD、Protel、 ViewLogic、Mentor、Graphics、Synopsys、LSIlogic、Cadence、MicroSim等等。...

采用傳統(tǒng)方法設(shè)計(jì)的漢字滾動(dòng)顯示器,通常需要使用單片機(jī)、存儲(chǔ)器和制約邏輯電路來(lái)進(jìn)行PCB(印制電路板)板級(jí)的系統(tǒng)集成。...

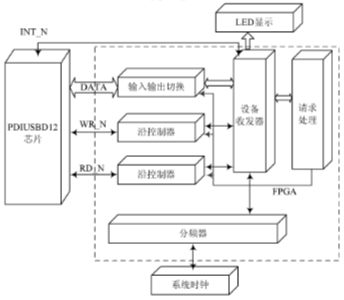

要想設(shè)計(jì)出更可靠更完善的加密硬件,必須采用新的計(jì)算機(jī)接口。而近年來(lái)發(fā)展快速的USB接口技術(shù)為硬件加密提供了一條很好的道路。...