資料介紹

盡管H.264/AVC承諾將此已有視頻編碼標準具有更高的編碼效率,它仍為系統架構師、DSP 工程師和硬件設計人員帶來了巨大的工程設計挑戰。H.264/AVC 標準引入了自 1990 年推出 H.261 之后視頻編碼標準演進過程中出現的大部分重大改變和算法間斷 (algorithmic discontinuities)。

盡管H.264/AVC承諾將此已有視頻編碼標準具有更高的編碼效率,它仍為系統架構師、DSP 工程師和硬件設計人員帶來了巨大的工程設計挑戰。H.264/AVC 標準引入了自 1990 年推出 H.261 之后視頻編碼標準演進過程中出現的大部分重大改變和算法間斷 (algorithmic discontinuities)。實現 H.264/AVC 編碼標準所需的算法計算復雜度、數據局部性,以及算法和數據并行性,常常會直接影響系統級別的整體架構決策。這種影響又會決定在廣播、視頻編輯、電話會議以及消費電子領域開發H.264/AVC解決方案所需的最終開發成本。

復雜度分析

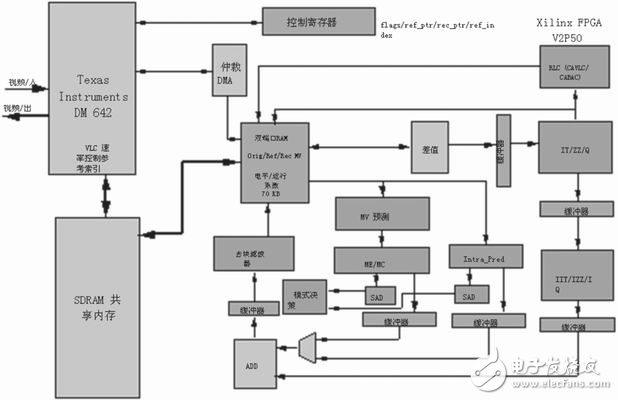

為了實現實時 H.264/AVC 標準清晰度 (SD) 或高清晰度 (HD) 分辯率編碼解決方案,系統架構師常常需要使用多個 FPGA 和可編程 DSP。為了說明所需計算的巨大復雜度,先探討一下 H.264/AVC 編碼器的典型運行時的周期要求。H.264/AVC 編碼器基于由聯合視頻工作組(JVT)提供的軟件模型,該工作組由來自 ITU-T 的視頻編碼專家組 (VCEG) 和 ISO/IEC 的運動圖像專家組 (MPEG) 的專家組成。

采用Intel的VTune軟件,在 Intel Pentium III 1.0 GHz 通用 CPU、512 MB 內存的平臺上運行,按照主要配置編碼解決方案實現 H.264/AVC SD,需要約 1,600 BOPS(每秒十億次運算)。

表 1 顯示了基于 Pentium III 通用處理器架構的 H.264/AVC 編碼器的復雜度的典型情況。請注意,在表 1 中,運動估計、宏塊/塊處理(包括模式決策),以及運動補償模塊是基本候選硬件加速單元。

然而,單憑計算復雜度并不能決定一個功能模塊是否應映射為硬件或是使其保持為軟件。為了評估在由 FPGA、可編程 DSP或通用主處理器混合組成的平臺上實現 H.264/AVC 編碼標準時,軟件和硬件分割的可行性,需要分析將會影響整體設計決策的大量架構問題。

數據局部性

在同步設計中,按照特定的順序和粒度訪問內存,同時根據延遲、總線競爭、對準、DMA 傳輸率以及所用內存的類型(如 ZBT 內存、SDRAM和 SRAM 等)使時鐘周期數降至最小的能力至關重要。數據局部性問題主要是由數據單元和算術單元(或處理引擎)之間的物理接口體現的。

數據并行性。

大多數信號處理算法都是對高度并行的數據進行操作(如 FIR 濾波)。單指令多數據 (SIMD) 和向量處理器對可被并行化或做成向量格式(或長數據寬度)的數據具有較高的處理效率。

FPGA可通過提供大量塊 RAM 支持大量極高總計帶寬要求來實現這一點。在新的 Xilinx Virtex-4 SX器件中,塊 RAM 的數量與 Xtreme DSP的邏輯片數緊密匹配(例如,SX25具有128個塊RAM,128個DSP邏輯片;SX35具有192個塊 RAM,192個DSP 邏輯片;SX55具有320個塊 RAM,512個DSP邏輯片)。

信號處理算法并行機制。

在典型的可編程 DSP 或通用處理器中,信號處理算法并行機制通常是指指令級并行 (ILP)。超長指令字 (VLIW) 處理器是此類采用ILP的機器中的一個例子,它將多條指令(ADD、MULT 及 BRA)組合起來,在一個周期內執行。處理器中高度流水線化的執行單元也是實現并行機制的典型硬件示例。現在已經有可編程DSP采用這種架構(如TI的TMS320C64x)。

但是,并非所有算法都能使用這種并行機制。遞歸算法,如 IIR 濾波、MPEG 1/2/4 中的變長編碼 (VLC)、上下文自適應變長編碼 (CAVLC),以及 H.264/AVC 中的上下文自適應二進制算術編碼 (CABAC),當映射到這些可編程 DSP 時,均無法達到最優且效率不高。這是因為數據遞歸阻礙了 ILP 的有效利用。作為取代方案,可在FPGA 結構中有效地構建專用硬件引擎。

計算復雜度。

可編程 DSP 受計算復雜度的限制,可通過處理器的時鐘速率來度量。在FPGA中實現的信號處理算法通常為計算密集型算法。其中的例子有運動估計中的絕對差值和 (SAD) 引擎以及視頻縮放。

通過將這些模塊映射到 FPGA 中,主處理器或可編程DSP就可有額外的周期來處理其他算法。此外,FPGA 結構還可以具有多時鐘域,從而允許選擇性硬件模塊根據各自的計算要求使用獨立的時鐘速度。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- H.264編碼原理 2次下載

- H.264視頻編碼標準英文資源匯總下載 21次下載

- 基于H.264編碼視頻的網絡傳輸跟蹤評價方法 0次下載

- 在嵌入式平臺PXA255上實現新一代視頻壓縮標準h.264編碼算法 1次下載

- 基于DM642的H.264編碼算法優化與實現 1次下載

- 新一代視頻壓縮編碼標準H.264-AVC(第2版)1 0次下載

- 基于嵌入式平臺的H264視頻編碼器的實現 87次下載

- 基于H.264與AVC標準的幀內預測算法 28次下載

- 基于H.264的立體視頻編碼方法 43次下載

- 基于H.264的無再損幀內編碼

- 基于DSP TMS320DM642的H.264視頻編碼的實現

- H.264視頻編碼在DM642上的實現與優化

- 如何在FPGA上實現H.264/AVC視頻編碼標準

- 新一代視頻編碼標準H.264在高速DSP平臺上的實現與優化(

- H.264是什么?H.264標準詳解

- 基于H.264實現最優重疊塊匹配加權窗的系數設計 3433次閱讀

- 基于VPM642板卡和DSP實現AVS解碼軟件的優化應用 3948次閱讀

- 帶有環路濾波的HEVC視頻解碼器的結構和應用實例分析 4162次閱讀

- 基于H.264解碼芯片的FPGA原型驗證平臺實現視頻控制模塊的設計 2626次閱讀

- 基于DE2開發板和NiosII處理器實現H.264編碼器的設計 2502次閱讀

- 矽海達科技SUE1 H.264編碼模塊介紹 1959次閱讀

- 矽海達科技SUE2 H.264編碼模塊介紹 2017次閱讀

- 矽海達科技SUE3 SDI H.264編碼模塊介紹 2176次閱讀

- 銳爾威視科技H.264百萬USB攝像頭模組規格 3039次閱讀

- fireflyH.264硬編碼&硬解碼簡介 3089次閱讀

- 基于塊匹配的高斯背景建模-ROI映射方法的FPGA和HEVC視頻編碼算法設計 2754次閱讀

- FFMPEG視頻編解碼流程 H.264硬件編解碼實現 1.9w次閱讀

- 新一代視頻壓縮標準“HEVC”:移動時代的核心技術 2504次閱讀

- H.264和AVS核心技術分析 1550次閱讀

- AVS視頻標準和H.264核心技術的區別 1947次閱讀

下載排行

本周

- 1DC電源插座圖紙

- 0.67 MB | 3次下載 | 免費

- 2AN-1267: 使用ADSP-CM408F ADC控制器的電機控制反饋采樣時序

- 1.41MB | 3次下載 | 免費

- 3AN158 GD32VW553 Wi-Fi開發指南

- 1.51MB | 2次下載 | 免費

- 4AN148 GD32VW553射頻硬件開發指南

- 2.07MB | 1次下載 | 免費

- 5AN111-LTC3219用戶指南

- 84.32KB | 次下載 | 免費

- 6AN153-用于電源系統管理的Linduino

- 1.38MB | 次下載 | 免費

- 7AN-283: Σ-Δ型ADC和DAC[中文版]

- 677.86KB | 次下載 | 免費

- 8SM2018E 支持可控硅調光線性恒流控制芯片

- 402.24 KB | 次下載 | 免費

本月

- 1ADI高性能電源管理解決方案

- 2.43 MB | 450次下載 | 免費

- 2免費開源CC3D飛控資料(電路圖&PCB源文件、BOM、

- 5.67 MB | 138次下載 | 1 積分

- 3基于STM32單片機智能手環心率計步器體溫顯示設計

- 0.10 MB | 130次下載 | 免費

- 4使用單片機實現七人表決器的程序和仿真資料免費下載

- 2.96 MB | 44次下載 | 免費

- 5美的電磁爐維修手冊大全

- 1.56 MB | 24次下載 | 5 積分

- 6如何正確測試電源的紋波

- 0.36 MB | 18次下載 | 免費

- 7感應筆電路圖

- 0.06 MB | 10次下載 | 免費

- 8萬用表UT58A原理圖

- 0.09 MB | 9次下載 | 5 積分

總榜

- 1matlab軟件下載入口

- 未知 | 935121次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關降壓/升壓雙向直流/直流轉換器 PCB layout 設計

- 1.48MB | 420062次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233088次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191367次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183335次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73810次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65988次下載 | 10 積分

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論