資料介紹

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端DSP信號處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

例如,由于數(shù)字信號處理應(yīng)用程序主要依賴于乘法累加器( MAC )操作, DSP處理器供應(yīng)商和FPGA供應(yīng)商通常將MACs每秒最高運(yùn)轉(zhuǎn)速度作為數(shù)字信號處理器性能好壞最簡單的評判方式。但僅僅通過MAC吞吐量來預(yù)測數(shù)字信號處理性能是有失公平的,對FPGA和DSP也一樣。這里有幾個原因。

MAC計算出來的FPGA性能指數(shù)總是假設(shè)硬連線的數(shù)字信號處理部件是在其最高時鐘速率運(yùn)行的。在實踐中,典型的FPGA設(shè)計將采用較低的速度。另一方面,使用硬連線原理并不是在FPGA上執(zhí)行實現(xiàn)MAC的唯一方法;另外MAC吞吐量可以通過使用可編程邏輯資源和分布式算法來實現(xiàn)。此外,并不是所有的信號處理算法都采用MAC密集型。例如,Viterbi譯碼,是電信應(yīng)用中的一個關(guān)鍵的DSP算法,并沒有用到MAC系統(tǒng)。

另一種用來評估信號處理性能的辦法,是使用普通的DSP功能(如FIR濾波器) 。但是,這種辦法也有缺點。其中一個問題是,每個供應(yīng)商通常使用不同的執(zhí)行方式來執(zhí)行這些功能,也許是使用不同的數(shù)據(jù)寬度、不同的算法或不同的執(zhí)行參數(shù)(如延遲)。這意味著,從不同的供應(yīng)商得出的結(jié)論一般都沒有可比性。此外,小的內(nèi)核功能通常不能作為有效的FPGA基準(zhǔn),因為在完整的FPGA應(yīng)用中執(zhí)行一個功能的方法往往是完全不同于你單獨執(zhí)行的功能。 (相對于處理器,這些小基準(zhǔn)通常在預(yù)測總體的DSP應(yīng)用程序性能時表現(xiàn)不錯。 )此外,經(jīng)過處理器或FPGA供應(yīng)商執(zhí)行的基準(zhǔn)往往缺乏獨立的核查,因此工程師很難對幾種設(shè)備作出比較。

幾年前BDTI公司就意識到建立獨立性是日益迫切需要的,確切來說,面向數(shù)字信號處理應(yīng)用采用蘋果對蘋果的方式來比較FPGA和處理器。 (見側(cè)欄:什么是BDTI ?)為了滿足這一需要, BDTI開發(fā)出一種新的面向應(yīng)用的基準(zhǔn), BDTI通訊基準(zhǔn)( OFDM )? ,這是基于正交頻分復(fù)用( OFDM )接收器。

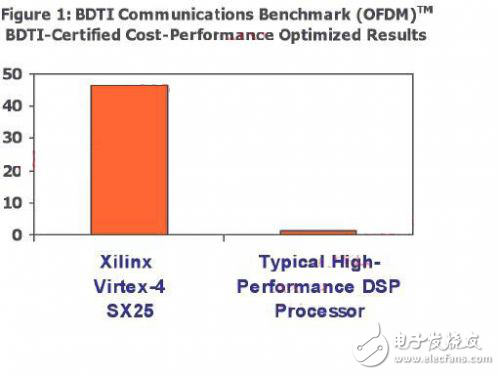

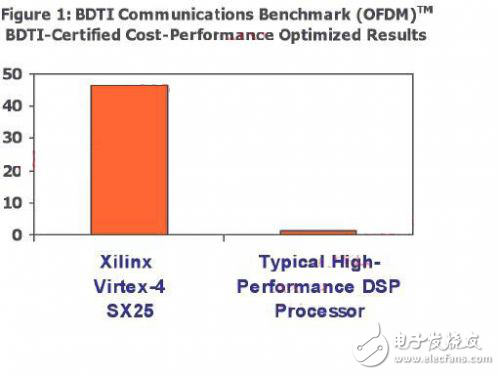

最近BDTI用BDTI通訊基準(zhǔn)( OFDM )來評估一些新的高性能FPGAs和DSP處理器。整套的標(biāo)準(zhǔn)測試結(jié)果和分析,現(xiàn)刊載于BDTI的報告“DSP的FPGAs實現(xiàn):第二版”。圖1顯示樣品歸一化,賽靈思SX25和典型的高性能DSP處理器的低成本結(jié)果。

正如該圖所示, BDTI公司的標(biāo)準(zhǔn)測試結(jié)果提供了一個戲劇性的證明,在高性能DSP應(yīng)用中使用FPGAs有潛在的成本優(yōu)勢——基于這一基準(zhǔn),SX25比一般的高性能DSP處理器更符合成本效益,而且不止一個數(shù)量級。

設(shè)計人員還需要了解所選擇的處理引擎,將如何影響它們的發(fā)展流程、實施工作和系統(tǒng)設(shè)計。出于這個原因, BDTI的報告探討了質(zhì)的因素,該因素影響決定是否使用一個FPGA ,數(shù)字信號處理,或兩者兼施,并提供指導(dǎo)如何作出明智的選擇。該報告強(qiáng)調(diào)的關(guān)鍵開放性問題,這將影響FPGA在高端的DSP應(yīng)用的長期成功,如FPGA的能量效率和FPGAs的新高層次合成工具的效率。

?

例如,由于數(shù)字信號處理應(yīng)用程序主要依賴于乘法累加器( MAC )操作, DSP處理器供應(yīng)商和FPGA供應(yīng)商通常將MACs每秒最高運(yùn)轉(zhuǎn)速度作為數(shù)字信號處理器性能好壞最簡單的評判方式。但僅僅通過MAC吞吐量來預(yù)測數(shù)字信號處理性能是有失公平的,對FPGA和DSP也一樣。這里有幾個原因。

MAC計算出來的FPGA性能指數(shù)總是假設(shè)硬連線的數(shù)字信號處理部件是在其最高時鐘速率運(yùn)行的。在實踐中,典型的FPGA設(shè)計將采用較低的速度。另一方面,使用硬連線原理并不是在FPGA上執(zhí)行實現(xiàn)MAC的唯一方法;另外MAC吞吐量可以通過使用可編程邏輯資源和分布式算法來實現(xiàn)。此外,并不是所有的信號處理算法都采用MAC密集型。例如,Viterbi譯碼,是電信應(yīng)用中的一個關(guān)鍵的DSP算法,并沒有用到MAC系統(tǒng)。

另一種用來評估信號處理性能的辦法,是使用普通的DSP功能(如FIR濾波器) 。但是,這種辦法也有缺點。其中一個問題是,每個供應(yīng)商通常使用不同的執(zhí)行方式來執(zhí)行這些功能,也許是使用不同的數(shù)據(jù)寬度、不同的算法或不同的執(zhí)行參數(shù)(如延遲)。這意味著,從不同的供應(yīng)商得出的結(jié)論一般都沒有可比性。此外,小的內(nèi)核功能通常不能作為有效的FPGA基準(zhǔn),因為在完整的FPGA應(yīng)用中執(zhí)行一個功能的方法往往是完全不同于你單獨執(zhí)行的功能。 (相對于處理器,這些小基準(zhǔn)通常在預(yù)測總體的DSP應(yīng)用程序性能時表現(xiàn)不錯。 )此外,經(jīng)過處理器或FPGA供應(yīng)商執(zhí)行的基準(zhǔn)往往缺乏獨立的核查,因此工程師很難對幾種設(shè)備作出比較。

幾年前BDTI公司就意識到建立獨立性是日益迫切需要的,確切來說,面向數(shù)字信號處理應(yīng)用采用蘋果對蘋果的方式來比較FPGA和處理器。 (見側(cè)欄:什么是BDTI ?)為了滿足這一需要, BDTI開發(fā)出一種新的面向應(yīng)用的基準(zhǔn), BDTI通訊基準(zhǔn)( OFDM )? ,這是基于正交頻分復(fù)用( OFDM )接收器。

最近BDTI用BDTI通訊基準(zhǔn)( OFDM )來評估一些新的高性能FPGAs和DSP處理器。整套的標(biāo)準(zhǔn)測試結(jié)果和分析,現(xiàn)刊載于BDTI的報告“DSP的FPGAs實現(xiàn):第二版”。圖1顯示樣品歸一化,賽靈思SX25和典型的高性能DSP處理器的低成本結(jié)果。

正如該圖所示, BDTI公司的標(biāo)準(zhǔn)測試結(jié)果提供了一個戲劇性的證明,在高性能DSP應(yīng)用中使用FPGAs有潛在的成本優(yōu)勢——基于這一基準(zhǔn),SX25比一般的高性能DSP處理器更符合成本效益,而且不止一個數(shù)量級。

設(shè)計人員還需要了解所選擇的處理引擎,將如何影響它們的發(fā)展流程、實施工作和系統(tǒng)設(shè)計。出于這個原因, BDTI的報告探討了質(zhì)的因素,該因素影響決定是否使用一個FPGA ,數(shù)字信號處理,或兩者兼施,并提供指導(dǎo)如何作出明智的選擇。該報告強(qiáng)調(diào)的關(guān)鍵開放性問題,這將影響FPGA在高端的DSP應(yīng)用的長期成功,如FPGA的能量效率和FPGAs的新高層次合成工具的效率。

?

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 基于FPGA和DSP的機(jī)載圖形顯示系統(tǒng) 36次下載

- HDLs設(shè)計FPGAs綜合與驗證設(shè)計 14次下載

- 為今天的多軌FPGAs和DSP提供動力,第2部分 5次下載

- 關(guān)于DSP-AD的參考文件 3次下載

- DSP中關(guān)于F2808的程序 4次下載

- 最新FPGA的DSP性能介紹 7次下載

- 揭秘FPGA的DSP性能 1次下載

- 基于FPGAs的DSP性能分析 1次下載

- 基于FPGA和DSP組合在無線基站中的應(yīng)用分析 0次下載

- xilinx FPGAs在工業(yè)中的應(yīng)用 26次下載

- DSP互連分析與FPGA實現(xiàn)

- Spartan-3A DSP FPGA Family: Da

- Spartan-3 Generation FPGAs應(yīng)用資料

- Virtex-5, Spartan-DSP FPGAs Ap

- Xtreme DSP選擇指南 (XtremeDSP Solu

- MCU、DSP和FPGA的區(qū)別 5123次閱讀

- FPGA中關(guān)于SPI的使用 925次閱讀

- FPGA設(shè)計中時序分析的基本概念 2751次閱讀

- Altera FPGA硬核浮點DSP模塊解決方案提高運(yùn)算性能 3646次閱讀

- 基于FPGA的自動化DSP開發(fā)流程 4309次閱讀

- 混合FPGA/DSP基平臺 是為無線基站提供一種有效設(shè)計的方法 917次閱讀

- 如何提升Virtex-5 FPGA更高的性能 ExpressFabric架構(gòu)介紹 1916次閱讀

- 以嵌入式DSP模塊和FPGA構(gòu)架為基礎(chǔ)的提高無線信號處理性能的子系統(tǒng)設(shè)計 863次閱讀

- 關(guān)于多電壓軌FPGA和DSP應(yīng)用的電源解決方案全解 1229次閱讀

- Xilinx Kintex UltraScale FPGA DSP開發(fā)套件主要性能和優(yōu)勢 2906次閱讀

- FPGA會取代DSP嗎?FPGA與DSP區(qū)別介紹 3.6w次閱讀

- 如何將MCU應(yīng)用到FPGA中:關(guān)于FPGA(1) 3930次閱讀

- 基于FPGA和DSP的噴油器霧化粒徑測量系統(tǒng)的設(shè)計 2032次閱讀

- 一文了解FPGA與DSP的區(qū)別、特點及用途 2.9w次閱讀

- FPGA+DSP的高速通信接口設(shè)計與實現(xiàn) 7762次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1489次下載 | 免費(fèi)

- 2單片機(jī)典型實例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費(fèi)

- 6基于AT89C2051/4051單片機(jī)編程器的實驗

- 0.11 MB | 4次下載 | 免費(fèi)

- 7基于單片機(jī)和 SG3525的程控開關(guān)電源設(shè)計

- 0.23 MB | 3次下載 | 免費(fèi)

- 8基于單片機(jī)的紅外風(fēng)扇遙控

- 0.23 MB | 3次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開關(guān)電源設(shè)計實例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537791次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論