軟件開(kāi)發(fā)者應(yīng)該明白許多參數(shù)都會(huì)影響接口的性能。即使對(duì)IP規(guī)范以及SOC設(shè)計(jì)團(tuán)隊(duì)開(kāi)發(fā)的特定配置進(jìn)行了最為謹(jǐn)慎的研究,也無(wú)法保證軟件開(kāi)發(fā)者能夠按照支持實(shí)際IP模塊的方式,對(duì)IP進(jìn)行編程。在最優(yōu)情況下,這些故障可以在軟件開(kāi)發(fā)階段檢測(cè)出來(lái)。在最壞情況下,這些故障可能在SOC實(shí)際使用過(guò)程中出現(xiàn)。

軟件開(kāi)發(fā)者還需要一份關(guān)于PHY的陳述,以便與其他設(shè)備驗(yàn)證互操作性和性能。關(guān)于高級(jí)工藝節(jié)點(diǎn)日益嚴(yán)重的問(wèn)題,是半導(dǎo)體公司用于構(gòu)建控制器與PHY完整原型的獨(dú)立PHY芯片越來(lái)越少。設(shè)計(jì)人員必須依賴他們的IP供應(yīng)商為軟件團(tuán)隊(duì)提供充足的PHY卡。在很多情況下,IP提供商只根據(jù)特定客戶的要求通過(guò)特定方式,提供用于新PHY IP驗(yàn)證實(shí)現(xiàn)與特性的PHY卡。獲得PHY(作為IP原型套件中標(biāo)準(zhǔn)部件)是一個(gè)獲得完整原型解決方案的可靠方法。

為了簡(jiǎn)化流程,雖然硬件團(tuán)隊(duì)改進(jìn)了配置設(shè)定,軟件團(tuán)隊(duì)可以使用DesignWare IP原型套件或者DesignWare IP虛擬開(kāi)發(fā)工具包(VDK)查看軟件棧(圖6)。軟件開(kāi)發(fā)者可以使用這兩種工具通過(guò)使用相關(guān)參考軟件開(kāi)發(fā)、調(diào)試、優(yōu)化IP驅(qū)動(dòng)軟件。

DesignWare IP原型套件不僅可以處理驅(qū)動(dòng)軟件的功能行為,還可以與連接到PHY子卡的外部設(shè)備共同驗(yàn)證軟件性能。由于硬件團(tuán)隊(duì)可以為HAPS-DX系統(tǒng)(IP原型FPGA系統(tǒng))提供燒錄文件,盡早確定目標(biāo)有很多益處,如果新的硬件就緒,軟件團(tuán)隊(duì)可以再次嘗試新的硬件配置。即使團(tuán)隊(duì)位于遠(yuǎn)程,這種互動(dòng)方法仍然可行。由于DesignWare IP原型套件價(jià)格可以接受,并且可以做到開(kāi)箱即可使用,可以輕松適用于SOC與軟件開(kāi)發(fā)團(tuán)隊(duì)。DesignWare IP原型套件首次組裝后,軟件開(kāi)發(fā)者可以在他們的主機(jī)上使用最優(yōu)開(kāi)發(fā)環(huán)境,或者在ARC軟件開(kāi)發(fā)平臺(tái)上編輯軟件。將新燒錄文件下載到HAPS-DX板上后,這個(gè)過(guò)程十分迅速,并且每天可以進(jìn)行數(shù)百個(gè)軟件的調(diào)試。

DesignWare IP虛擬開(kāi)發(fā)工具包(VDK)提供了一種模擬模型(虛擬原型),可以使用ARMv8 Cortex big.LITTLE處理系統(tǒng)(四核Cortex-A57及四核Cortex-A53處理器)呈現(xiàn)ARMv8基本參考模板。DesignWare 控制器 IP模型將與參考模板進(jìn)行整合。每個(gè)模型都可以根據(jù)軟件開(kāi)發(fā)者相關(guān)的設(shè)置進(jìn)行配置。經(jīng)過(guò)配置步驟后,軟件開(kāi)發(fā)者可以使用他們喜歡的軟件調(diào)試器。除了標(biāo)準(zhǔn)調(diào)試器功能,VDK還可以詳細(xì)查看軟件或硬件的活動(dòng)。軟件團(tuán)隊(duì)還可以將完成的軟件棧發(fā)送給硬件團(tuán)隊(duì),以便其進(jìn)行下一次性能迭代。這種并行的硬件設(shè)計(jì)和軟件開(kāi)發(fā)過(guò)程通常還被稱為"左移"。以IP為中心的SDK可以使設(shè)計(jì)人員,將軟件開(kāi)發(fā)任務(wù)分解為一系列獨(dú)立、相互隔離的任務(wù),這就不需要進(jìn)行大規(guī)模的組織變動(dòng)或大規(guī)模投資。唯一的投資就是添加Synopsys IP SDK,軟件團(tuán)隊(duì)無(wú)需進(jìn)行其他投資或者學(xué)習(xí)。

第4步:將IP整合到SOC中

從宏觀角度來(lái)看SOC設(shè)計(jì)問(wèn)題,半導(dǎo)體企業(yè)硬件方面的問(wèn)題主要包括:設(shè)計(jì)自有的差異化IP模塊、獲得高質(zhì)量第三方IP、按照SOC優(yōu)化法進(jìn)行配置、將所有模塊整合到時(shí)鐘、電壓供應(yīng)商的SOC基礎(chǔ)模塊中、芯片緩沖存儲(chǔ)器或寄存器、測(cè)試電路。SOC設(shè)計(jì)團(tuán)隊(duì)將確定半導(dǎo)體特定實(shí)施細(xì)節(jié)并制定關(guān)于如何整合IP的要求。IP具有泛型接口,如果不是在SOC基礎(chǔ)設(shè)施中加入額外粘合邏輯無(wú)法匹配。對(duì)于許多IP供應(yīng)商而言,這項(xiàng)工作是由SOC設(shè)計(jì)團(tuán)隊(duì)負(fù)責(zé)的繁瑣任務(wù)。

對(duì)IP供應(yīng)商期待更多(幫助)有利于設(shè)計(jì)人員解決這些問(wèn)題。首先,DesignWare IP原型套件提供了完整的參考設(shè)計(jì)。根據(jù)該設(shè)計(jì),半導(dǎo)體可以執(zhí)行相應(yīng)的粘合邏輯。他們甚至可以復(fù)制(相關(guān)方)提供的RTL源代碼并以此為起點(diǎn)作出更多工作。

對(duì)于小型SOC設(shè)計(jì)組織而言,這是一種使用IP提供者的知識(shí)、通過(guò)支持工程師或IP開(kāi)發(fā)者獲得相 關(guān)見(jiàn)解的高效方法。

對(duì)于項(xiàng)目復(fù)雜且截止時(shí)間較緊的大型組織而言,IP原型套件還不夠。他們需要更多的支持,并且需要大幅度降低內(nèi)部費(fèi)用:他們需要定制化的接口IP子系統(tǒng)。接口IP子系統(tǒng)使得設(shè)計(jì)人員可以充分利用IP提供者關(guān)于協(xié)議與標(biāo)準(zhǔn)的知識(shí)和見(jiàn)解,將這些知識(shí)和見(jiàn)解與他們自己的半導(dǎo)體知識(shí)和執(zhí)行問(wèn)題相結(jié)合,并提供綜合性解決方案。IP可交付成果與半導(dǎo)體需求的整合應(yīng)該通過(guò)節(jié)省成本、半定制方法完成。由于這個(gè)過(guò)程可以用于多個(gè)客戶,每個(gè)客戶可以享用來(lái)自其他項(xiàng)目的IP提供商經(jīng)驗(yàn),將IP重復(fù)利用范式用于子系統(tǒng)。IP提供者在上述整合中需要提供的要求包括:控制器與PHY的整合、多協(xié)議與常見(jiàn)PHY的整合、子系統(tǒng)(包括軟件棧)的完成。(例子:感應(yīng)器子系統(tǒng))

第5步:將驅(qū)動(dòng)和固件整合到SOC軟件棧中

最后,還需要進(jìn)行軟件開(kāi)發(fā)工作。即使對(duì)于驅(qū)動(dòng)而言,多數(shù)工作可以通過(guò)DesignWare IP原型套件或者IP虛擬開(kāi)發(fā)工 具包進(jìn)行分解和輔助,軟件開(kāi)發(fā)團(tuán)隊(duì)的終極目標(biāo)是完成整個(gè)軟件棧。軟件團(tuán)隊(duì)一般都從在上一個(gè)硅片上運(yùn)行的可用軟件棧開(kāi)始,并且嘗試使用先前的基板進(jìn)行一些開(kāi)發(fā)。但是由于半導(dǎo)體的重大變化,他們無(wú)法走的很遠(yuǎn),因此,如果他們希望撼動(dòng)整個(gè)設(shè)計(jì)圈,他們需要一個(gè)涉及SOC所有相關(guān)部件的硅實(shí)現(xiàn)前目標(biāo)。

這項(xiàng)工作所需的投資和努力遠(yuǎn)遠(yuǎn)大于簡(jiǎn)單的IP SDK,但是對(duì)于軟件開(kāi)發(fā)團(tuán)隊(duì)是一個(gè)好消息的是:新思科技的IP SDKs實(shí)際上是一個(gè)可以獲得整個(gè)SOC目標(biāo)的縮小版。小型團(tuán)隊(duì)將會(huì)欣喜的發(fā)現(xiàn)DesignWare IP原型套件可以作為墊腳石,幫助他們獲得更多的SOC部件。4M的門(mén)容量對(duì)于低于500K的控制器尺寸可以充分滿足需要,為相同的原型系統(tǒng)添加更多部件所需的空間也預(yù)留充足。

隨著規(guī)模不斷擴(kuò)大,原型團(tuán)隊(duì)可以首先使用HAPS-70原型系統(tǒng)并與像衛(wèi)星系統(tǒng)一樣擴(kuò)展連接DesignWare IP原型套件,這樣可以保留已經(jīng)完成且已驗(yàn)證的部分、可以快速切換到SOC其他未驗(yàn)證部分進(jìn)行工作(圖7)。

對(duì)于使用虛擬原型方法的團(tuán)隊(duì)而言,DesignWare IP VDK內(nèi)的模型是Virtualizer?虛擬原型工具中可用模型的完整打包版。這類團(tuán)隊(duì)可以使用Virtualizer?中相同的參考模型和配置,與事務(wù)級(jí)模型(TLM)庫(kù)(涵蓋最常用的商業(yè)IP)中的其他特定SOC模型一起進(jìn)行擴(kuò)展,并使用Virtualizer事務(wù)級(jí)模型(TLM)創(chuàng)建工具為獨(dú)特的內(nèi)部IP創(chuàng)建模型。

IP Accelerated(IP加速)

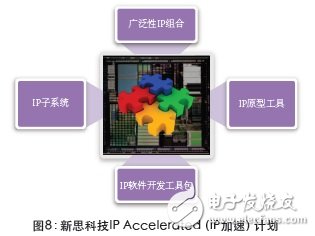

IP Accelerated(IP加速)是新思科技(作為接口IP的頭號(hào)提供商)為了推進(jìn)IP供應(yīng)商范例啟動(dòng)的多年計(jì)劃。新思科技IP Accelerated(IP加速)計(jì)劃(圖8)促進(jìn)了新思科技已經(jīng)建立的廣泛的,經(jīng)過(guò)硅驗(yàn)證DesignWare IP組合,該組合包括新型DesignWare IP原型套件、DesignWare IP虛擬開(kāi)發(fā)工具包、IP子系統(tǒng),這可以加快確定原型、軟件開(kāi)發(fā),并加快將IP整合到SOC體中。

對(duì)于硬件工程師而言,IP原型套件可以提供經(jīng)過(guò)驗(yàn)證的IP配置,并且該配置可以輕松修改以便為目標(biāo)性應(yīng)用進(jìn)行優(yōu)化設(shè)計(jì)。軟件開(kāi)發(fā)者可以使用IP虛擬開(kāi)發(fā)工具包或者IP原型套件用于軟件的前期開(kāi)發(fā)、調(diào)試、測(cè)試。

概述與展望

半導(dǎo)體行業(yè)正在根據(jù)市場(chǎng)需求的變化進(jìn)行一次自然進(jìn)化。雖然客戶向半導(dǎo)體行業(yè)提出了很多新的要求,IP提供者不得不滿足這些不斷增加的要求。IP Accelerated(IP加速)計(jì)劃有利于應(yīng)對(duì)這些挑戰(zhàn)。我們需要盡量在滿足IP用戶最大程度上的自我發(fā)展與向關(guān)注核心競(jìng)爭(zhēng)力的組織提供專門(mén)定制化服務(wù)的行為之間尋求平衡。

參考

[1]系統(tǒng)IC業(yè)務(wù)成功的要素以及對(duì)商業(yè)模式產(chǎn)生的影響,IBS2012年第4季度報(bào)告

[2]2013年新思科技全球用戶調(diào)查

[3]全球系統(tǒng)IC行業(yè)服務(wù)報(bào)告 - 將半導(dǎo)體行業(yè)內(nèi)的軟件貨幣化的方法,IBS第23卷第4號(hào),2014年4月

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論