用循環語句設計一個7人投票表決器,速求

2013-04-23 18:01:49

僅供參考,有哪里不對的話還望各位網友多多指教,大家共同探討。

2019-06-21 15:24:02

8人表決器電路,,源文件

2015-04-12 09:43:57

2.還有一種反熔絲(Anti-fuse)技術的FPGA,如Actel,Quicklogic的部分產品就采用這種工藝。但這種的PLD是不能重復擦寫,需要使用專用編程器,所以開發過程比較麻煩,費用也比較昂高

2012-02-27 10:42:53

PLD現在已經從采用最先進的標準單元技術制造的固定邏輯器件手中奪得部分市場份額。而消費電子則是PLD正在快速增長的應用領域。 PLD行業最近出現了很多新變化。以往,PLD更多是用在一些特殊產品中,例如低成本原型,或者像路由器這樣的小批量產品。而今天,PLD則更多涉足消費電子領域。

2019-07-29 08:07:20

采用最先進的標準單元技術制造的固定邏輯器件手中奪得部分市場份額。而消費電子則是PLD正在快速增長的應用領域。 PLD行業最近出現了很多新變化。以往,PLD更多是用在一些特殊產品中,例如低成本原型,或者像路由器這樣的小批量產品。而今天,PLD則更多涉足消費電子領域。

2019-07-17 07:19:16

采用最先進的標準單元技術制造的固定邏輯器件手中奪得部分市場份額。而消費電子則是PLD正在快速增長的應用領域。 PLD行業最近出現了很多新變化。以往,PLD更多是用在一些特殊產品中,例如低成本原型,或者像路由器這樣的小批量產品。而今天,PLD則更多涉足消費電子領域。

2019-07-22 06:51:56

,通過三態門控制數據直接輸出或反饋到輸入端。PLD有多種結構形式和制造工藝,不同廠商生產的可編程邏輯器件又有不同的型號和名稱,下面簡單介紹低密度和高密度可編程邏輯器件的基本結構和特點。(1)PROM。即可編程只讀存儲器

2019-03-06 10:19:07

得不夠用了。如果我們采用把外部數據地址翻譯成控制信號的方法,就會有用不完的資源,而實現這個翻譯功能的,最簡單有效的莫過于PLD器件。例如:1、LG12864液晶模塊的控制信號就有E、RW、RS、CS1、CS2五個

2012-11-19 20:41:23

和VHDL的使用比率大概是80%和20%,在中國,大多數電子行業企業都采用Verilog。而模塊化的設計讓VerilogHDL語言具有思路清晰、邏輯關系明確、可讀性強等特點,模塊化的設計在

2018-05-04 12:06:12

verilogHDL中的{}用法,求詳解。

2015-03-22 23:48:03

三人表決器的VHDL設計實現求代碼

2018-11-10 13:50:50

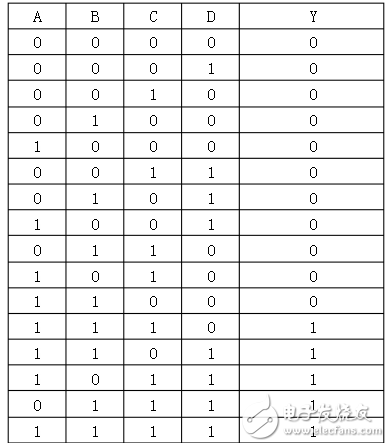

設計一個七人表決電路:表決結果用不同顏色的LED表示;表決輸入采用自恢復按鍵,即點動后能夠自動復位的那種,盡量采用與或非門完成設計,結果必須最簡;

2009-05-17 10:10:23

求labview速成方法《《《《急急急

2012-09-11 21:54:12

基于PLD和嵌入式存儲器實現W-CDMA調制解調器的設計

2020-12-28 06:04:37

)、USB 2.0、DVI、HDMI和各種各樣的無線標準。本文將介紹如何應用可編程邏輯器件(PLD)將不同的高速視頻內容連接到視頻播放器。 視頻輸入 USB 2.0是目前連接電腦和娛樂信息設備的主流

2019-05-14 07:00:12

:數字電路是FPGA的敲門磚、因為數字電路主要的內容就是組合和時序,而組合和時序就是FPGA設計的核心。HELLO FPGA項目實戰篇:該篇列舉三人表決器、數字時鐘、多功能點歌系統、數字示波器這四個實際的工程項目,手把手帶領大家分析工程、分解工程、到最終實現工程。

2020-05-11 14:31:53

搶答器在各類競賽中的必備設備,有單路輸入的,也有組輸入方式,本設計以FPGA為基礎設計了有三組輸入(每組三人),具有搶答計時控制,能夠對各搶答小組成績進行相應加減操作的通用型搶答器;現行的搶答器中

2019-09-24 08:24:20

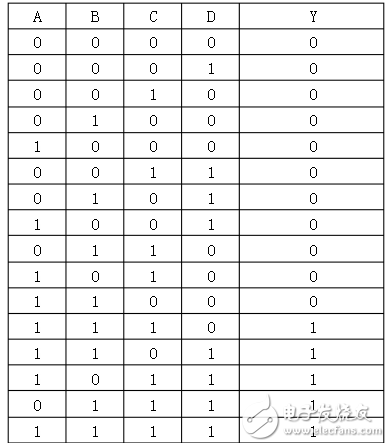

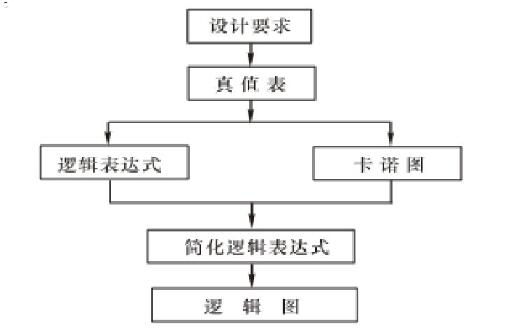

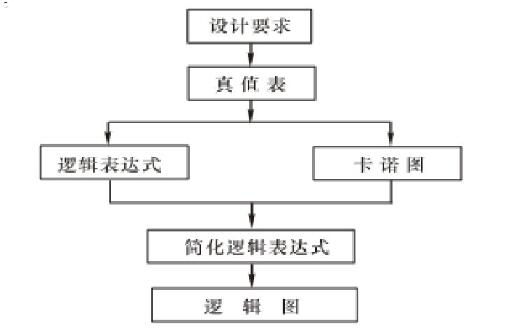

時序電路)。 在組合邏輯電路中,任何時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。這就是組合邏輯電路在邏輯功能上的共同特點。在上一節中,設計的三人表決器就是組合邏輯電路,輸出與輸入一一對應,和其他

2023-02-21 15:35:38

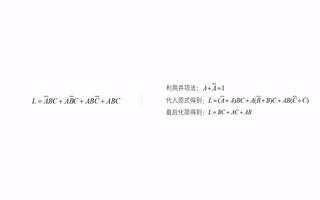

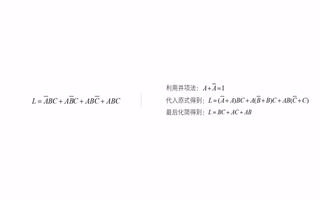

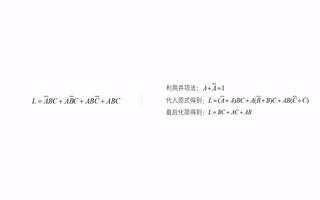

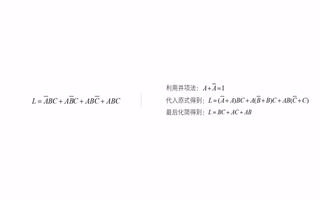

項。兩個相鄰最小項可以合并為一個與項并消去一個變量。 如圖: 圖10 :三輸入變量的卡諾圖 圖11 :三人表決器的卡諾圖我們可以用圓圈圈出相鄰的值為‘1’的最小項,注意只能是矩陣畫(2,4

2023-02-20 17:24:56

現在用51單片機和nrf905做一個表決器。關于nrf905有一些問題,想讓大家幫幫忙!!!nrf905上的spi接口只需要設置RF配置寄存器,是嗎?如果是如何確定那個是主哪個是從, 難道主從是看程序中所寫的發送和接收程序嗎?

2012-09-15 17:16:47

`項目實戰篇以例舉三人表決器、數字時鐘、多終端點歌系統、數字示波器這四個實際的工程項目,手把手帶領大家從分析工程、分解工程到最終實現工程。`

2021-04-06 14:20:59

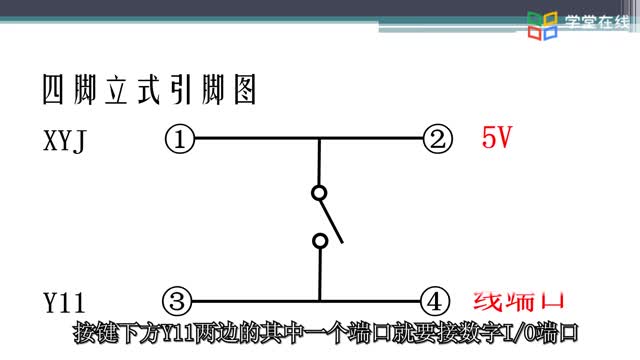

有了對LED、KEY、數碼管的了解后,接下來就是對這三者一個綜合應用了,那就是經典的三人表決器。結合開發板,三個按鍵按下,則其對應的LED將會點亮,數碼管同時顯示總的投票數 無需廢話。看程序

2016-09-21 22:02:31

)兩類功能,瞬時邏輯主要是指與、或、非及其混合運算,輸出結果對輸入條件能即時響應;延時邏輯一般由時鐘信號驅動,主要實現寄存器、計數器以及與十序有關的邏輯功能。 最簡單的PLD器件一般有8個專用輸入端和8

2012-10-30 23:39:54

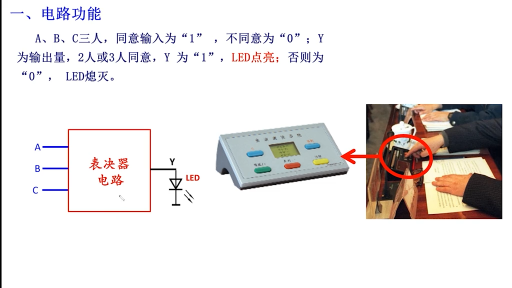

(二) 由邏輯命題編程如果用撥動開關左1、左2、左3代表邏輯輸入A、B、C,發光管左1、左2、左3位指示其狀態,用數碼管1和0指示輸出狀態試編程序實現下述邏輯關系:M10.模擬少數服從多數表決器(三

2013-07-14 16:01:39

4路搶答電路。具體功能如下:1用D觸發器和門電路設計一個四路搶答電路。2每個參賽者控制一個按鈕,用按動按鈕發出搶答信號。3裁判有一個總按鈕開關,用于將搶答器清零復位。4競賽開始后,先按動按鈕者將對應的一個發光二極管點亮,此后其他三人再按動按鈕對電路不起作用。僅供參考,不喜勿噴。

2015-05-26 18:20:37

可綜合的VerilogHDL設計實例在前面七章里我們已經學習了VerilogHDL的基本語法、簡單組合邏輯和簡單時序邏輯模塊的編寫、Top-Down設計方法、還學習了可綜合風格的有限狀態機

2009-11-23 16:01:33

的消費類視頻接口包括ieee 1394(火線)、u*** 2.0、dvi、hdmi和各種各樣的無線標準。本文將介紹如何應用可編程邏輯器件(pld)將不同的高速視頻內容連接到視頻播放器。

視頻輸入

u

2018-12-28 07:00:06

基于AT89C51的智能搶答與表決計時器的設計與實現

2012-08-06 12:45:56

74LS283芯片,對輸入電平進行全加;三是7485N芯片,對其進行比較;四是譯碼顯示器對邏輯運算后的結果進行輸出顯示,完成五人表決器的功能。

2018-10-19 16:04:45

請問如何使用PLD去設計三相正弦波電壓發生器?

2021-04-29 07:01:08

采用最先進的標準單元技術制造的固定邏輯器件手中奪得部分市場份額。而消費電子則是PLD正在快速增長的應用領域。

2019-09-24 06:58:39

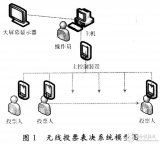

以微型處理器為核心,外圍配以存儲器,鍵盤及led顯示器,設計出一種實用的無線電子表決器

2019-03-13 15:02:16

現在我在做一個無線表決器,其他都成功了,但是就是在報到時無法排除沒有按下報到鍵和沒有上電的表決器,我個人認為是表決器返回值時出錯了,但我有找不到問題,希望各位幫幫忙,謝了!!! 下面是我集中器發送

2013-03-14 16:53:57

怎么畫線路圖和原理圖

2018-06-19 12:07:25

本帖最后由 eehome 于 2013-1-5 09:58 編輯

用AT89C51實現三人表決器

2012-08-14 19:39:24

本書光盤提供了第15章到第23章的實例完整的Verilog HDL程序代碼。為了方便查閱,每章實例都歸檔在該章相應的文件夾下。所有的實例文件名為:“*.v”,可以用任何文本編輯器打開并進行編輯(例如

2012-02-07 10:25:05

用BD—Ⅳ型,拼一個三人表決器電路接通開關,A、B、C三點:雙向燈綠燈紅燈三點都懸空(不表決)藍滅滅無論哪二點接正,另一點接正、接負、懸空滅亮滅無論哪二點接負,另一點接正、接負、懸空滅滅亮不使

2019-09-29 20:57:34

這兩個警告怎么解決,一下是源程序,我做的是三人表決,程序通過,但是仿真的波形不對啊Warning: No exact pin location assignment(s) for 4 pins

2016-09-28 18:07:55

PLD設計技巧—采用同步電路設計AsynchronousvsSynchronous Circuit Design

Mainly useCombinationalLogic to do

2008-09-11 09:12:46 24

24 PC機與單片機通信實例:表決器單片機要同時處理很多部分的功能,如:按鍵處理、LED處理、通信處理等。而單片機程序是串行執行的。如何讓眾多任務同時進行或者看起來同時

2009-06-28 00:02:05 70

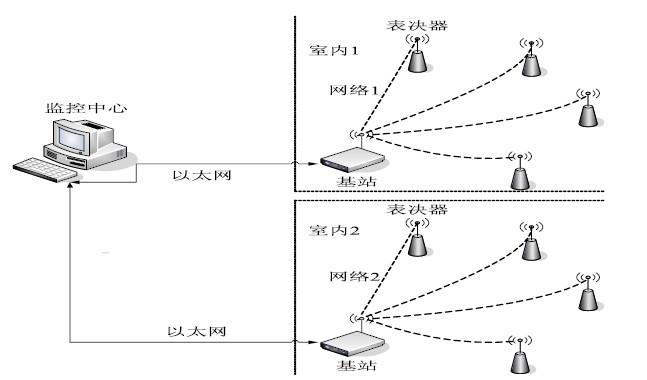

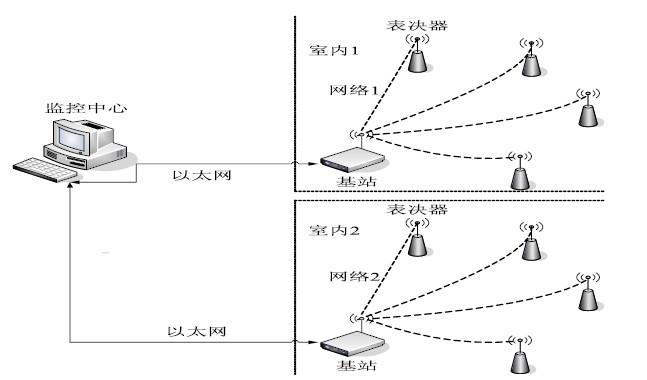

70 介紹了一種基于MSP430F123 和nRF905 的無線表決系統的軟硬件設計與實現。系統通過主控器、表決器和PC 機實現對表決信息的采集、處理和顯示。本系統具有低功耗、功能強、可靠性

2009-08-11 08:22:51 51

51 介紹了PCM采編器的工作原理,并且詳細解釋了采用VerilogHDL語言用EDA的方法設計及實現PCM采編器的仿真及下栽過程,說明了PCM采編器在通信及廣播領域的廣泛用途。

2012-04-01 15:07:42 74

74 我們根據三人表決器的直值表,可以通過 卡諾圖 化簡可以得到: L2=SW1SW2 SW1SW3 SW2SW3 L1=_L2 那么我們可以在MAX plusII中用原理圖實現上面的三人表決器 下面僅把和 VHDL 不同的詳細寫下,相

2012-05-18 15:46:43 8330

8330

--三人表決器(三種不同的描述方式) vhdl -- Three-input Majority Voter -- The entity declaration is followed

2012-05-18 16:04:22 20986

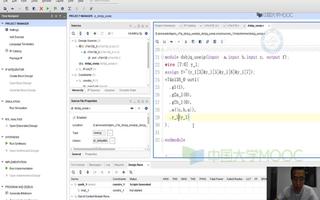

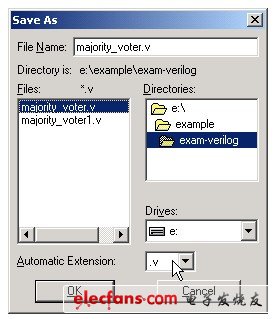

20986 今天我們將帶領大家完成你的第一個PLD設計,即使你從沒有接觸過PLD,也可以讓你可以在十分種之內初步學會PLD設計! 不信? 呵呵 我們慢慢往下看。 實驗目的 我們分別采用VHDL、Verilog

2012-05-18 16:29:52 1124

1124 打開MAX plusII,在開始菜單內選擇MAX PLUS II 項,開始運行MAX PLUS II(如下圖) 你最好把圖標放到桌面上,以后直接雙擊MAX PLUS II圖標就可以運行軟件了 在MAX PLUSII上點右鍵,選擇發送到-桌面快

2012-05-18 16:37:17 13917

13917

1 引言 投票表決器在選舉,會議,教學,娛樂節目中得到大量的使用。現行的無線表決系統采用單一的無線網絡,使無線終端設備與上位機進行通信。由于無線網絡存在傳輸距離有限,

2012-07-24 16:45:27 1671

1671

VerilogHDL基礎資料,介紹VerilogHDL的基礎知識和實際應用

非常實用的教程

2015-12-07 14:14:31 0

0 VerilogHDL數字系統設計及其應用

有需要的朋友下來看看

2015-12-29 15:45:20 11

11 復雜數字電路與系統的VerilogHDL設計技術

2015-12-29 17:21:18 1

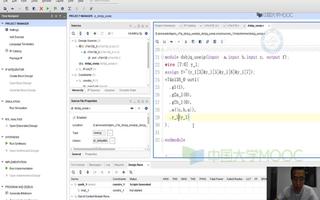

1 掌握在 Quartus Ⅱ開發環境下,運用硬件描述語言輸入法對“三人表決器”進行設計輸入、編譯、調試和仿真的方法。

2016-01-15 15:27:33 0

0 HL配套C實驗例程100例之表決器,配合開發板學習效果更好。

2016-04-11 16:09:41 14

14 以前寫論文收集的一些資料,學習單片機、C語言的好資料!!!!

2016-07-08 13:58:47 4

4 基礎的電子類資料,設計和開發必備資料,快來下載學習吧。

2016-09-28 11:57:32 12

12 verilogHDL精粹,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 17:12:34 4

4 基于PCM采編器的VerilogHDL語言設計

2017-10-31 09:30:46 39

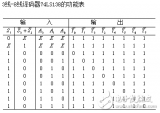

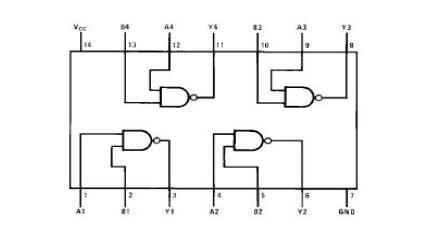

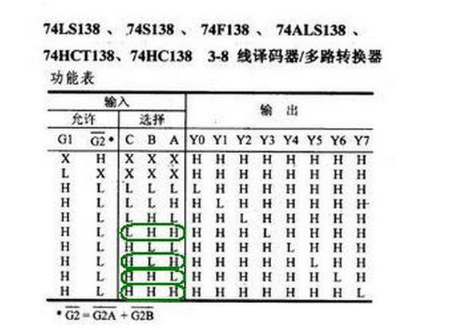

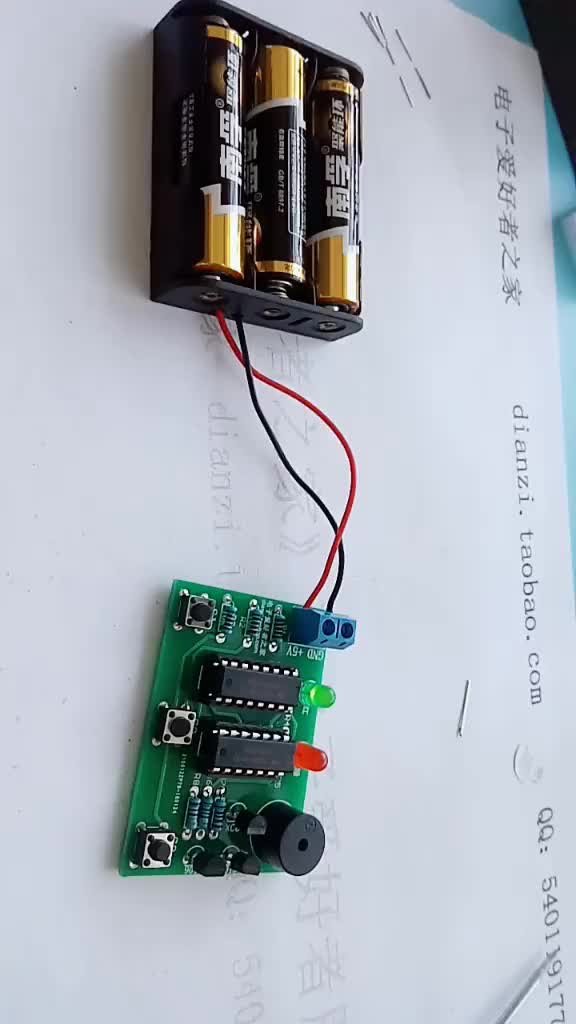

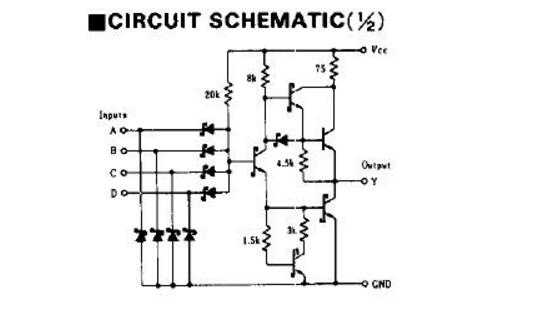

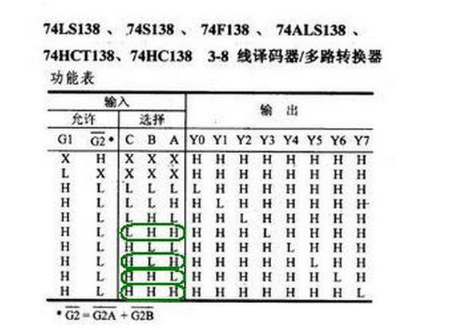

39 三人表決器主要由一個3-8位譯碼器(74LS138)和2個4輸入與非門(74LS20)組成。通過三個按鈕接受用戶輸入。按鈕按下表示同意,不按下表是否決,當沒有人按下按鈕時,或只有一個人按下按鈕

2017-10-31 15:13:25 92965

92965

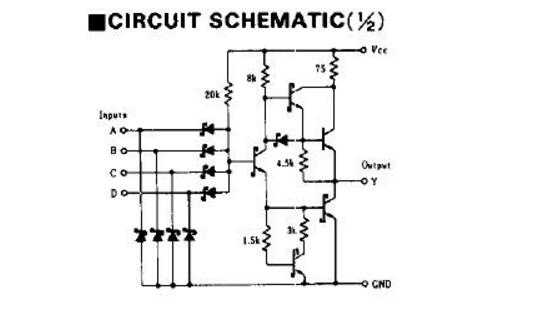

本文為大家帶來五種三人表決器電路設計方案,包括兩款仿真電路及程序分析,三款邏輯電路設計的原理詳解。

2018-01-17 18:49:21 298033

298033

本文為大家分享四款四人表決器電路設計的原理及方案詳細。

2018-01-17 19:13:09 142800

142800

本文為大家帶來五款五人表決器電路設計方案。

2018-01-18 09:18:07 98683

98683

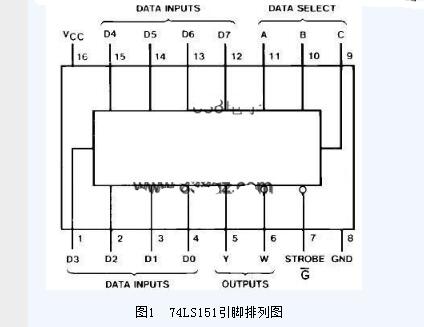

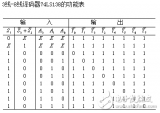

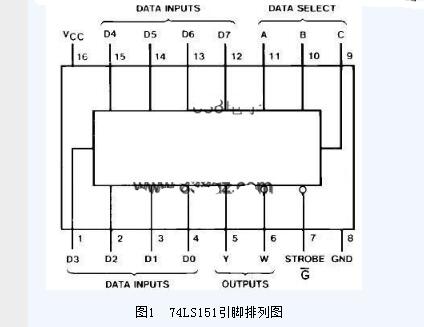

本文介紹了4種方式實現三人表決電路。其中包括用74LS00,74LS20實現三人表決電路、用譯碼器138和與非門74LS20設計實現三人表決電路、用8選1數據選擇器74LS151實現三人表決電路以及用4選1數據選擇器74LS153實現三人表決電路方法。

2018-01-26 17:26:20 335165

335165

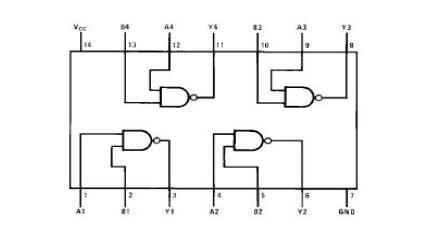

本文開始介紹了74LS00管腳排列圖與74ls00的功能表,其次介紹了74ls00應用電路與74ls00的極限值,最后介紹了74ls00制作三人表決器邏輯電路的設計步驟與調試。

2018-02-08 15:42:56 243528

243528

本文開始介紹了74LS20功能表與74LS20引腳圖,其次介紹了74LS20真值表,最后詳細介紹了74ls20實現的四人表決器電路并對工作原理、電路仿真及調試進行了相應的介紹。

2018-02-08 16:18:08 90713

90713

74ls151是常用的8選1數據選擇器。本文主要介紹了74ls151引腳圖、74ls151邏輯圖及74ls151真值表,詳細的闡述了74ls151實現三人表決器電路。

2018-02-08 16:59:36 177218

177218

本文主要介紹了五款74ls138的應用電路圖。其中包括了74ls138全加器電路、74ls138搶答器電路、74ls138實現邏輯函數、74ls138全減器電路以及與74LS20組合的三人表決器電路。

2018-05-04 10:31:55 95858

95858

”,綠燈不亮;當表決器的五個輸入變量中有3個以上(含3個)為“1”時,則表決器輸出為“1”,此時綠燈就亮了。

2018-05-07 11:38:47 108521

108521

在三人表決器的設計中,如果數字系統簡單,可以采用門電路;如果數字系統復雜,則可以采用譯碼器、數據選擇器和加法器比較好。

2018-08-07 09:31:14 161411

161411

投票表決器在選舉,會議,教學,娛樂節目中得到大量的使用。現行的無線表決系統采用單一的無線網絡,使無線終端設備與上位機進行通信。由于無線網絡存在傳輸距離有限,對障礙物穿透性較差等問題,無法實現遠程監控

2018-12-26 09:10:00 4425

4425

該設計實現了基于MSP430F135和CCllOO的無線表決系統的主控制裝置和表決器的軟硬件,并利用Microsoft Visual Studio 2005實現了系統PC機軟件的設計,同時用非接觸式射頻卡儲存個人信息,省時省力,在平時民主測評中以及其他相應場合的應用前景非常廣泛。

2018-09-13 09:32:00 5404

5404

多數表決器常見于信號處理。例如,在自動控制中,對三個針對同一事物的信號使用多數表決器進行運算,并按照其中兩個一致的結果執行。這樣既可以提高信號的可靠性(信號不止一個),又避免信號源錯誤(出錯的信號在表決中被排除)造成不必要的損失。

2019-12-04 07:02:00 2675

2675

表決器,是投票系統中的客戶端,是一種代表投票或舉手表決的表決裝置。表決時,與會的有關人員只要按動各自表決器上“贊成”、“反對”、“棄權”的某一按鈕,熒光屏上即顯示出表決結果。目前,表決器可分為有線

2019-09-23 07:09:00 2043

2043

表決器,是投票系統中的客戶端,是一種代表投票或舉手表決的表決裝置。表決時,與會的有關人員只要按動各自表決器上“贊成”、“反對”、“棄權”的某一按鈕,熒光屏上即顯示出表決結果。

2019-09-23 07:05:00 2725

2725

我們例舉三人表決器、數字時鐘、多終端點歌系統、數字示波器這四個實際的工程項目,手把手帶領大家從分析工程、分解工程、到最終實現工程。通過逐個解決工程中的實際問題,來學習原汁原味的FPGA設計。本篇一改

2019-12-06 07:05:00 6384

6384

本文檔的主要內容詳細介紹的是組合邏輯電路三人表決器的設計資料詳細說明。

2019-12-03 08:00:00 12

12 本文檔的主要內容詳細介紹的是使用單片機實現七人表決器的程序和仿真資料免費下載。

2020-06-22 08:00:00 30

30 本文檔的主要內容詳細介紹的是8人表決器的電路圖免費下載。

2020-06-28 16:46:00 49

49 protel dxp 三人表決器

2022-06-14 15:00:26 0

0 利用multisim仿真,三人搶答。

2022-06-16 14:45:59 15

15 基于51單片機的表決器例程源代碼例程源代碼

2023-05-12 15:55:13 1

1 基于51單片機的表決器例程源代碼例程源代碼

2023-05-18 09:54:43 0

0

電子發燒友App

電子發燒友App

評論