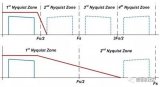

經常涉及對寬帶模擬信號進行數據采集和存儲,以便計算機進一步進行數據處理。為了對高速模擬信號進行不失真采集,根據奈奎斯特定理, 采樣頻率必須為信號頻率的2 倍以上,但在電阻抗多頻及參數成像技術中正

2023-09-15 09:45:01 1054

1054

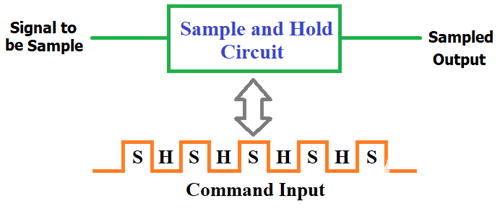

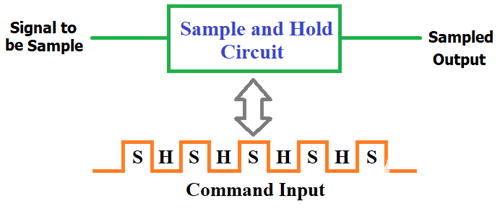

本文主要介紹了采樣保持電路圖大全(五款采樣保持電路設計原理圖詳解),采樣保持電路(采樣/保持器)又稱為采樣保持放大器。當對模擬信號進行A/D轉換時,需要一定的轉換時間,在這個轉換時間內,模擬信號要保持基本不變,這樣才能保證轉換精度。采樣保持電路即為實現這種功能的電路。

2018-02-23 09:59:44 95716

95716

采樣保持電路從模擬輸入信號中獲取樣本并保持特定時間段,然后輸出輸入信號的采樣部分。該電路僅對幾微秒的輸入信號進行采樣。

2022-11-08 17:29:18 6704

6704

作者:Wasim Shaikh 和 Srikanth Nittala 本文介紹連續時間Σ-Δ ADC,通過簡化信號鏈來有效解決采樣問題。采用這種方法無需使用抗混疊濾波器和緩沖器,并可解決與額外組件

2020-12-30 17:06:17 3456

3456

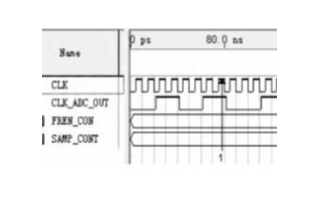

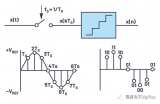

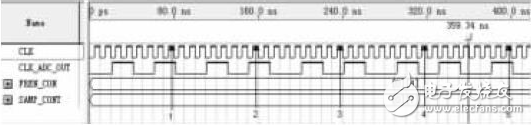

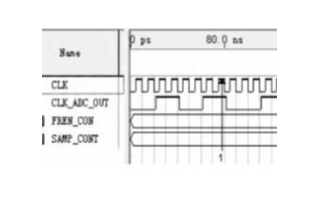

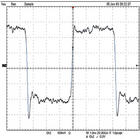

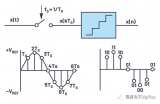

,分頻后的時鐘波形在時鐘的上升沿對信號進行采樣,那么就會得到如圖1(a)中所表示的等效時間采樣。等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計圖1 等效時間采樣示意圖2 、基于FPGA的等效

2020-10-21 16:43:20

等效時間采樣中應用的ADC,應該注意哪些問題呢?一般采樣速率有何限制?對于ADC的模擬輸入帶寬呢?

2023-12-25 06:42:31

AD值存到SPI FLASH中。 我發現采樣頻率是4K時還是比較準的。當采到10K時,由于SPI FLASH的寫入的函數比較浪費時間,導致整個采樣的時間不對。 大家有沒有什么好辦法來存數啊?我要存100K左右的數據。多謝各位啦~

2020-08-20 08:00:14

電路中經常用到AD采樣,但對于AD采樣的原理有沒有想進一步了解下,以顯示下自己不止于小白呢,那么請往下看。----AD采樣的分類----包括并聯比較型(也叫Flash型)、SAR型(逐次逼近型

2022-01-26 06:49:44

STM32——ADC采樣時間、采樣周期、采樣頻率計算方法ADC轉換:單片機將采集到的模擬量信號,通過ADC控制器轉換成數字量。采樣周期:單片機讀取數字量必須等轉換完成后,完成一個通道ADC讀取(采樣

2021-12-10 06:16:05

ADC_RegularChannelConfig(ADC1, ADC_Channel_10, 1, ADC_SampleTime_55Cycles5); //設置指定 ADC 的規則組通道,設置它們的轉化順序和采樣時間 ADC_Cmd

2020-08-28 08:00:16

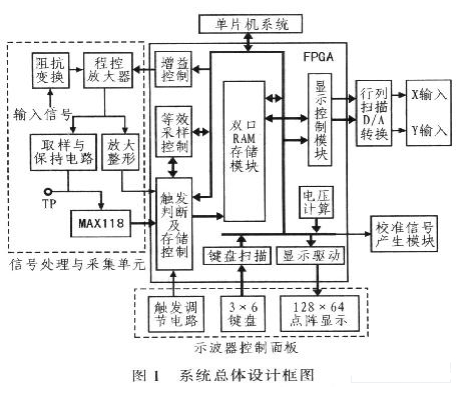

項目名稱:等效隨機采樣的數字存儲式示波器試用計劃:利用fpga驅動高速adc模塊,構成數字存儲式示波器

2017-06-20 11:19:18

高速、超寬帶信號采集技術在雷達、天文和氣象等領域應用廣泛。高采樣率需要高速的模/數轉換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現的數據采集對FPGA的性能和PCB布局布線技術提出了嚴峻的挑戰。

2019-11-08 06:34:52

你好,這是原理圖

我使用FPGA對AD7606進行采樣,每次采樣的值總是再下一次采樣時出現,請問這是什么問題?

2023-12-14 08:06:06

,采取等位移多點取樣法,完全克服了以上方法的缺點,具有很高的識幣能力。同時,還能對硬幣的直徑進行檢測。由于采樣時間和采樣間隔都很短,對系統的高速性和可靠性有較高的要求,用傳統的單片機難以滿足要求,在該設計中,通過FPGA完成對數據的高速采樣和處理。

2018-11-09 11:00:49

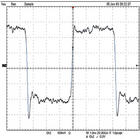

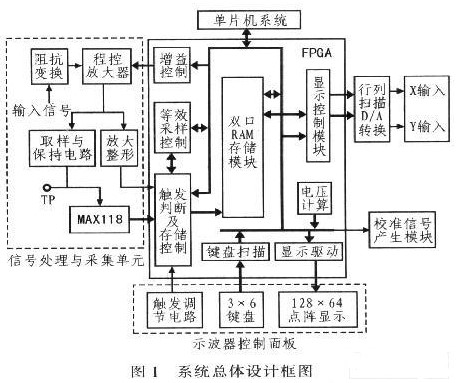

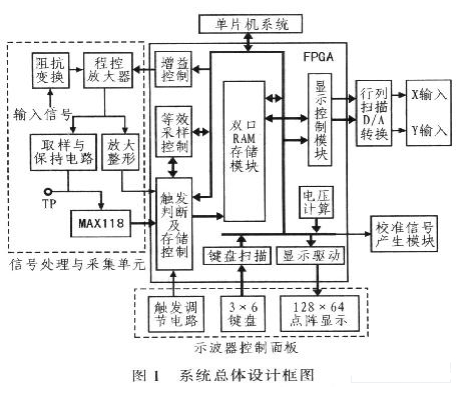

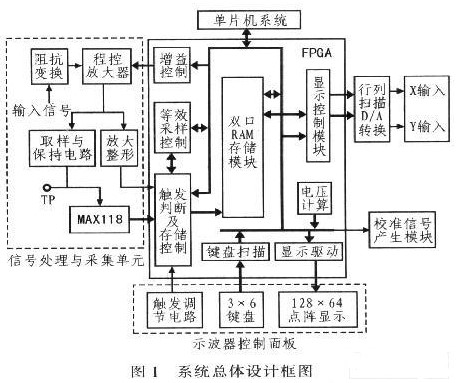

本文介紹一種基于等效和實時采樣的數字示波器設計。

2021-05-17 06:00:57

請教各路大神,在ucos里若是AD采樣時間需要很準確,例如50us采樣一個數據,有什么解決方法呢? 單分配一個AD采樣任務貌似不太合理。

2019-08-09 04:15:59

Hello,我利用2812的AD對一個200Hz的正弦信號進行采樣,要求每個周期采20個點,然后在Ad的中斷服務子程序中進行處理,雖然經過計算可以設置AD的采樣頻率,但是因為中斷服務子程序的執行時間不好控制,我想問一下,如何能夠保證我的Ad采樣頻率?謝謝!

2018-08-19 07:40:23

等效時間采樣中應用的ADC,應該注意哪些問題呢?一般采樣速率有何限制?對于ADC的模擬輸入帶寬呢?

2018-11-26 09:46:09

實時技術到底有什么意義?到底選擇實時采樣還是等效時間采樣?

2021-05-10 06:57:27

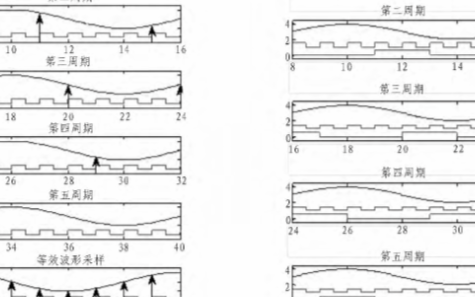

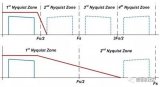

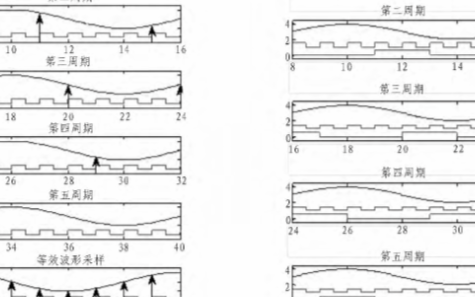

在數字示波器技術中!常用的采樣方法有兩種" 實時采樣和等效采樣# 實時采樣通常是等時間間隔的!它的最高采樣頻率是奈奎斯特極限頻率# 等效采樣$3456789:;<$8=>96;?% 是指

2010-07-08 16:30:04 42

42 本文在介紹了等效采樣的原理和方法的基礎上提出了一種基于EDA技術的實現方案。借助高速發展的EDA技術,可以方便地產生采樣信號,大大簡化采樣觸發電路,解決了傳統等效采樣

2010-08-03 10:48:54 19

19 針對四通道時間交叉采樣對時鐘的嚴格要求,提出了使用時鐘分配器AD9516給四個交叉采樣的模數轉換器AD9445提供四路在相位上嚴格相差90°的110 MHz的采樣時鐘。在介紹AD9516特

2010-12-16 16:08:58 0

0 摘要:介紹了基于單片機系統的精密時鐘發生電路對高頻信號(1MHz~80MHz)進行等效采樣的方法,設計并實現一個模擬帶寬為1Hz~80MHz的簡易數字示波器。

2006-03-24 13:13:02 1373

1373

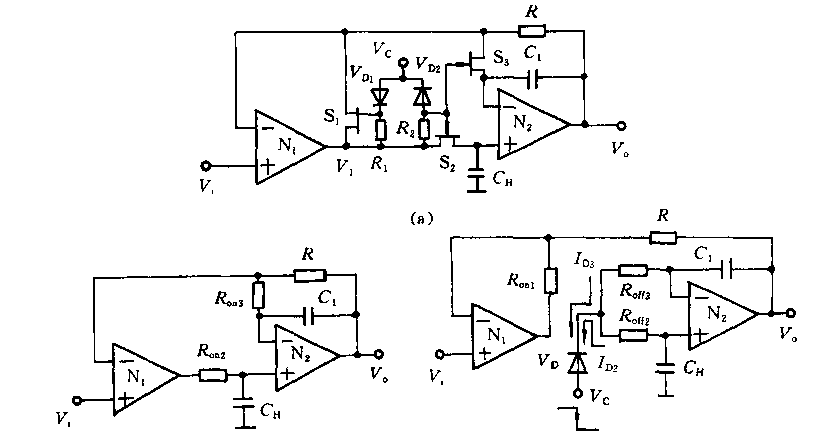

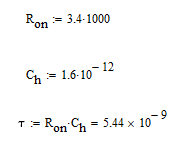

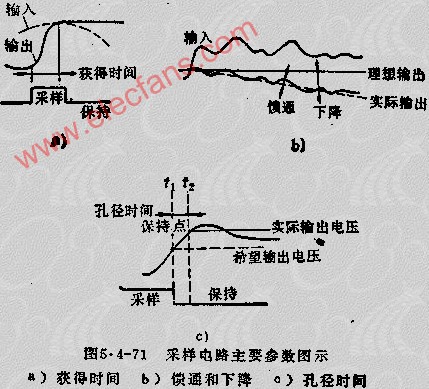

采樣保持放大器

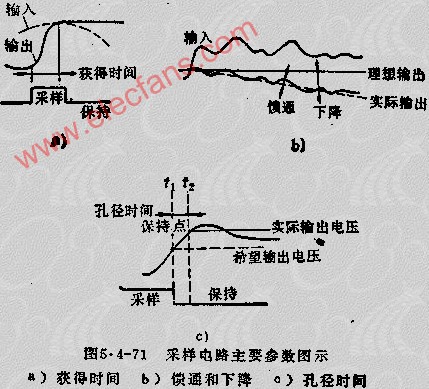

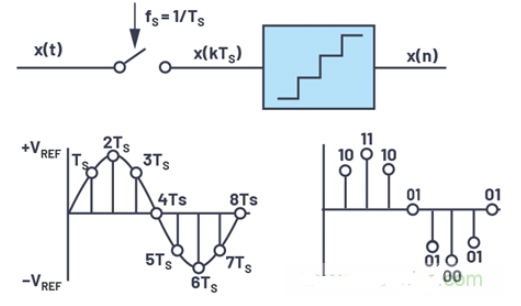

采樣保持電路(采樣/保持器)又稱為采樣保持放大器。當對模擬信號進行A/D轉換時,需要一定的轉換時間,在這個轉換時間內,模擬信號要保持基本不變,這

2009-03-11 18:29:56 3785

3785

采樣保持電路(S/H)原理

A/D轉換需要一定時間,在轉換過程中,如果送給ADC的模擬量發生變化,則不能保證精度。為此,在ADC前加入采樣保持電路,如圖8-30所示。采樣保持電路有兩種

2009-04-12 12:01:35 22785

22785

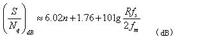

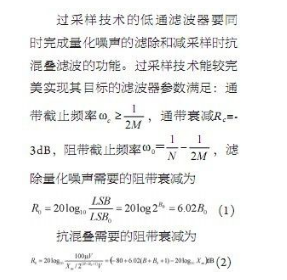

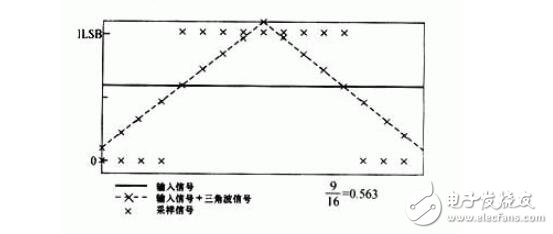

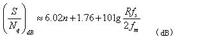

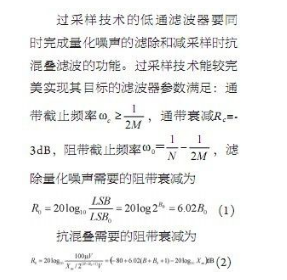

過采樣技術原理介紹

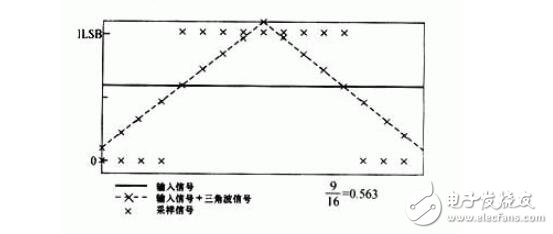

假定環境條件: 10位ADC最小分辨電壓1LSB 為 1mv 假定沒有噪聲引入的時候, ADC采樣上的電壓真

2009-05-04 19:23:53 13146

13146 什么是過采樣

過采樣是使用遠大于奈奎斯特采樣頻率的頻率對輸入信號進行采樣。設數字音頻系統原來的采樣頻率為fs,通常為44.1kHz或48kHz

2009-05-04 19:27:55 4259

4259

什么是采樣頻率?什么叫采樣頻率

采樣頻率:即取樣頻率,指每秒鐘取得聲音樣本的次數.它的采樣頻率越高,聲音的

2009-05-04 19:42:42 20344

20344

基于DSP的過采樣技術

在使用DSP進行數字信號處理時,應用過采樣技術可以增加其內置模數轉換器的分辨率。討論了應用過采樣技術的原理、如何使

2009-05-04 21:22:37 923

923

DSP的過采樣技術原理

在使用DSP進行數字信號處理時,應用過采樣技術可以增加其內置模數轉換器的分辨率。討論了應用過采樣技術的原理、如何

2009-05-04 22:40:17 2745

2745

在使用DSP進行數字信號處理時,應用過采樣技術可以增加其內置模數轉換器的分辨率。討論了應用過采樣技術的原理、如何使用TMS320LF2407來實現過采樣,以及在軟件上的實現方法

2009-05-09 12:19:05 681

681

圖像子采樣

對彩色電視圖像進行采樣時,可以采用兩種采樣方法。一種是使用相同

2009-07-31 14:22:59 4908

4908 什么是采樣的頻率/采樣的位數?

采樣頻率是指錄音設備在一秒鐘內對聲音信號的采樣次數,采樣頻率越高聲音的還原就越真實越自

2010-02-05 09:54:04 2088

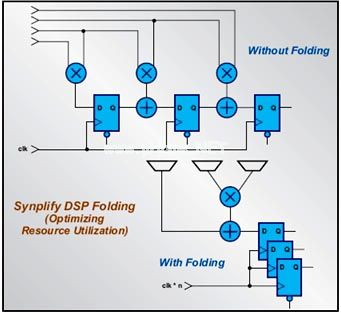

2088 用FPGA實現音頻采樣率的轉換

如今,即使低成本FPGA也能提供遠遠大于DSP的計算能力。目前的FPGA包含專用乘法器甚至DSP乘法/累加(MAC)模塊,能以550MHz以上的時鐘速度處理

2010-03-01 10:50:05 3788

3788

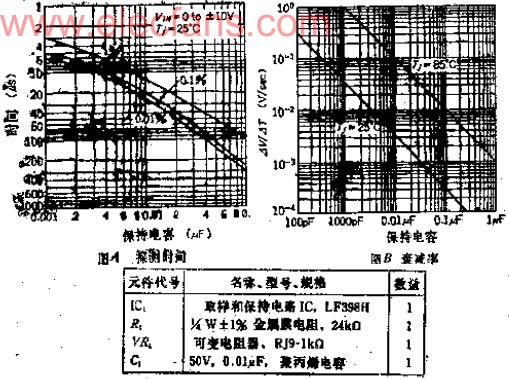

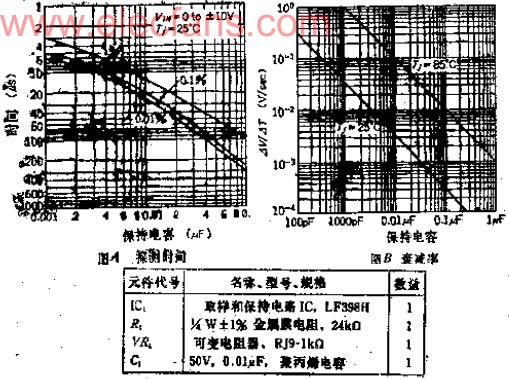

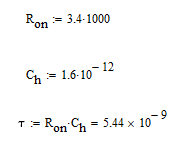

采樣時間為20US的中速采樣和保持電路

電路的功能

所謂采樣和保持

2010-05-05 15:53:51 1382

1382

采樣電路的特性參數

為了衡量采樣電路的工作特性,一般要考查以下的兒個主要參數。

1、獲得時間

2010-05-23 17:42:56 1573

1573

提出了一種應用于便攜式數字存儲示波器等效采樣的實現方案。詳細講述了FPGA和微處理器LPC2138對高頻信號隨機等效采樣的處理過程,利用一種全新的方法即主要利用FPGA內部邏輯單元完成對觸發時刻到與下一采樣時刻的時間間隔的測量。給出了FPGA對采樣點的處理方

2011-03-16 12:12:35 126

126 為了降低系統成本和功耗, 采用基于ARM 系統的精密時鐘發生電路對高頻信號(6. 25MHz~100MHz) 進行等效采樣, 配合高速AD、F IFO 和FPGA 電路設計并實現一個手持式存儲示波表。該樣機在人機

2011-06-21 16:33:41 114

114 本內容提供了2812片內ADC采樣時間計算。1)序列采樣模式(SMODE = 0)[attach]12497[/attach]

2011-09-05 11:39:36 3094

3094 對超寬帶系統中采樣門前置電路進行了理論分析和系統研究,對其產生電路中輸入信號的幅度和寬度、采樣信號的寬度和上升時間、等效采樣的時間間隔等因素的影響進行了分析,給出

2011-10-11 14:58:57 28

28 利用過采樣技術可在不需片外ADC器件的情況下,達到同樣的采樣效果。將Cortex-M3內核與過采樣技術相結合,不僅能夠降低成本,而且提升了系統的運行速率、可靠性與穩定性。

2012-02-06 16:41:07 41

41 在使用DSP進行數字信號處理時,應用過采樣技術可以增加其內置模數轉換器的分辨率。討論了應用過采樣技術的原理、如何使用TMS320LF2407來實現過采樣,以及在軟件上的實現方法。

2012-03-20 14:10:09 15

15 2015-08-24 18:14:00 18

18 基于FPGA多通道采樣系統設計資料,有興趣的同學可以下載學習

2016-04-28 14:29:56 48

48 基于FPGA實現變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 基于FPGA的高速多通道AD采樣系統的設計與實現_徐加彥

2017-01-18 20:23:58 12

12 等效采樣

2017-03-04 17:52:58 13

13 基于ARMCortex_M3的過采樣技術

2017-09-29 09:58:20 4

4 基于ARM Cortex-M3的過采樣技術

2017-10-30 16:39:17 8

8 ADC轉換就是輸入模擬的信號量,單片機轉換成數字量。讀取數字量必須等轉換完成后,完成一個通道的讀取叫做采樣周期。采樣周期一般來說=轉換時間+讀取時間。轉換時間=采樣時間+12.5個時鐘周期。采樣時間是你通過寄存器告訴STM32采樣模擬量的時間,設置越長越精確。

2017-11-14 14:52:57 30137

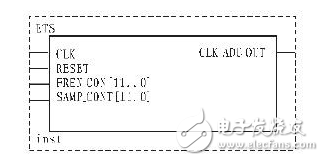

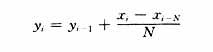

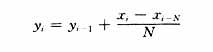

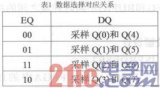

30137 的2倍以上,但在電阻抗多頻及參數成像技術中正交序列數字解調法的抗噪性能對信號每周期的采樣點數決定,采樣點數越多,抗噪性能越高。當采樣信號頻率很高時,為了在被采樣信號的一周期內多采樣,就需要提高采樣時鐘的頻率,但是由

2017-11-16 16:12:18 7

7 針對LVDS接口,研究并實現了一種基于FPGA的LVDS過采樣技術,重點對LVDS過采樣技術中系統組成、ISERDESE2、時鐘采樣、數據恢復單元、時鐘同步狀態機等關鍵技術進行了描述

2017-11-18 05:13:01 6915

6915

項目背景及可行性分析 1.項目名稱、項目的主要內容及目前的進展情況 項目名稱: 基于FPGA的高速采樣顯示電路的實現 主要內容:通過對被測信號的實時采樣,利用等效采樣原理,可以將采樣率為1MHz等效

2017-11-22 11:18:29 14

14 由于存在內部熱噪聲、孔徑抖動和渡越時間不確定性等因素,面臨采樣速度和精度相互制約的影響,出現了瓶頸。而由多通道時間交織ADC(Time-lnterleaved ADC.TIADC)采用M個相同型號的ADC單元依次交替完成采樣。理論上,TIADC的采樣率可以到達單ADC的M倍,同時保持采樣精度基本不

2018-02-07 13:51:17 2

2 RF采樣轉換器可捕獲高頻信號和大帶寬信號;但是,并非每種應用都能利用需要極高速采樣的信號。就帶寬或輸出頻率不過高的情況而言,利用RF采樣轉換器的高采樣速率能力仍存在一大優勢。

2018-05-02 09:30:50 7852

7852

誤差、增益誤差以及時間相位誤差將嚴重降低數據采集系統性能[2]。基于數字信號處理方法的數字后端修正技術可有效抑制以上失配造成的失真。近年來,已有文獻應用FPGA實現數字后端修正技術。文獻[3]采

2018-06-25 11:45:00 7047

7047

數據采集系統的總體架構如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內部實現。為實現多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態機控制下,完成模擬信號經過

2018-08-28 10:16:07 12734

12734

選擇實時采樣和等效采樣相結合的方式,實時采樣速率小于1 MS/s,水平分辨率至少為20點/div,故系統50 kHz以下采用實時采樣方式,而50 kHz~10 MHz采用等效時間采樣方式,最高等效采樣速率可達到200 Ms/s。

2019-05-05 08:19:00 2266

2266

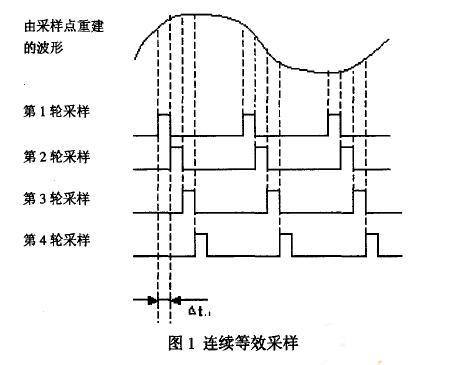

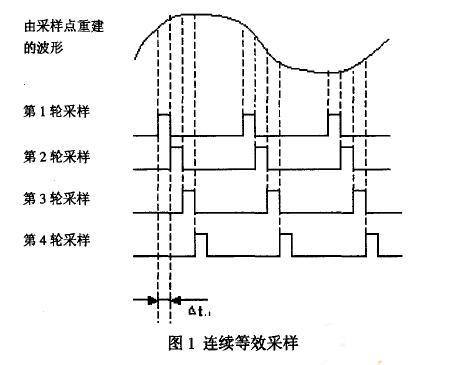

有兩種等效采樣的方法:隨機等效采樣和連續等效采樣。連續等效采樣在每個觸發捕獲一個樣值,而不依賴于時間/格的設置和掃描速度,每發現一個觸發經過一個雖然很短卻明確的延遲(deltat) ,就獲得

2018-11-08 08:40:00 6715

6715

過采樣技術是數字信號處理者用來提高模數轉換器(ADC)性能經常使用的方法之一,它通過減小量化噪聲,提高ADC的信噪比,從而提高ADC的有效分辨率[1]。過采樣技術不但沒有增加額外的模擬電路,而且由于提高了有效分辨率還能簡化模擬電路,并且簡單易行,因而被數字信號處理實踐者廣泛應用于測控領域

2018-12-19 09:55:55 2321

2321

過采樣技術在通信信號處理中的應用龍雄摘要:過采樣技術應用能夠促使各類通信信號能夠趨于平穩循環化發展,更利于技

2019-02-24 08:42:00 4837

4837

輸入系統的有正有負的模擬信號在AD采樣前,會加上了直流偏置變成全正信號才輸入AD的,所以在AD采樣后送給FPGA的信號是無符號數。

2019-08-11 11:43:39 2821

2821 采樣電阻是電流采樣和對電壓采樣。對電流采樣則串聯一個阻值較小的電阻,對電壓采樣則并聯一個阻值較大的電阻。采樣電阻又被稱為合金電阻、電流檢測電阻、取樣電阻等。

2019-11-08 08:47:34 8954

8954 的頻率,但是由于系統的ADC 器件時鐘速率并不能達到要求的高頻速率或者存儲處理速度等不能滿足要求因此我們可以采用低速ADC 器件通過等效時間采樣來對寬帶模擬信號進行數據采集從而使系統易于實現。

2020-03-12 10:22:48 2628

2628

信號傳輸中,數字信號將對模擬信號產生干擾,目前采用的解決方法是利用單片機來實現模擬信號和數字信號在單線中的混合傳輸,而這其中的測試和調試就要求示波器必須能夠對數字信號和模擬信號同時進行分析和顯示。因此,這里介紹一種基于等效和實時采樣數字示波器的設計。

2020-08-18 10:25:05 2001

2001

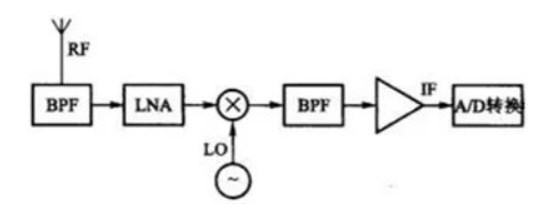

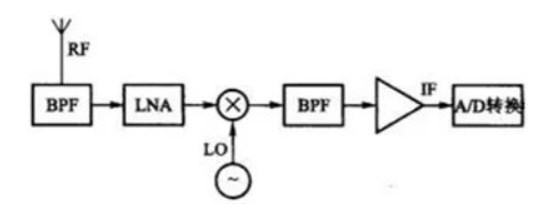

一、什么是中頻采樣,什么是IQ采樣 射頻接收系統通常使用數字信號處理算法進行信號解調和分析,因此需要使用ADC對信號進行采樣。根據采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣

2020-12-02 14:03:25 9031

9031 本文檔的主要內容詳細介紹的是基于FPGA的AD采樣的實現免費下載。

2021-01-21 15:33:54 31

31 AN-1543:ADuCM4050中用于時間同步的SensorStrobe和輸入采樣、傳感器數據采樣

2021-04-27 18:50:18 1

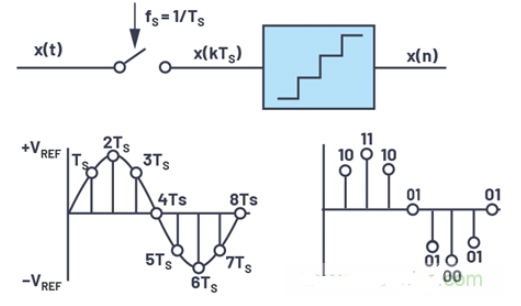

1 最終為此犧牲系統目標。 本文將會從采樣技術的基礎知識說起,重溫模數轉換的基本運作方式,并幫助大家理解現實中會遇到的問題。在接下來的后一篇文章中,我們會進一步介紹如何通過連續時間Σ-Δ ADC簡化信號鏈,有效地解決采樣中遇

2021-06-25 11:28:04 2582

2582

利用FPGA控制ADC0809采樣電壓(長城電源技術(山西有限公司)-利用FPGA控制ADC0809采樣電壓,并通過數碼管顯示電壓數值

2021-09-28 11:05:04 36

36 煙氣剖析儀的采樣體系分為慣例采樣體系和加熱采樣體系。 1、慣例采樣體系:一般選用耐酸堿,耐高溫的塑料管,確保對氣體無吸附。 適用狀況:含水量較低樣氣的短時間測驗;不含酸性氣體的樣氣的短時間測驗

2021-11-02 17:17:02 338

338 在A/D轉換器中,因為輸入的模擬信號在時間上式連續的,而輸出的數字信號代碼是離散的。所以A/D轉換器在進行轉換時,必須在一系列選定的瞬間(時間軸上的一些規定點上)對輸入的模擬信號采樣保持,然后再

2021-11-11 12:36:05 3

3 STM32: ADC采樣頻率及相應時間的確定

2021-11-26 20:36:05 19

19 ADC轉換就是輸入模擬的信號量,單片機轉換成數字量。讀取數字量必須等轉換完成后,完成一個通道的讀取叫做采樣周期。采樣周期一般來說=轉換時間+讀取時間。而轉換時間=采樣時間+12.5個時鐘周期。采樣

2021-11-26 20:36:06 88

88 STM32 ADC 過采樣技術

2021-12-08 16:21:06 41

41 第一:前言用STM32 采集數據必須依據信號源設置采樣頻率。根據奈奎斯特定律,采樣率必須是信號源最大頻率的2倍以上,但是在實際的需求當中,采樣率應該是Fs>3Fmax .采樣周期=轉換時間

2021-12-14 18:57:51 42

42 對過采樣技術的理解與記憶

2022-02-07 15:36:06 663

663 射頻接收系統通常使用數字信號處理算法進行信號解調和分析,因此需要使用ADC對信號進行采樣。根據采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣和中頻采樣只需要一路ADC,采樣結果

2022-07-28 09:05:47 2626

2626 示波器采樣頻率,又稱采樣速度或采樣率,定義了每秒從連續信號中提取并形成離散信號的采樣數量,它使用赫茲(Hz)來表示,采樣頻率倒數為采樣周期或采樣時間,即采樣間隔,一般來說,采樣頻率是指計算機每秒采集多少個信號樣本。

2022-09-14 15:38:13 2709

2709 評估快速和超快速數據轉換器動態性能的最有用技術之一是相干采樣。這種技術提高了快速傅立葉變換(FFT)的光譜分辨率,并且在滿足某些條件時無需進行窗口采樣。但是,如果不能滿足相干采樣的條件,則可

2023-02-25 10:07:07 2822

2822

本文分析數字電源ADC采樣時間的原理、誤差來源、改善方法。

2023-03-08 15:01:00 3182

3182

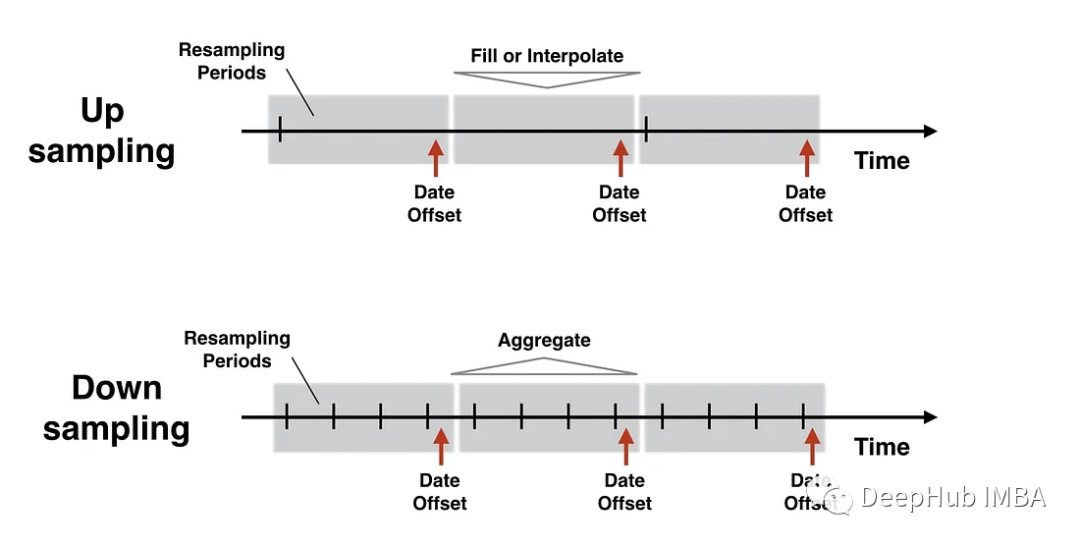

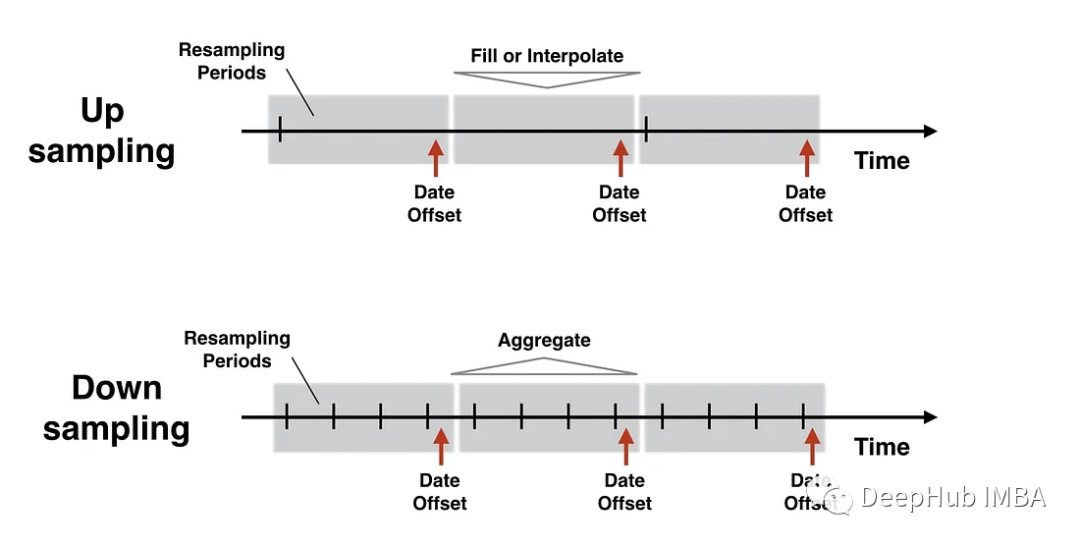

點擊上方 藍字 關注我們 ?采樣就是采集模擬信號的樣本。通常采樣指的是下采樣,也就是對信號的抽取。其實,上采樣和下采樣都是對數字信號進行重采,重采的采樣率與原來獲得該數字信號的采樣率比較,大于原信號

2023-06-08 17:15:03 732

732 用于等效時間采樣應用的空間多路單腔雙光梳激光器1介紹雙光學頻率梳(簡稱雙光梳)[1]的概念在光頻梳被提出后不久被引入[2-4]。在時域上,雙光梳可以理解為兩個相干光脈沖序列,它們的重復頻率有輕微

2022-05-26 09:47:05 460

460

更改信號采樣率是數字信號處理中的一個重要操作,它涉及對信號進行重新采樣,以改變信號的采樣率。

2023-06-20 14:44:37 2543

2543 ,就需要提高采樣時鐘的頻率,但是由于系統的ADC 器件時鐘速率并不能達到要求的高頻速率或者存儲處理速度等不能滿足要求因此我們可以采用低速ADC 器件通過等效時間采樣來對寬帶模擬信號進行數據采集從而使系統易于實現。 1 等效時間采

2023-07-29 09:00:01 537

537

對于相同的信號周期(下述圓),每隔一段時間采樣點移動一次為采樣率,表格為三種不同采樣率。由表知采樣率1采樣速度最慢,采樣率2最快,采樣率3居中

2023-08-17 10:11:13 1799

1799

重采樣是時間序列分析中處理時序數據的一項基本技術。它是關于將時間序列數據從一個頻率轉換到另一個頻率,它可以更改數據的時間間隔,通過上采樣增加粒度,或通過下采樣減少粒度。

2023-09-19 17:06:15 1204

1204

什么是示波器的實時采樣率? 什么是示波器的等效時間采樣? 示波器是一種測試儀器,用于顯示波形和信號的性質。實時采樣率是指示波器在一個時間單位內(通常是1秒),可以將信號進行采樣的次數。它是示波器

2023-10-17 16:16:07 920

920 示波器采樣時間怎么設置 示波器的采樣率有什么意義? 一、示波器采樣時間的設置 1. 示波器采樣時間的概念 示波器的采樣時間指的是示波器通過在指定時間段內獲取的樣本數量來描述示波器的性能。示波器采樣

2023-10-17 16:16:10 2207

2207 中頻采樣是什么意思?中頻采樣與基帶采樣的區別? 中頻采樣與基帶采樣都是數字信號處理中常用的采樣技術,它們的區別在于采樣信號的頻率不同。基帶采樣是指在信息原始頻域內進行采樣,而中頻采樣是指在信號已經

2023-10-22 11:24:39 1146

1146 什么是中頻采樣?什么是IQ采樣?中頻采樣和IQ采樣的比較和轉換? 中頻采樣和IQ采樣是數字信號處理中非常重要的概念。在數字信號處理中,模擬信號需要經過采樣變成數字信號,這樣才能讓數字電路加以處理

2023-10-22 11:24:42 2240

2240

2023-11-07 08:31:41 0

0 電子發燒友網站提供《奈奎斯特準則如何運用于基帶采樣、欠采樣和過采樣應用.pdf》資料免費下載

2023-11-28 09:25:33 0

0 示波器實時采樣與等效采樣有何區別? 示波器實時采樣和等效采樣是示波器在測量電信號時使用的兩種不同的方法。它們在采樣速度、信號還原精度、存儲和處理能力等方面有所不同。下面將詳細介紹這兩種采樣方法的區別

2023-12-21 14:02:19 319

319 等效時間采樣示波器與實時示波器的對比,有什么不同? 等效時間采樣示波器和實時示波器是電子測試設備中常用的兩種示波器。它們在運行原理、應用場景、優點和缺點等方面存在一些顯著差異。 一、等效時間采樣

2024-01-19 11:29:28 321

321

電子發燒友App

電子發燒友App

評論