前言

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。時(shí)鐘作為數(shù)字系統(tǒng)中的“心臟”,其設(shè)計(jì)的質(zhì)量好壞直接關(guān)乎整個(gè)系統(tǒng)的穩(wěn)定性,本文主要介紹了數(shù)字設(shè)計(jì)中的常見(jiàn)的時(shí)鐘產(chǎn)生電路和時(shí)鐘類型,并進(jìn)行相關(guān)分析簡(jiǎn)介。

時(shí)鐘產(chǎn)生電路

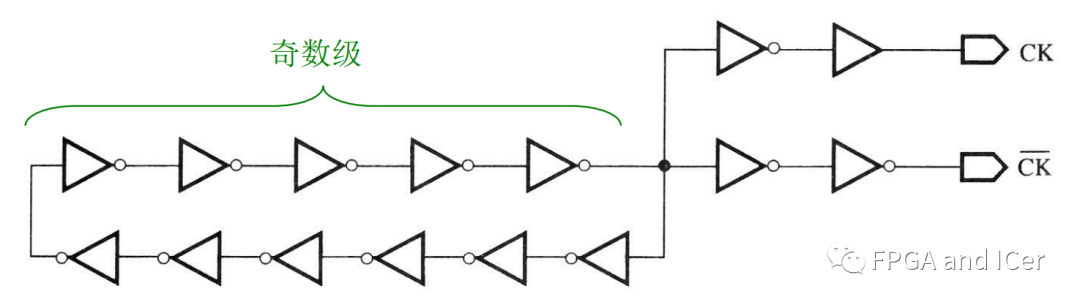

奇數(shù)個(gè)反相器首尾相連即構(gòu)成環(huán)形振蕩器(簡(jiǎn)稱 「“環(huán)振”」 ),每個(gè)反相器兩端出現(xiàn)周期性振蕩信號(hào)。

環(huán)形振蕩器

假定每個(gè)反相器都相同,所產(chǎn)生的時(shí) 鐘周期T或頻率f取決于反相器鏈的級(jí)數(shù)N和反相器的傳播延時(shí)tp

可通過(guò)改變反相器的級(jí)數(shù)以及每個(gè)反相器的面積來(lái)改變輸出的時(shí)鐘頻率。

「環(huán)形振蕩器的優(yōu)缺點(diǎn)如下:」

「優(yōu)點(diǎn):」 電路簡(jiǎn)單,無(wú)需外接元器件,完全片上集成。

「缺點(diǎn):」 頻率精度差,隨工藝、電源電壓離散的變化大;頻率穩(wěn)定性差,隨時(shí)間、 溫度的變化大。

針對(duì)該時(shí)鐘的特點(diǎn),因此該時(shí)鐘適用于對(duì)精度和穩(wěn)定度要求都不高的片上時(shí)鐘產(chǎn)生器。

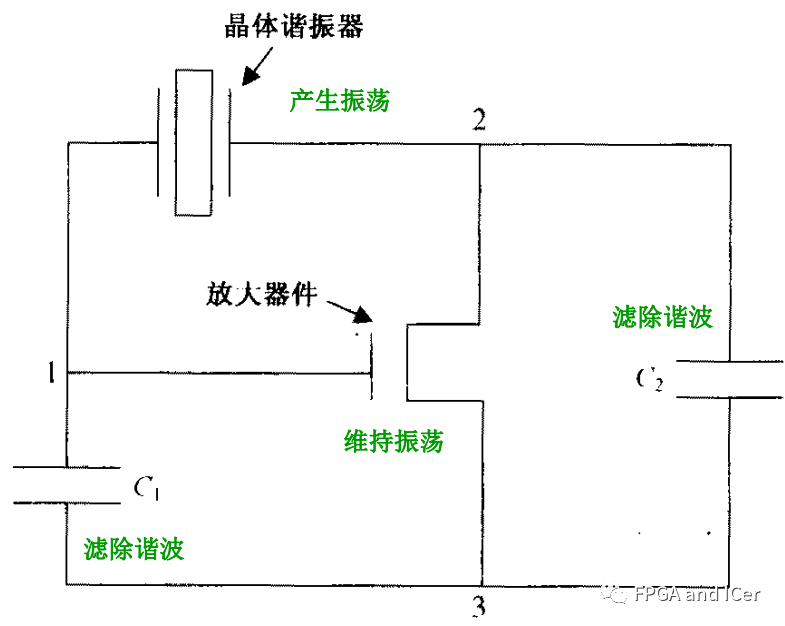

晶體振蕩器

晶體震蕩電路主要構(gòu)成如下,主要由晶體諧振器產(chǎn)生震蕩,電容進(jìn)行濾除振蕩產(chǎn)生的諧波,放大器將篩選出的頻率進(jìn)行維持并進(jìn)行放大,從而產(chǎn)生穩(wěn)定的時(shí)鐘信號(hào)。

石英晶體兩端加上電壓后,就會(huì)產(chǎn)生振蕩電流(機(jī)械能 電能),振蕩頻率由晶體的尺寸與形狀決定(晶體越薄越小,頻率越高)。

「晶體振蕩器的優(yōu)缺點(diǎn)如下:」

「優(yōu)點(diǎn):」 晶體振蕩器頻率穩(wěn)定性高,可達(dá)10 ^ -6 (ppm), 而環(huán)形振蕩器只能達(dá)到 10 ^ -2(ppm)。

「缺點(diǎn):」 晶體振蕩器輸出頻率范圍一般不超過(guò)100MHz,難以滿足現(xiàn)代高速數(shù)字IC的更高時(shí)鐘頻率要求;而且采用非硅工藝的石英諧振器,無(wú)法片內(nèi)集成;輸出頻率難以調(diào)節(jié),只能產(chǎn)生單一頻率。

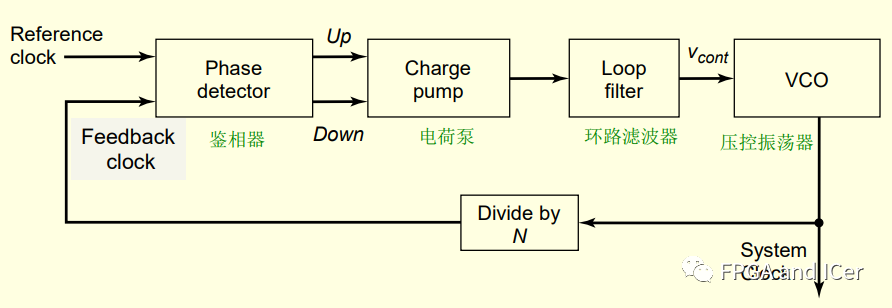

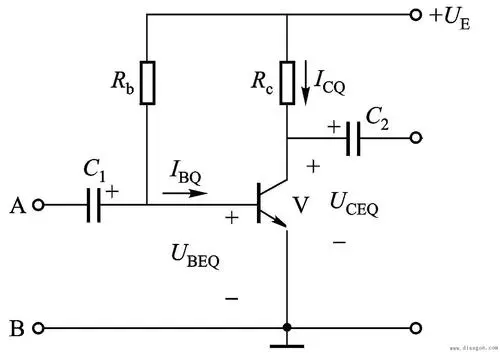

PLL鎖相環(huán)電路

鎖相環(huán) (PLL) 是一種反饋電路,且為模擬電路,性能受工藝、電源噪聲、溫度等的 影響顯著,設(shè)計(jì)難度較大。

PLL電路的工作原理是將外部信號(hào)的相位與壓控晶體振蕩器 (VCXO) 產(chǎn)生的時(shí)鐘信號(hào)的相位進(jìn)行比較。然后,電路調(diào)整振蕩器時(shí)鐘信號(hào)的相位以匹配參考信號(hào)的相位。因此,原始參考信號(hào)和新信號(hào)彼此是精確同相的。

PLL鎖相環(huán)電路

一個(gè)鎖相環(huán)PLL電路通常由以下模塊組成:

「鑒相鑒頻器PFD(Phase Frequency Detector):」 將分頻后的反饋時(shí)鐘與參考時(shí)鐘的相位進(jìn)行比較,若反饋時(shí)鐘滯后/領(lǐng)先參考時(shí)鐘,則發(fā)生一個(gè)Up/Down信號(hào)。該信號(hào)的大小正比于所檢測(cè)到的相位差。

**電荷泵: ** 電荷泵將Up/Down信號(hào)轉(zhuǎn)換為一個(gè)較大/較小的模擬控制電壓Vcont,以便加速/減慢VCO, 從而消除反饋時(shí)鐘與參考時(shí)鐘的相位差。

「低通濾波器(環(huán)路濾波器)LPF(Low-Pass Filter、Loop Filter):」 用于濾除Vcont中的高頻成分并平滑其響應(yīng),減少本地時(shí)鐘的抖動(dòng)。

「壓控振蕩器VCXO(Voltage Controlled Oscillator):」 壓控振蕩器產(chǎn)生系統(tǒng)時(shí)鐘信號(hào),信號(hào)的頻率受輸入電壓Vcont的控制。利用變?nèi)?a target="_blank">二極管(偏置電壓的變化會(huì)改變耗盡層的厚度,從而影響電容大小)與電感構(gòu)成的LC諧振電路構(gòu)成,提高變?nèi)荻O管的逆向偏壓,二極管內(nèi)耗盡層變大,電容變小,LC電路的諧振頻率提高,反之,降低逆向偏壓時(shí),二極管內(nèi)電容變大,頻率降低。

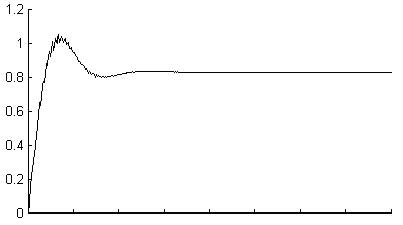

DLL和PLL具有類似的功能,可以完成時(shí)鐘高精度、低抖動(dòng)的倍頻和分頻,以及占空比調(diào)整和移相等功能。DLL即Delay Lock Loop,主要是用于產(chǎn)生一個(gè)精準(zhǔn)的時(shí)間延遲,且這個(gè)delay不隨外界條件如溫度,電壓的變化而改變。PLL利用壓控振蕩器調(diào)整頻率來(lái)改變相位,DLL利用壓控延遲線調(diào)整延時(shí)來(lái)改變相位。

DLL調(diào)整相位的方法是用壓控延遲線(VCDL,Votage-Controlled Delay Line)而非 VCO,通過(guò)改變延時(shí)而非頻率。

「PLL/DLL電路的優(yōu)缺點(diǎn)如下:」

「優(yōu)點(diǎn):」 穩(wěn)定性好,無(wú)需積分運(yùn)算,極點(diǎn)少;鎖定速度快,PLL需要先鎖定頻率再鎖定相位,DLL直接鎖定相位;抗抖動(dòng)與噪聲性能好,無(wú)環(huán)振VCO 那樣的反饋路徑,對(duì)工藝與環(huán)境波動(dòng)不敏感;可直接產(chǎn)生多相時(shí)鐘。

「缺點(diǎn):」 無(wú)法改變輸出頻率,不能倍頻,不 能產(chǎn)生多個(gè)時(shí)鐘頻率;調(diào)節(jié)范圍較大時(shí),可能產(chǎn)生錯(cuò)誤鎖定。

時(shí)鐘類型

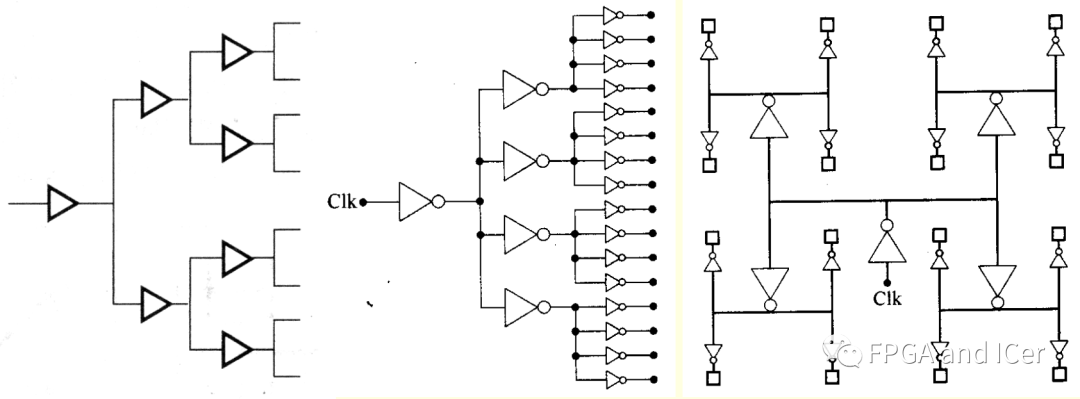

全局時(shí)鐘

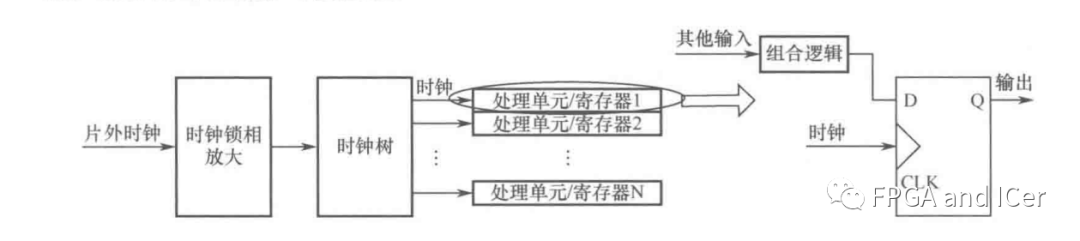

全局時(shí)鐘(Global Clock)。一般的時(shí)鐘都指的是全局時(shí)鐘,全局時(shí)鐘在芯片中的體現(xiàn)形式是時(shí)鐘樹(shù)。

時(shí)鐘樹(shù)

它是由片上的時(shí)鐘管腳引入,經(jīng)過(guò)鎖相和放大之后進(jìn)入時(shí)鐘樹(shù),輸出給寄存器的穩(wěn)定、可靠的時(shí)鐘信號(hào)。這種時(shí)鐘的時(shí)延通常被設(shè)計(jì)得最小,相對(duì)抖動(dòng)也最小。

內(nèi)部時(shí)鐘

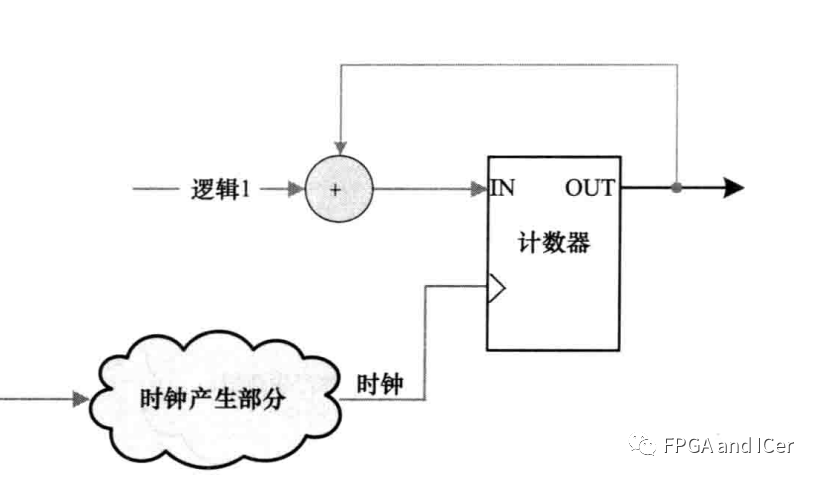

對(duì)于內(nèi)部時(shí)鐘最早的接觸應(yīng)該就是使用計(jì)數(shù)器輸出的計(jì)數(shù)值的相關(guān)邏輯做分頻時(shí)鐘。但如果設(shè)計(jì)不當(dāng),該部分會(huì)導(dǎo)致設(shè)計(jì)功能和時(shí)序問(wèn)題。組合邏輯電路的常見(jiàn)的引起設(shè)計(jì)錯(cuò)誤的問(wèn)題:毛刺和延時(shí),同時(shí)也是組合邏輯搭建的時(shí)鐘所面對(duì)的問(wèn)題。往簡(jiǎn)單了說(shuō),組合邏輯的毛刺會(huì)引起功能的異常,降低系統(tǒng)的穩(wěn)定;延時(shí)會(huì)引起在時(shí)鐘進(jìn)行時(shí)序分析的相關(guān)問(wèn)題,下面就這兩方面進(jìn)行說(shuō)明。

組合邏輯搭建的時(shí)鐘產(chǎn)生器會(huì)引入毛刺,使功能出現(xiàn)問(wèn)題,此外由組合邏輯所導(dǎo)致的延遲也會(huì)導(dǎo)致時(shí)序方面的問(wèn)題。在同步設(shè)計(jì)中,數(shù)據(jù)輸入端的毛刺不會(huì)引起任何問(wèn)題,因?yàn)閿?shù)據(jù)是在時(shí)鐘邊沿處捕獲的,所以可以將毛刺自動(dòng)濾掉。然而,如果毛刺或尖峰脈沖出現(xiàn)在時(shí)鐘輸入端(或者寄存器的異步輸入端)就會(huì)產(chǎn)生明顯的影響。

下圖通過(guò)邏輯設(shè)計(jì)產(chǎn)生了時(shí)鐘,時(shí)鐘產(chǎn)生部分包含一些組合邏輯,而計(jì)數(shù)器的寄存器是對(duì)邊沿敏感的,這就導(dǎo)致下圖的設(shè)計(jì)毛刺會(huì)明顯影響到計(jì)數(shù)器的值。

邏輯設(shè)計(jì)時(shí)鐘產(chǎn)生

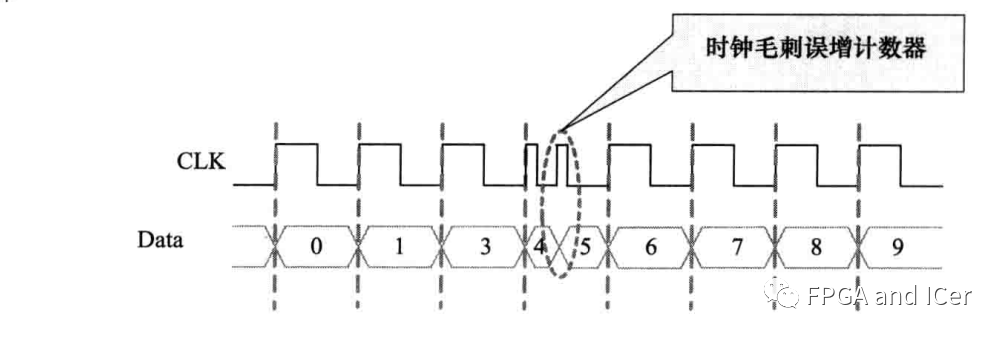

在下面這個(gè)例子中可以看到,由于時(shí)鐘沿處的毛刺,計(jì)數(shù)器在所示的時(shí)鐘周期上遞增了兩次。由于時(shí)鐘毛刺的作用,計(jì)數(shù)器增加了額外的計(jì)數(shù)值,這樣就可能導(dǎo)致功能出現(xiàn)問(wèn)題。

毛刺導(dǎo)致邏輯錯(cuò)誤

窄毛刺會(huì)違背寄存器的最小脈沖寬度要求。在毛刺到達(dá)時(shí)鐘輸入端時(shí),如果寄存器的數(shù)據(jù)輸入變化,會(huì)違背建立和保持時(shí)間。即使設(shè)計(jì)沒(méi)有違背時(shí)序要求,寄存器也可能輸出意料之外的值,使整個(gè)設(shè)計(jì)功能出現(xiàn)風(fēng)險(xiǎn)。

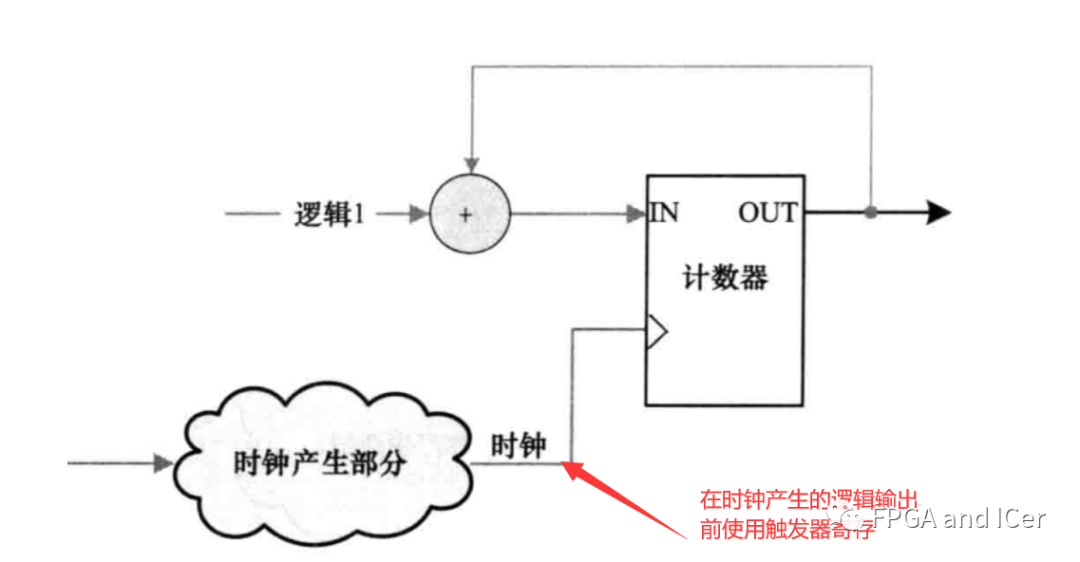

解決毛刺引發(fā)的設(shè)計(jì)功能問(wèn)題,最簡(jiǎn)單的辦法就是使用寄存器在時(shí)鐘產(chǎn)生邏輯后寄存輸出,這樣無(wú)論前級(jí)的時(shí)鐘產(chǎn)生部分的代碼是否存在毛刺,都使用觸發(fā)器做了寄存,降低了毛刺引起功能錯(cuò)誤的風(fēng)險(xiǎn)。

解決方法

分析完毛刺的影響,下面分析下組合邏輯構(gòu)建的時(shí)鐘引入的延遲問(wèn)題。

用來(lái)產(chǎn)生內(nèi)部時(shí)鐘的組合邏輯也會(huì)增加時(shí)鐘線上的延遲。在某些情況下,時(shí)鐘線上的邏輯延遲會(huì)導(dǎo)致時(shí)鐘偏移比兩個(gè)寄存器之間的數(shù)據(jù)路徑延遲更大。如果時(shí)鐘偏移大于數(shù)據(jù)延遲,就會(huì)違背寄存器的時(shí)序要求,設(shè)計(jì)的功能也不會(huì)正確。

因此,就需要設(shè)計(jì)時(shí)鐘時(shí)盡量減少時(shí)鐘偏斜,一種減少時(shí)鐘偏移的方法是將產(chǎn)生的時(shí)鐘放到SoC中高扇出且低偏移值的時(shí)鐘樹(shù)上。「使用低偏移值時(shí)鐘樹(shù)有助于減少信號(hào)整體的時(shí)鐘偏移。」

分頻時(shí)鐘

許多設(shè)計(jì)需要來(lái)自于主時(shí)鐘的分頻時(shí)鐘。在設(shè)計(jì)中要保證大多數(shù)時(shí)鐘來(lái)自于PLL。使用PLL能避免由異步時(shí)鐘分頻邏輯引起的許多問(wèn)題。在對(duì)主時(shí)鐘進(jìn)行分頻時(shí),應(yīng)該始終使用同步計(jì)數(shù)器或狀態(tài)機(jī)。

此外,設(shè)計(jì)應(yīng)該保證總是由寄存器直接產(chǎn)生分頻時(shí)鐘信號(hào)。不要對(duì)計(jì)數(shù)器或狀態(tài)機(jī)的輸出進(jìn)行解碼,然后產(chǎn)生時(shí)鐘信號(hào);這種實(shí)現(xiàn)方式常會(huì)導(dǎo)致毛刺和尖峰脈沖。可參考內(nèi)部時(shí)鐘的舉例。

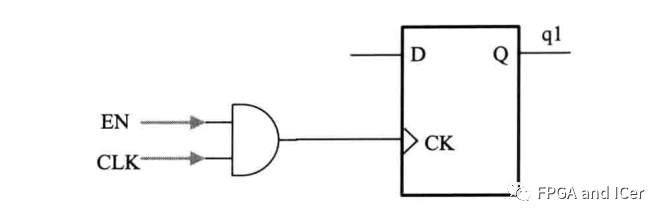

門控時(shí)鐘

門控時(shí)鐘的時(shí)鐘線上的門控單元會(huì)導(dǎo)致時(shí)鐘偏移,并會(huì)引入尖峰脈沖作用于觸發(fā)器。但在涉及到低功耗設(shè)計(jì)時(shí)(通常ASIC中),門控時(shí)鐘還是比較常用的。

門控時(shí)鐘

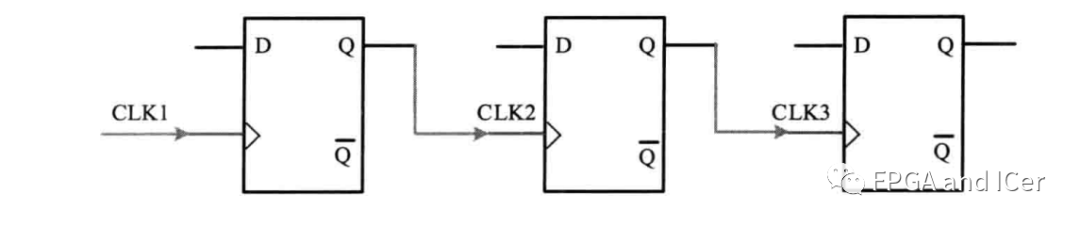

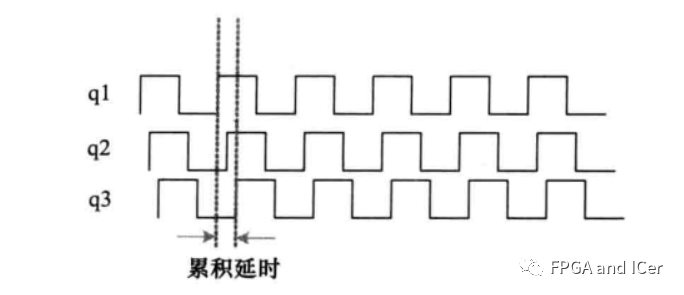

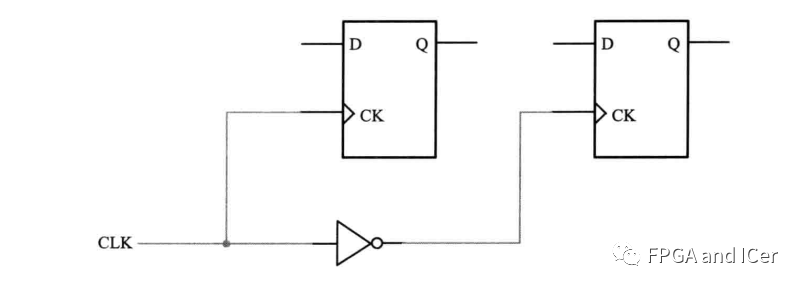

行波時(shí)鐘

行波計(jì)數(shù)器:將觸發(fā)器前級(jí)輸入引腳連接至下個(gè)寄存器的輸入引腳,依次級(jí)聯(lián)。由于第一個(gè)觸發(fā)器時(shí)鐘到Q的延遲而使第二個(gè)觸發(fā)器的時(shí)鐘輸入產(chǎn)生偏移,而且不能在每個(gè)時(shí)鐘邊沿都激活。此時(shí),延時(shí)逐漸累積會(huì)在引入時(shí)序分析和綜合麻煩,因此需要盡量避免使用這種結(jié)構(gòu),

行波計(jì)數(shù)器

積累延時(shí)

盡管使用行波計(jì)數(shù)器(或者行波時(shí)鐘)存在各種問(wèn)題,但是在功耗較高的系統(tǒng)中很適合使用這種計(jì)數(shù)器,因?yàn)檫@樣能大量降低由邏輯或SoC所引起的峰值功耗。

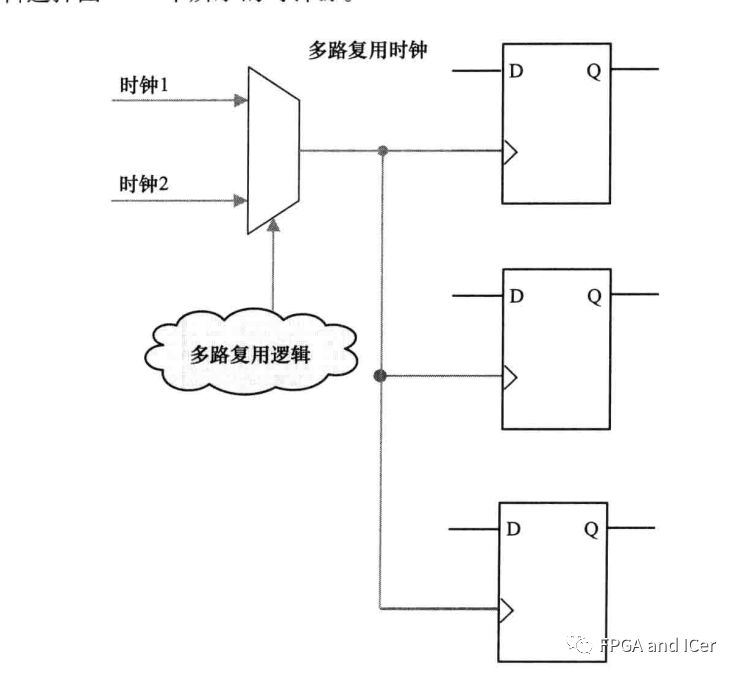

多路時(shí)鐘

時(shí)鐘多路器用于使同一個(gè)邏輯功能具有不同的時(shí)鐘。某些類型的多路邏輯選擇如下圖所示的時(shí)鐘源。

多路邏輯選擇時(shí)鐘源

例如,需要處理多個(gè)頻率標(biāo)準(zhǔn)的通信應(yīng)用常常使用多個(gè)時(shí)鐘。雖然在時(shí)鐘信號(hào)上引入邏輯上的問(wèn)題,是在不同的應(yīng)用中對(duì)多路時(shí)鐘的要求差別很大。

在能滿足下面的標(biāo)準(zhǔn),時(shí)鐘多路操作就是可接受的:

在初始化配置后,時(shí)鐘多路邏輯就不再改變。

在測(cè)試時(shí),設(shè)計(jì)會(huì)繞過(guò)功能時(shí)鐘多路邏輯而選擇普通時(shí)鐘。

在時(shí)鐘切換時(shí),寄存器始終處于復(fù)位狀態(tài)。

在時(shí)鐘切換時(shí)產(chǎn)生的短暫錯(cuò)誤響應(yīng)沒(méi)有負(fù)面影響。

如果設(shè)計(jì)中時(shí)鐘切換很頻繁,并且不在復(fù)位時(shí)切換,設(shè)計(jì)也不能容忍芯片中出現(xiàn)短暫的錯(cuò)誤響應(yīng),就必須使用同步設(shè)計(jì)以確保寄存器沒(méi)有違背時(shí)序,時(shí)鐘信號(hào)上不出現(xiàn)毛刺同時(shí)沒(méi)有競(jìng)爭(zhēng)條件或其他麻煩。

為了實(shí)現(xiàn)時(shí)鐘切換,在xilinx的原語(yǔ)中,存在CLK選擇的結(jié)構(gòu)以供設(shè)計(jì)者進(jìn)行選擇設(shè)計(jì),按下面的原語(yǔ)示例,設(shè)計(jì)時(shí)需要控制信號(hào)S滿足建立時(shí)間和保持時(shí)間,可實(shí)現(xiàn)時(shí)鐘的無(wú)毛刺切換。

?

?

???BUFGMUX?#(

??????.CLK_SEL_TYPE("SYNC")??//?ASYNC,?SYNC

???)

???BUFGMUX_inst?(

??????.O(O),???//?1-bit?output:?Clock?output

??????.I0(I0),?//?1-bit?input:?Clock?input?(S=0)

??????.I1(I1),?//?1-bit?input:?Clock?input?(S=1)

??????.S(S)????//?1-bit?input:?Clock?select

???);

?

?

雙邊沿或混合邊沿時(shí)鐘

雙邊沿時(shí)鐘是指在時(shí)鐘的上升沿和下降沿都進(jìn)行數(shù)據(jù)傳輸,兩個(gè)觸發(fā)器由兩個(gè)相位相反的時(shí)鐘信號(hào)控制。

雙邊沿或混合邊沿時(shí)鐘

這樣操作會(huì)為使用同步復(fù)位和使用插入掃描鏈這樣的測(cè)試方法帶來(lái)麻煩,同時(shí)也會(huì)增加確定關(guān)鍵信號(hào)的路徑的難度。

但雙沿采樣時(shí)鐘也是有好處的。

雙沿時(shí)鐘使得原本一個(gè)周期輸出/輸入一個(gè)數(shù)據(jù)的架構(gòu),改變?yōu)橐粋€(gè)周期輸出/輸入兩個(gè)數(shù)據(jù),這樣在不升高時(shí)鐘頻率的前提下,提升了信號(hào)的吞吐率,從而帶來(lái)「性能的提升」。另外一個(gè)使用雙沿時(shí)鐘的優(yōu)勢(shì)是「降低功耗」,因?yàn)闀r(shí)鐘頻率減半,所以系統(tǒng)的功耗只有等效同步電路的一半。

但一般情況下,不建議使用雙邊沿時(shí)鐘,這是因?yàn)椋?/p>

由于上下沿都用,要求時(shí)鐘的質(zhì)量很高,一般的時(shí)鐘源很難達(dá)到,成本高。

由于時(shí)鐘的抖動(dòng)等不確定因素的存在,容易使時(shí)鐘的占空比發(fā)生改變,因此容易引起建立時(shí)間和保持時(shí)間的違規(guī)。

?

在FPGA中的通常高速傳輸時(shí)會(huì)用到雙沿采樣時(shí)鐘,DDR存儲(chǔ)同樣也是使用的雙沿采樣,但在常規(guī)情況下不使用雙沿采樣時(shí)鐘。

?

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論