InTime。 前言 高層次的設(shè)計可以讓設(shè)計以更簡潔的方法捕捉,從而讓錯誤更少,調(diào)試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復(fù)雜的 FPGA 設(shè)計上實現(xiàn)高性能,往往需要手動優(yōu)化 RTL 代碼,這也意味著從 C 轉(zhuǎn)化得到 RTL 基本不可能。其實,使用 FPGA 工具設(shè)置來優(yōu)化設(shè)計可以最

2020-12-20 11:46:46 1416

1416

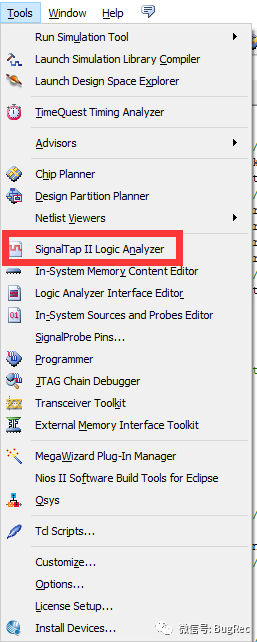

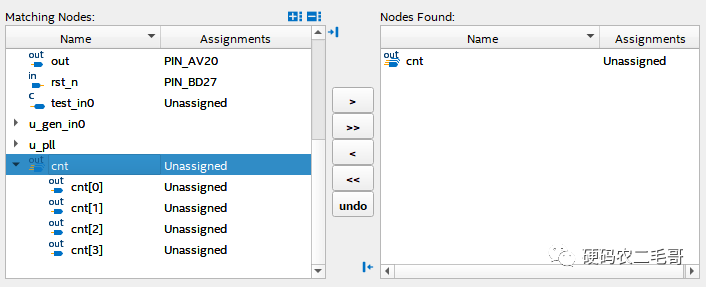

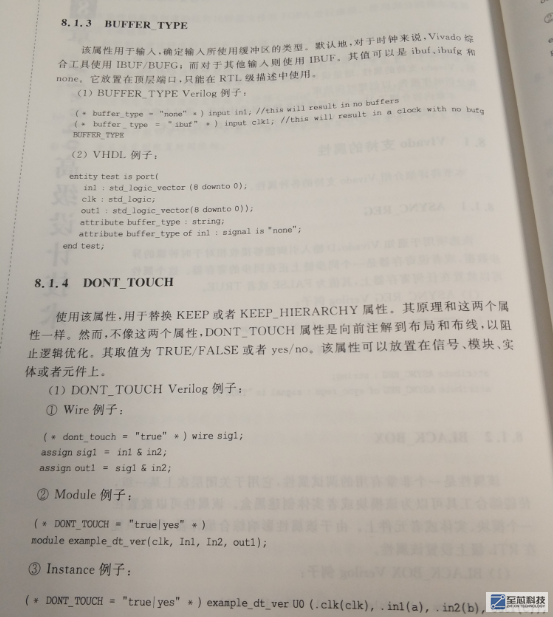

本文分別對quartus和vivado防止信號被優(yōu)化的方法進行介紹。

2023-05-25 11:25:46 1887

1887

上篇主要是分享了Vivado編譯軟件遠程調(diào)試的方法。杰克使用Vivado軟件進行遠程連接,主要是用于固化程序以及FPGA(PL端)的異常排查。而本篇主要內(nèi)容是對使用Vitis軟件遠程調(diào)試的方法進行總結(jié)和分享。

2023-05-25 14:36:58 1685

1685

今天跟大家分享的內(nèi)容很重要,也是調(diào)試FPGA經(jīng)驗的總結(jié)。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設(shè)計越來越多。在調(diào)試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼

2023-08-01 09:18:34 1041

1041

本文主要闡述了MOSFET在模塊電源中的應(yīng)用,分析了MOSFET損耗特點,提出了優(yōu)化方法;并且闡述了優(yōu)化方法與EMI之間的關(guān)系。

2023-08-17 09:16:30 1300

1300

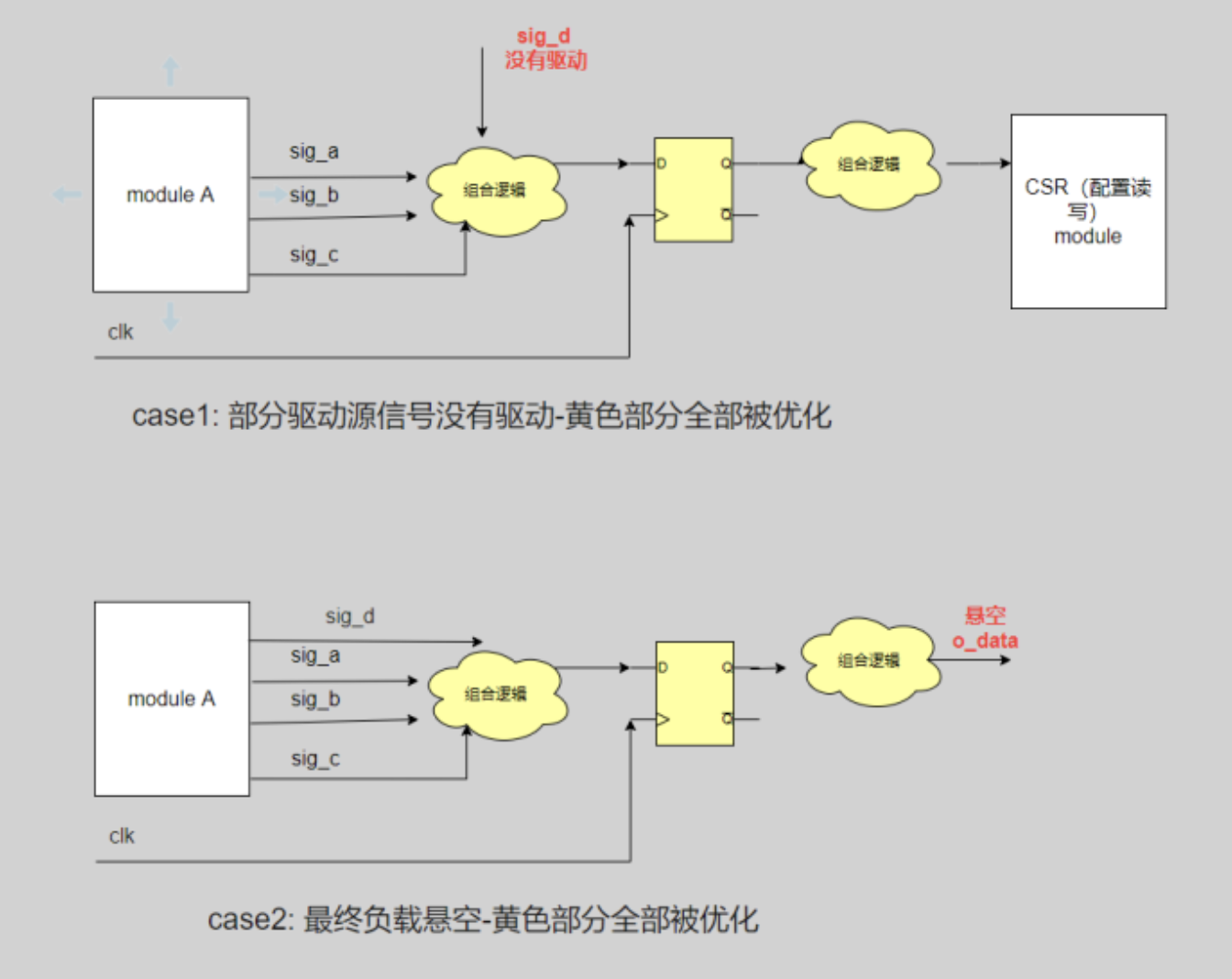

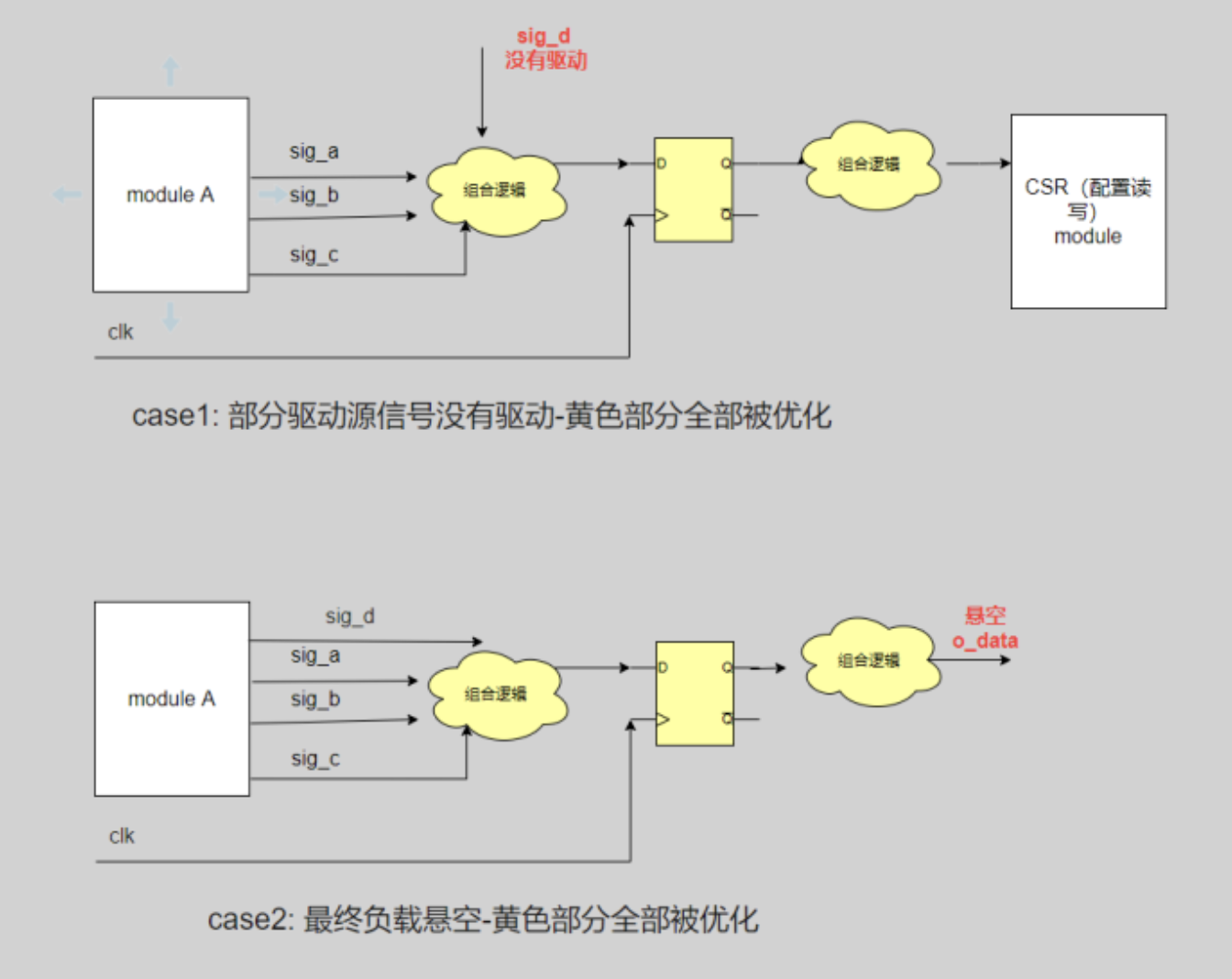

在項目初期,在使用FPGA工具quartus或者vivado生成版本燒入開發(fā)板進行調(diào)試時(DC開啟優(yōu)化選項后同樣會優(yōu)化掉寄存器),我們有時會發(fā)現(xiàn)部分寄存器被優(yōu)化掉了,今天簡單聊聊被優(yōu)化的幾種情況。

2023-09-08 15:09:59 1221

1221

時間,降低了制造成本。直觀的邏輯合成環(huán)境包括先進的優(yōu)化技術(shù)、屢獲殊榮的時序分析和先進的推論技術(shù),適用于與供應(yīng)商無關(guān)的設(shè)計中,可加快產(chǎn)品上市時間、消除設(shè)計缺陷以及提供極佳的結(jié)果質(zhì)量 (QoR)。 FPGA

2018-09-20 11:11:16

FPGA中的I_O時序優(yōu)化設(shè)計在數(shù)字系統(tǒng)的同步接口設(shè)計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優(yōu)化設(shè)計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

的板級調(diào)試方法有很多,借助于常規(guī)的示波器和邏輯分析儀的調(diào)試方法是最典型的手段。如圖10.1所示,基于傳統(tǒng)的臺式示波器或邏輯分析儀進行板級調(diào)試有著諸多的不便,相對于設(shè)計電路深藏在芯片內(nèi)部的FPGA

2015-09-02 18:39:49

FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點介紹了DDS技術(shù)在FPGA中的實現(xiàn)

2012-08-11 18:10:11

FPGA的時序優(yōu)化高級研修班通知通過設(shè)立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優(yōu)化的方法。1.FPGA靜態(tài)時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優(yōu)化方法

2013-03-27 15:20:27

FPGA 設(shè)計優(yōu)化主要分為編碼風(fēng)格、設(shè)計規(guī)劃和時序收斂三大部分,這 些因素直接決定了 FPGA 設(shè)計的成敗。 編碼風(fēng)格直接影響 FPGA 設(shè)計的實現(xiàn)并最終影響設(shè)計的性能。盡管綜合 工具集成

2022-09-29 06:12:02

摘要:主要討論了FPGA設(shè)計中毛刺信號產(chǎn)生的原因,分析總結(jié)了處理毛刺信號的幾種方法,通過對毛刺信號的處理可以提高芯片的穩(wěn)定性。隨著FPGA(Field Programmable Gate Array

2009-04-21 16:47:58

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級設(shè)計

2021-04-15 06:33:58

各位大神,小弟最近在做一個項目,由于之前選用的FPGA資源不夠,現(xiàn)在需要將程序的資源占用率降下來。經(jīng)過我的冥思苦想,也找不到好的方法,不知道各位大神平時工作中降低資源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

的幀速率,使其成為更好、更流暢的體驗。

本指南介紹了優(yōu)化Unity程序的方法,尤其是它們的GPU使用。

本指南將優(yōu)化分為三章:

?應(yīng)用程序處理器優(yōu)化?GPU優(yōu)化?資產(chǎn)優(yōu)化

2023-08-02 18:52:09

優(yōu)化的度 網(wǎng)站優(yōu)化的方法有很多,下面是一等一SEO教程學(xué)習(xí)網(wǎng)總結(jié)了一些內(nèi)容,分享一下。在我們進行網(wǎng)站優(yōu)化時,總會出現(xiàn)些優(yōu)化過度而導(dǎo)致網(wǎng)站被降權(quán),甚至被K站。那么怎么才能知道自己是否網(wǎng)站優(yōu)化過度

2012-11-13 15:21:44

(用到了三角函數(shù))都比較消耗電機主控芯片的計算能力。在考慮算法實現(xiàn)的時候,都需要針對主控芯片的實際性能進行一定優(yōu)化,才能確保算法能夠順利運行。這里我總結(jié)下電機控制中對程序算法優(yōu)化的辦法。數(shù)據(jù)的概念浮點數(shù)

2021-08-27 06:37:05

hbase響應(yīng)速度;9. 避免出現(xiàn)region熱點現(xiàn)象,啟動按照table級別進行balance。以上是對HBase性能優(yōu)化方法的概要總結(jié),有HBase性能優(yōu)化需求的,可以在此基礎(chǔ)上延伸學(xué)習(xí),會有一定收獲的!

2018-04-20 17:16:47

LVGL優(yōu)化幀率的方法有哪幾種?

2022-02-10 07:48:51

怎樣去調(diào)試NuttX shell呢?NuttX shell的調(diào)試基本方法總結(jié)

2021-12-20 06:15:48

希望各位能幫我分析一下,為什么這優(yōu)化等級OZ,會導(dǎo)致程序一多就卡死的原因。或者是卡死在rt_schedule函數(shù)中,如何進行調(diào)試,判斷問題所在。

2022-09-07 11:25:52

?CPU 寄存器值,任務(wù)中局部變量,調(diào)用的函數(shù)參數(shù)和函數(shù)調(diào)用深度(使用迭代函數(shù)請慎重)。因此在進行任務(wù)堆棧分配時考慮到最糟糕情況就3. 任務(wù)間通訊4. 定時器總結(jié)一下。見下表。三. 優(yōu)化方法: 1.

2021-01-26 14:10:37

有人嗎?有沒有人使用STM32F745,通過FMC訪問FPGA,但是相鄰的訪問的操作的順序被優(yōu)化!

2020-04-15 01:05:15

,按照向?qū)砑有枰^察的信號。然后保存。再打開xdc文件,即可看到添加了ila約束。IV 生成bit文件,開始調(diào)試。這部分和方法1中類似,不再贅述。總結(jié):使用內(nèi)嵌邏輯分析儀有兩種方式,1是直接添加

2023-04-06 21:48:03

關(guān)于c6000系列的C代碼優(yōu)化總結(jié),在hellodsp上看到的好帖,拿來共享一下~~~

2011-08-03 15:24:16

rt-thread-OK1061-S 調(diào)試,KEIL優(yōu)化將原等級2改為等級0,進入HardFault_Handler,幫忙找下原因。

2022-01-12 06:36:14

能夠有一些時序問題,我們再通過時序分析的方法對它進行優(yōu)化。我們這里把原本的100M時鐘改成了200M時鐘,具體步驟如下: 一:更改時鐘之后進行綜合,并打開timing analysis 二:通過

2018-08-22 11:45:54

《MATLAB優(yōu)化算法案例分析與應(yīng)用》清華大學(xué)出版社《MATLAB優(yōu)化算法案例分析與應(yīng)用》這本書,給大家推薦一下這本書清華大學(xué)出版社《MATLAB優(yōu)化算法案例分析與應(yīng)用》這本書,給大家推薦一下這本書

2014-10-10 12:34:35

《現(xiàn)代CPU性能分析與優(yōu)化》是一本非常實用的書籍,對于從事性能關(guān)鍵型應(yīng)用程序開發(fā)和進行系統(tǒng)底層優(yōu)化的技術(shù)人員來說是不可或缺的。這本書也很適合任何想更好地了解應(yīng)用程序性能并探索其診斷和改進方法的開發(fā)者

2023-04-18 16:03:36

。

第11章討論多線程應(yīng)用程序的性能分析技巧,概要地描述多線程應(yīng)用程序性能優(yōu)化所要

在第一部分里介紹了與性能分析相關(guān)的內(nèi)容比如性能測量,分析方法等,還有CPU架構(gòu)的說明,如流水線等:

CPU利用率的介紹

2023-04-24 15:31:26

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應(yīng)等等,各種不同因素都在迅速推動系統(tǒng)設(shè)計人員關(guān)注節(jié)能問題。一項有關(guān)設(shè)計優(yōu)先考慮事項的最新調(diào)查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰(zhàn)。為什么要設(shè)計優(yōu)化FPGA功耗?

2019-08-08 07:39:45

本文闡述了Spartan-3 FPGA針對DSP而優(yōu)化的特性,并通過實現(xiàn)示例分析了它們在性能和成本上的優(yōu)勢。

2019-10-18 07:11:35

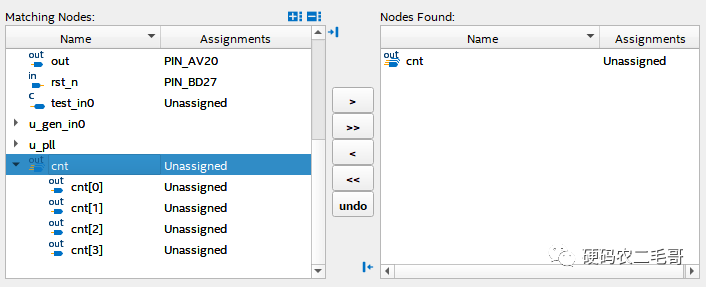

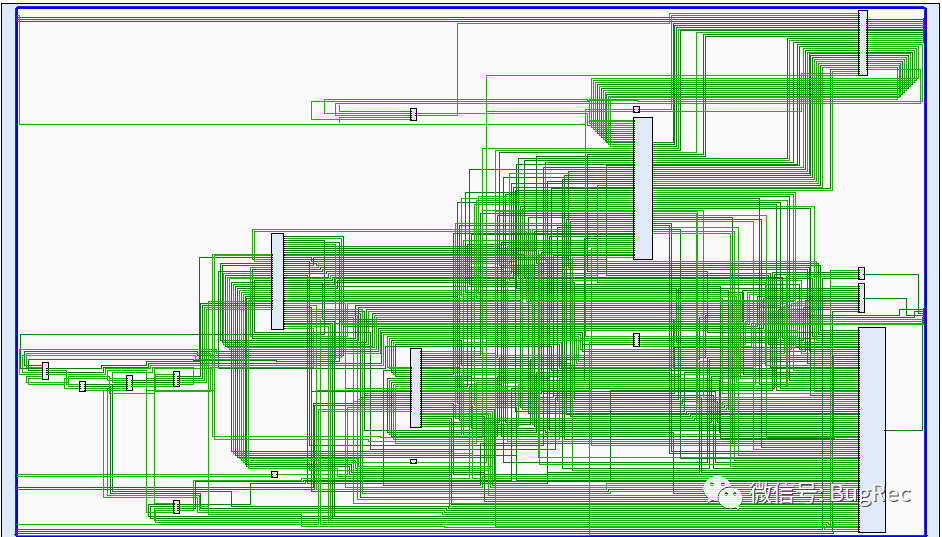

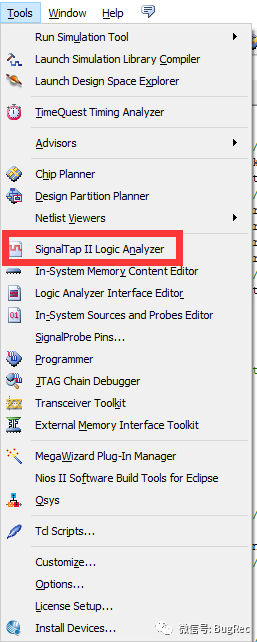

分析儀,可以幫助我們在線分析芯片內(nèi)部邏輯。而且操作簡單方便,但是往往因為某些原因,有些信號在綜合的時候就會被優(yōu)化掉,就可能會導(dǎo)致我們的設(shè)計失敗,當然在為邏輯分析儀添加觀察信號的時候也無法找到該信號

2023-05-16 17:48:23

代碼優(yōu)化的目的是什么?具體方法包括哪幾種?代碼優(yōu)化工作有什么創(chuàng)新點?

2021-06-03 06:17:31

數(shù)據(jù)中心。這一應(yīng)用模式的轉(zhuǎn)變需要具備快速擴展能力的計算節(jié)點來滿足視頻內(nèi)容制作和分發(fā)的各個不同高計算強度階段的需求,如轉(zhuǎn)碼需求和水印需求。

我們近期使用賽靈思SDAccel?開發(fā)環(huán)境來編譯和優(yōu)化專為FPGA

2019-06-19 07:27:40

)。方法2調(diào)試起來簡單,PLL設(shè)置簡單,出錯可能性小。通過不斷調(diào)整相位,最終肯定可以正確通信。缺點也明顯,接口一多,每個都要做隨路時鐘就浪費了。最近一直在做時序約束,總結(jié)一下時序約束過程。(1)根據(jù)時序

2016-09-13 21:58:50

的方法,都是需要我們慢慢的去挖掘在已有的基礎(chǔ)上面去拓展思維。東莞seo博客總結(jié),我們想要做好關(guān)鍵詞優(yōu)化排名,那么我們需要對于關(guān)鍵詞進行合理的布局和思考,運用以上為大家介紹的一些方法去實時的操作,還需要再

2019-08-11 01:19:18

,一般情況下,速度指標是首要的,在滿足速度要求的前提下,盡可能實現(xiàn)面積優(yōu)化。因此,本文結(jié)合在設(shè)計超聲探傷數(shù)據(jù)采集卡過程中的CPLD編程經(jīng)驗,提出串行設(shè)計、防止不必要鎖存器的產(chǎn)生、使用狀態(tài)機簡化電路描述、資源共享,利用E2PROM芯片節(jié)省片內(nèi)資源等方法對VHDL電路進行優(yōu)化。

2019-06-18 07:45:03

嵌入式Java虛擬機優(yōu)化技術(shù)總結(jié)的太棒了

2021-04-25 06:47:34

響應(yīng)運行。并且經(jīng)過實踐證明,嵌入式系統(tǒng)內(nèi)存優(yōu)化使用,能夠提升系統(tǒng)空間5%內(nèi)存,確保系統(tǒng)順利運行。【關(guān)鍵詞】 嵌入式 Linux系統(tǒng) 內(nèi)存優(yōu)化 使用方法研究現(xiàn)如今,嵌入式系統(tǒng)軟件被廣泛應(yīng)用于各行...

2021-11-04 06:23:46

電磁波等能量。微波天線是微波通信系統(tǒng)收發(fā)設(shè)備的“出入口”,天線性能直接影響整個系統(tǒng)的運行。目前關(guān)于微波天線優(yōu)化的研究成果雖然很多,但多數(shù)均是從單一因素進行考慮,優(yōu)化效果并不是非常理想,本文通過綜合考慮多種因素并優(yōu)化微波天線選擇參數(shù)來尋找更合理的選擇方法。

2019-06-11 07:25:18

目前關(guān)于微波天線優(yōu)化的研究成果雖然很多,但多數(shù)均是從單一因素進行考慮,優(yōu)化效果并不是非常理想,本文通過綜合考慮多種因素并優(yōu)化微波天線選擇參數(shù)來尋找更合理的選擇方法。

2021-05-26 06:04:03

混合信號測試錯誤的常見原因是什么?怎么對混合信號測試的開關(guān)系統(tǒng)進行優(yōu)化?

2021-05-10 07:02:47

”的方法。先將要觀察的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。然而當設(shè)計的復(fù)雜程度增加時,這個方法就不再適合了,其中有幾個原因。 &

2010-01-08 15:05:27

ifi給你科普如何優(yōu)化SPDIF數(shù)字信號,數(shù)字音頻信號差或者劣,這是大多數(shù)數(shù)碼產(chǎn)品存在的問題,而iPurifier SPDIF可達到優(yōu)化效果。我們的電腦機箱內(nèi)存在著嚴重的電磁波,D/A、A/D轉(zhuǎn)換

2016-08-16 11:04:18

有什么方法可以優(yōu)化自適應(yīng)轉(zhuǎn)向大燈系統(tǒng)的設(shè)計嗎?

2021-05-14 06:14:18

設(shè)計低功率電路同時實現(xiàn)可接受的性能是一個困難的任務(wù)。在 RF 頻段這么做更是迅猛地提高了挑戰(zhàn)性。今天,幾乎每一樣?xùn)|西都有無線連接能力,因此 RF 功率測量正在迅速變成必要功能。這篇文章著重介紹多種準確測量 RF 信號電平的有用方法,以優(yōu)化這些無線系統(tǒng)的性能。本文討論滿足各種不同應(yīng)用需求的優(yōu)化方法。

2019-07-22 07:53:11

`玩轉(zhuǎn)Zynq連載5——基于Vivado的在線板級調(diào)試概述 更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s Vivado在線調(diào)試概述FPGA的板級調(diào)試方法有很多

2019-05-24 15:16:32

電機優(yōu)化失敗的原因

2023-12-15 07:03:27

(用到了三角函數(shù))都比較消耗電機主控芯片的計算能力。在考慮算法實現(xiàn)的時候,都需要針對主控芯片的實際性能進行一定優(yōu)化,才能確保算法能夠順利運行。這里我總結(jié)下電機控制中對程序算法優(yōu)化的辦法。數(shù)據(jù)的概念...

2021-09-07 06:19:56

目錄一、電源優(yōu)化方法1.1 功能禁用1.2 動態(tài)功耗管理 (Dynamic Power Management)1.3 頻率縮放1.4 時鐘門控1.5 使用PL加速二、四大功耗域及PMU2.1 電池

2021-11-12 08:36:14

要求純硬件,防止電機堵轉(zhuǎn)電流過大,燒驅(qū)動。此電路有優(yōu)化的地方嗎?或者有更好的方案嗎?求大神指點。

2019-11-22 10:58:50

的,還能在一定程度上避免未知錯誤,常用的Java代碼優(yōu)化細節(jié)如下:1. 為類、方法指定final修飾符為類指定final修飾符可以讓類不可以被繼承,為方法指定final修飾符可以讓方法不可以被重寫,如果

2018-04-02 15:43:44

每一版本都提供了完整的FPGA設(shè)計流程,并且專門針對特定的用戶群體(工程師)和特定領(lǐng)域的設(shè)計方法及設(shè)計環(huán)境要求進行了優(yōu)化。那大家知道賽靈思ISE? 設(shè)計套件11.1版對FPGA有什么優(yōu)化作用嗎?

2019-07-30 06:52:50

FPGA怎么選擇?針對功耗和I/O而優(yōu)化的FPGA介紹

2021-05-06 09:20:34

干下來,發(fā)現(xiàn)方法總比困難多,有一種太極生兩儀,兩儀生四象,四象生八卦,八卦生萬物的趕腳。借用三十六計來總結(jié),一點也不夸張。怎么說呢?時序的本質(zhì)就是delay的控制,控制在setup和hold都滿足

2020-12-10 07:37:31

主要講解了fpga設(shè)計、方法和實現(xiàn)。這本書略去了不太必要的理論、推測未來的技術(shù)、過時工藝的細節(jié),用簡明、扼要的方式描述fpga中的關(guān)鍵技術(shù)。主要內(nèi)容包括:設(shè)計速度高、體積小、功耗低的體系結(jié)構(gòu)方法

2012-03-01 14:59:23

和遠端串擾這種方法來研究多線間串擾問題。利用Hyperlynx,主要分析串擾對高速信號傳輸模型的侵害作用并根據(jù)仿真結(jié)果,獲得了最佳的解決辦法,優(yōu)化設(shè)計目標。【關(guān)鍵詞】:信號完整性;;反射;;串擾;;近

2010-05-13 09:10:07

本文主要講述的是單片機的在線調(diào)試方法。

2009-04-22 16:43:23 33

33 GPRS優(yōu)化思路總結(jié)報告:一、概述 2二、無線優(yōu)化的思路 2三、(E)GPRS網(wǎng)絡(luò)資源容量分析優(yōu)化 53.1、(E)GPRS網(wǎng)絡(luò)拓撲結(jié)構(gòu) 63.2、GB口分析優(yōu)化 63.3、ABIS口分析

2009-07-27 21:29:34 26

26 摘要:自20 世紀30 年代起,水利規(guī)劃科學(xué)成為人類極為關(guān)注的研究課題之一,而其中計算優(yōu)化方 法則是水利規(guī)劃實踐中經(jīng)常遇到的難點。文章介紹了不同時期水利規(guī)劃中的優(yōu)化方法,分析了不同優(yōu)化 方法的優(yōu)點和適用范圍,并對新興的優(yōu)化智能算法進行了分析介紹。

2011-02-23 16:03:07 0

0 本文提出了一種基于SoPC的FPGA在線測試方法,是對現(xiàn)有FPGA在線測試方法的一種有效的補充。

2011-04-18 11:46:20 1145

1145

文中應(yīng)用電磁場全波仿真工具SIwave構(gòu)建信號跨層走線模型,從電源分配網(wǎng)絡(luò)(PDN)阻抗的角度分析了跨層走線對信號傳輸?shù)挠绊?同時使用添加電容的方法優(yōu)化信號傳輸路徑,并對電容的選取及

2012-02-29 14:25:25 5

5 提出了基于關(guān)系代數(shù)樹結(jié)構(gòu)的SQL查詢優(yōu)化策略。利用改進查詢計劃的代數(shù)定律,分析基于關(guān)系代數(shù)樹的關(guān)系代數(shù)式查詢優(yōu)化方法、研究關(guān)系代數(shù)表達式與SQL查詢的等價變換準則、分析關(guān)

2012-05-07 10:11:17 21

21 基于FPGA的可堆疊存儲陣列設(shè)計與優(yōu)化

2017-01-07 21:28:58 0

0 WCDMA網(wǎng)絡(luò)RF優(yōu)化方法及案例分析

2017-01-12 22:04:03 11

11 磁流變液阻尼器的磁路有限元分析與優(yōu)化設(shè)計方法

2017-01-21 12:12:16 1

1 DSP在線升級與資源優(yōu)化再配置

2017-10-20 09:53:27 5

5 DSP程序優(yōu)化總結(jié)

2017-10-23 14:24:03 2

2 低頻振蕩是影響互聯(lián)電網(wǎng)安全穩(wěn)定運行的突出問題,提高系統(tǒng)阻尼是防止區(qū)間低頻振蕩最有效的措施。本文提出了一種基于遺傳算法的優(yōu)化機組有功出力的方法,通過在線模態(tài)分析,優(yōu)化調(diào)整后的機組有功出力提高了最弱阻尼

2017-11-09 10:42:09 6

6 資源、速度和功耗是FPGA設(shè)計中的三大關(guān)鍵因素。隨著工藝水平的發(fā)展和系統(tǒng)性能的提升,低功耗成為一些產(chǎn)品的目標之一。功耗也隨之受到越來越多的系統(tǒng)工程師和FPGA工程師的關(guān)注。Xilinx新一代開發(fā)工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優(yōu)化。

2017-11-18 03:11:50 4873

4873 現(xiàn)有的工具和技術(shù)可幫助您有效地實現(xiàn)時序性能目標。當您的FPGA 設(shè)計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現(xiàn)工具為滿足時序要求而優(yōu)化設(shè)計的能力,還取決于設(shè)計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2951

2951 ,在算法層提出了數(shù)學(xué)模型優(yōu)化、軟件模型優(yōu)化和循環(huán)算法優(yōu)化等方法,在語法層提出了指針使用和嵌入函數(shù)等優(yōu)化方法,具有較強的問題針對性,對其它領(lǐng)域的信號級仿真也具有參考價值。

2018-01-02 16:19:58 0

0 摘要: 分析了目前我國網(wǎng)絡(luò)測試和優(yōu)化方面的現(xiàn)狀,提出了面向用戶感知的測試和分析系統(tǒng)平臺架構(gòu),對面向用戶感知的網(wǎng)絡(luò)優(yōu)化方法進行了總結(jié),并對未來我國網(wǎng)絡(luò)優(yōu)化的實施提出了策略建議。 1 我國網(wǎng)絡(luò)測試和優(yōu)化

2018-01-19 01:37:16 535

535 本文檔內(nèi)容介紹了基于chipscope使用教程以及FPGA在線調(diào)試的方法,供參考

2018-03-02 14:09:49 9

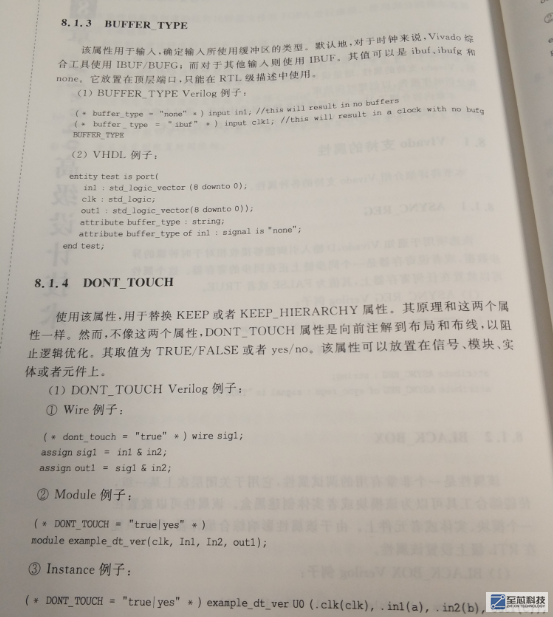

9 = “{TRUE|FALSE |SOFT}” *),可以防止信號被綜合掉,但是無法防止在布局布線的時候優(yōu)化掉。3、 信號前面使用(* DONT_TOUCH= “{TRUE|FALSE}” *),可以防止信號

2018-06-01 16:59:43 12364

12364

= “{TRUE|FALSE |SOFT}” *),可以防止信號被綜合掉,但是無法防止在布局布線的時候優(yōu)化掉。3、 信號前面使用(* DONT_TOUCH= “{TRUE|FALSE}” *),可以防止信號

2018-10-09 15:22:43 5407

5407 高層次的設(shè)計可以讓設(shè)計以更簡潔的方法捕捉,從而讓錯誤更少,調(diào)試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復(fù)雜的 FPGA 設(shè)計上實現(xiàn)高性能,往往需要手動優(yōu)化 RTL 代碼,這也意味著

2018-12-16 11:19:28 1435

1435

信號銷任務(wù)之間可以自動優(yōu)化PCB上的多個fpga同時尊重pin-specific規(guī)則和約束。減少路由層,減少跨界車和整體跟蹤PCB上的長度,并減少信號完整性問題較高的畢業(yè)率和更短的FPGA路線時間。

2019-10-14 07:06:00 2849

2849 FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設(shè)計流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測試設(shè)備■使用 FPGAVIEW改善外部測試設(shè)備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 9

9 在線調(diào)試也稱作板級調(diào)試,它是將工程下載到FPGA芯片上后分析代碼運行的情況。

2020-11-01 10:00:49 3948

3948

本文檔的主要內(nèi)容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現(xiàn)優(yōu)化設(shè)計。

2021-01-13 17:00:59 25

25 本文檔的主要內(nèi)容詳細介紹的是FPGA的時序分析的優(yōu)化策略詳細說明。

2021-01-14 16:03:59 17

17 本文檔的主要內(nèi)容詳細介紹的是FPGA的時序分析的優(yōu)化策略詳細說明。

2021-01-14 16:03:59 19

19 DC-DC電源系統(tǒng)的優(yōu)化設(shè)計總結(jié)(電源技術(shù)期刊咋樣)-該文檔為DC-DC電源系統(tǒng)的優(yōu)化設(shè)計總結(jié)文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-22 11:45:17 26

26 Xilinx被AMD收購的事情把我震出來了,看了看上上一篇文章講了下仿真的文件操作,這篇隔了很久遠,不知道該從何講起,就說說FPGA的在線調(diào)試的一些簡單的操作方法總結(jié)。

2023-06-19 15:52:21 1225

1225

之前的文章介紹了FPGA在線調(diào)試的方法,包括選定抓取信號,防止信號被優(yōu)化的方法等等。

2023-06-20 10:38:48 3333

3333

在項目初期,在使用FPGA工具quartus或者vivado生成版本燒入開發(fā)板進行調(diào)試時(DC開啟優(yōu)化選項后同樣會優(yōu)化掉寄存器),我們有時會發(fā)現(xiàn)部分寄存器被優(yōu)化掉了,今天簡單聊聊被優(yōu)化的幾種情況。

2023-09-26 09:47:49 455

455

的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。然而當設(shè)計的復(fù)雜程度增加時,這個方法就不再適合了,其中有幾個原因。第一是由于FPGA的功能增加了,而器件的引腳數(shù)目卻緩慢地增長。因此,可用邏輯對I/O的比率減小了,參見圖1。此外,設(shè)計很復(fù)雜時

2023-12-20 13:35:01 147

147

電子發(fā)燒友App

電子發(fā)燒友App

評論