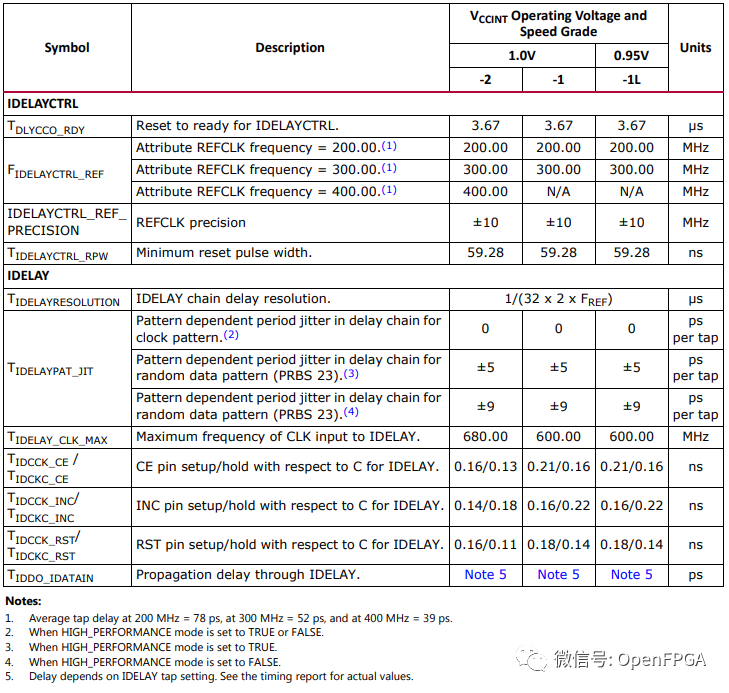

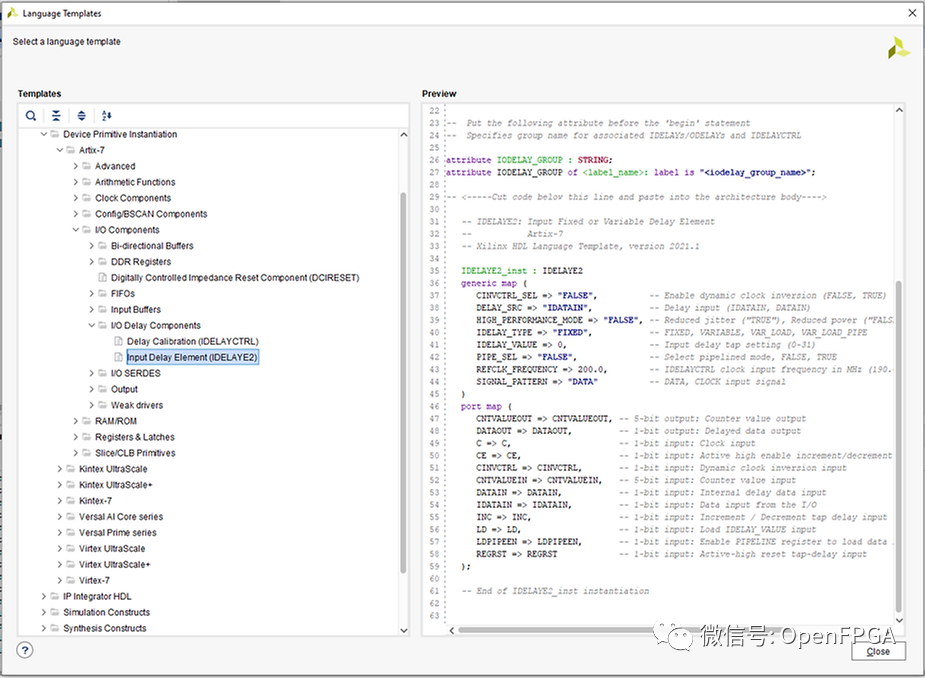

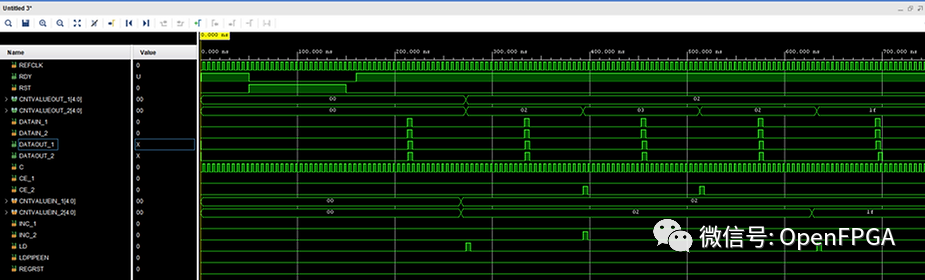

idelay2中按推薦配置,從DATAIN還是從IDATAIN輸入區別為是內部延時還是從IO輸入,FIXED固定延時,idelay value先輸入0,,時鐘是200M,其他全部接0。

2020-11-25 14:35:49 9912

9912 ,FPGA生成并向8個攝像機發送26.66MHz時鐘,每個攝像機返回320MHz的時鐘和12位SDR數據。從轉發的26.66MHz時鐘生成320MHz時鐘并將其用于ISERDES(在所有通道上)應該是

2020-07-24 12:10:42

我有2個時鐘輸入通過一個支持時鐘的IO對(AN19和AN20)進入FPGA。時鐘輸入具有相同的頻率,但不同相。是否可以通過他們自己的IODELAY和BUFIO來分配每個本地時鐘網絡?我希望一個時鐘

2020-05-29 15:52:06

嗨,我正在嘗試使用KC705板進行PCIE RC和端點測試。1)我將把PCIE RC控制器IP設計和FPGA PCIE PHY放在FPGA中。2)我將在FPGA中放置另一個PCIE端點控制器IP

2020-07-26 13:06:25

貨真價實XILINX、ALTERA 一系列2手FPGA,我們真實庫存,貨真價實。可提供檢測。實驗,應用等需求。Q 3618704432淘世宇電子

2019-07-28 17:40:08

。 NIOS2這種軟核cpu思路很新穎 廢物利用網表中閑置的邏輯門 就可以讓FPGA平白無故就多了一塊強大的控制器 而不用外接一個mcu。 但FPGA功耗/個頭較大 更適合一些設計原型的開發中 或是對尺寸

2018-08-17 09:59:27

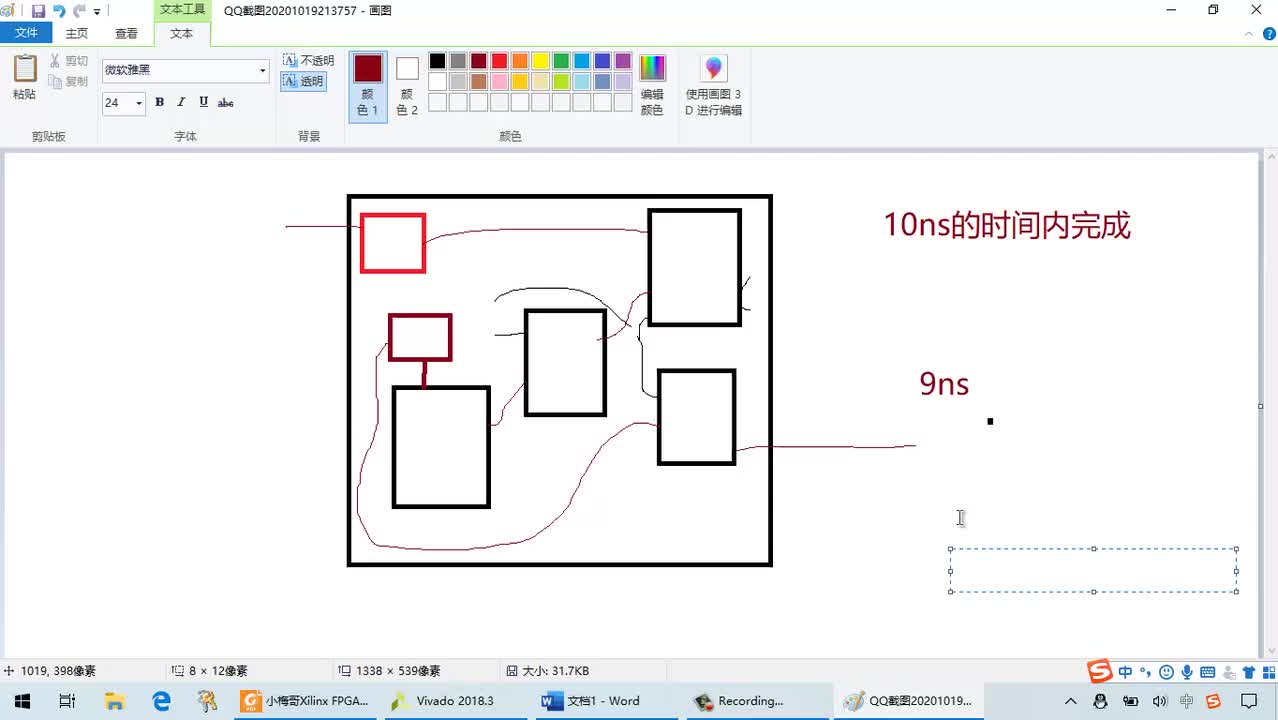

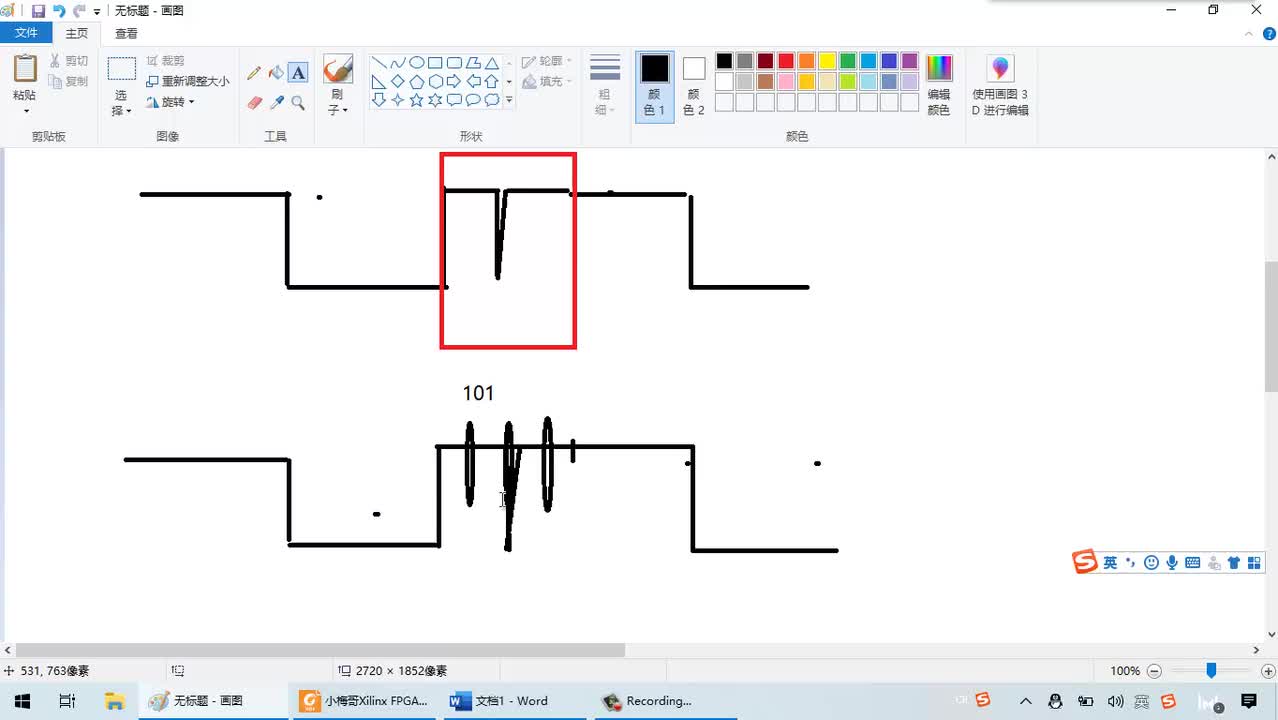

基本的時序分析理論2本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們再來看一個例子,如圖8.2所示

2015-07-14 11:06:10

FPGA開發全攻略(全,分為上下2部)

2019-03-25 14:44:29

大家好我FPGA應用需要用到8GDDR,目前采用2片4GDDR2,發現一個有趣問題,美光,2GDDR2支持16位,速率可達200M,但美光4G的DDR2只有8位,速率才125M~150MHz。怎么會慢呢?有沒有更快的?

2013-06-22 22:02:28

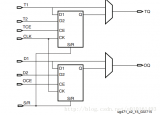

是 IDELAY2 和 ODELAY2 原語。這些原語為開發人員提供了一個由 32 個抽頭組成的可編程延遲線,可提供可調節或固定的延遲。實際可用的原語取決于我們正在使用的 IO bank 的類型。High

2022-10-12 14:19:39

嗨,我使用的是Kintex 7(325,-2速度等級)。我想在VAR_LOAD模式下使用ODELAY并非常頻繁地更改抽頭值。我看到ODELAY上的最大時鐘速度為800MHz的數據表,但我沒有看到

2020-08-25 15:48:58

fpga應用篇(四):binary2bcd在實際中,我們常常需要將數據通過數碼管或者LCD顯示出來,例如,我們要將224顯示到數碼管上,我們要做的事就是分別提取出2,2,4這三個數字,然后分別送到

2017-04-10 18:04:37

嗨,大家好 *我在主串行模式下使用spartan-3e fpga和XCFxxS Prom。*對于fpga開始初始化,必須進行2次進行: 1)通電良好(正常工作), 2)引腳prog_B必須為高電平

2019-05-07 10:31:43

我的基本配置如下:1.SYNC信號連接至FPGA io口,并配置該IO口高電平輸出2.ADC沒有外接晶振,使用的內部晶振,并且內部晶振沒有配置輸出3.SCLK信號通過FPGA晶振分頻得到,頻率為

2019-01-30 11:24:43

MPS2和MPS2+FPGA原型板是ARM Cortex-M評估和開發的開發平臺。

MPS2和MPS2+FPGA原型板提供以下功能:

Altera Cyclone FPGA和主板上電和配置MPS2

2023-08-18 07:25:28

`BPI-F2S 嵌入式和FPGA教育套件是一套基于凌陽7021 SOC的單片機高度集成的開發平臺。具有高性能、低功耗的特點;嵌入式Linux嵌入式系統,適用于語音圖像處理、通信、便攜式工業控制設備

2020-04-26 14:51:09

_VALUE => 0, IDELAY2_VALUE => 0, IDELAY_MODE =>“正常”, ODELAY_VALUE => 0, IDELAY_TYPE =>

2018-10-11 14:52:33

我有興趣在IDDR2和ODDR2前面使用一個IODELAY2作為Spartan 6上60MHz DDR接口的一部分。但我對一些屬性和端口感到困惑。對于IDELAY_TYPE:不管您將其設置

2019-07-25 13:49:13

使用高云?半導體 GW2A/GW2AR 系列 FPGA 產品做電路板設計時需遵循一系列規則。本文檔詳細描述了 GW2A/GW2AR 系列 FPGA 產品相關的一些器件特性和特殊用法,并給出校對表用于

2022-09-29 06:32:25

GW2ANR 系列 FPGA 產品數據手冊主要包括高云半導體 GW2ANR 系列 FPGA 產品特性概述、產品資源信息、內部結構介紹、電氣特性、編程接口時序以及器件訂貨信息,幫助用戶快速了解高云半導體 GW2ANR 系列FPGA 產品以及特性,有助于器件選型及使用。

2022-09-29 06:13:24

GW2AR 系列 FPGA 產品數據手冊主要包括高云半導體 GW2AR 系列FPGA 產品特性概述、產品資源信息、內部結構介紹、電氣特性、編程接口時序以及器件訂貨信息,幫助用戶快速了解高云半導體 GW2AR 系列FPGA 產品以及特性,有助于器件選型及使用。

2022-09-29 06:59:13

GW2A 系列 FPGA 產品數據手冊主要包括高云半導體 GW2A 系列FPGA 產品特性概述、產品資源信息、內部結構介紹、電氣特性、編程接口時序以及器件訂貨信息,幫助用戶快速了解高云半導體 GW2A 系列 FPGA產品特性,有助于器件選型及使用。

2022-09-29 06:37:08

使用我剛剛放入的ODELAY組件從DRC引擎獲得以下錯誤:錯誤:[DRC 23-20]規則違規(PLOD-1)ODELAY檢查3.3 V標準 - 端子p1750_hclk具有3.3 V標準,但連接到ODELAY。此組合無法清除。我在哪里可以找到有效的組合?TomT ...

2020-08-28 13:10:52

- >(到FPGA邏輯) | 時鐘數據iddrdata - > ibufds - > idelay - > iddr - >(到FPGA邏輯)1 - 大多數情況下,我

2020-06-18 07:36:38

你好我最近購買了帶有DDR SDRAM的FPGA Mimas V2 Spartan 6 FPGA開發板。我正在使用xilinx ise 14.7,verilog代碼,當使用工

2019-08-08 09:44:18

喜我有一個設計,我連接了2個FPGA- 一個vlx75T(發送125MHz clk和txdata)到vlx760 FPGA。并且vlx760 FPGA在由vlx75生成的相同clk處將數據

2019-04-08 10:27:05

敬啟者!在“Spartan-6 FPGA數據手冊:DC amd開關特性”之后,IODELAY2元件Spartan6的最大延遲定義為:最大延遲=整數(抽頭數/ 8)X Ttap8 + Ttapn。因此

2019-05-30 10:27:55

從光盤上拷下來的,Xilinx FPGA2 pro使用說明,想要的拿去吧

2013-10-24 10:14:16

7A100,lvds經過idelay2,使用2個iserdes2級聯后輸出1:10。在idelay2掃描tap時,后面的iserdes輸出的數據發生對齊錯誤,發現其中iserdes2(master

2023-05-09 11:23:05

ps2_keyboardfpga

2012-08-12 15:56:04

DDR2電路設計在高速大數據的應用中,高速大容量緩存是必不可少的硬件。當前在FPGA系統中使用較為廣泛的高速大容量存儲器有經典速度較低的單數據速率的SDRAM存儲器,以及速度較高的雙速率DDR

2016-12-30 20:05:09

IODELAY2,以便可以將其校準為HALF_MAX。以下是主IODELAY2的配置: DATA_RATE =>“DDR”,IDELAY_MODE =>“正常”,SERDES_MODE

2019-06-26 07:14:40

大家好,我有一個使用Artix7 200部件的大型設計,該設計有超過100個輸入,使用IDELAY2跨越8個庫,根據這里的建議,我只需要為整個設計實例化1個IDELAYCTRL,我已經完成了它工作

2020-08-10 06:36:18

嗨!我正在試驗用作解串器的Spartan-6。我無法100%無錯誤,所以不幸的是我需要更仔細地分析我的代碼的行為(以及我在那里使用的原語:ISERDES,ODELAY2和校準機制 - 也許他們給了我

2019-07-24 06:17:58

`例說FPGA連載74:FX2與FPGA之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例有4個工程,一個8051 MCU

2017-02-17 10:24:06

`例說FPGA連載75:FX2與FPGA之SignalTap II與功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc FPGA

2017-02-19 20:28:01

`例說FPGA連載2:FPGA是什么特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc2015年伊始,Intel欲出資百億美金收購

2016-06-23 16:04:27

FX2是不是類似于一個仿真器,內部的固件程序在下載FPGA程序時模擬JTAG協議將程序下進去嗎,這時是不是工作在主模式下;還有上位機通過FX2與FPGA通信時是不是工作在被動模式下, 主動模式和被動模式的切換是通過什么來實現的?

2018-05-09 14:14:44

嗨,我在Kintex7上運行。我(我承認)我正在測試的ODELAY2原語的一個不尋常的應用程序。行為模擬表明設計應該有效,但實際上并非如此。我已經在硬件管理器中監視了盡可能多的信號,除了

2020-08-28 07:14:42

] .idelaye2_bus:mb_subsystem_pre_idelay_0_group''mb_subsystem_i / pre_idelay / inst / pins [0] .idelaye2

2018-11-08 11:29:47

_TYPE => "VAR_LOADABLE",IDELAY_VALUE => 0,ODELAY_TYPE => "VAR_LOADABLE"

2018-10-11 14:53:18

基于FPGA和AD1836的I2S接口該如何去設計?

2021-05-26 06:45:37

`積分商城兌換的禮品《基于FPGA的數字信號處理(第2版)》曬曬,:-)`

2016-03-28 23:53:15

Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產的型號為MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM為存儲器。用一個IP核完成

2011-05-03 11:31:09

我在sp601板上使用tri-ethernet-mac示例。gmii接收器接口使用IODELAY2原語來延遲接收器側的輸入信號。vhdl代碼提到應該根據設計在ucf中更改IDELAY_VALUE。我

2019-05-28 06:40:20

海, 我的電路板由2個Kintex-7 fpga和兩個獨立的BPI閃光燈(微米級閃光燈)組成。如何使用單JTAG連接器(菊花鏈)progaram 2 fpga?theertha

2020-05-29 13:47:54

你好根據我的要求,我需要在一個IOB上使用2 odelay。我需要延遲這兩個信號“ts_dqs”和“out_dqs”,如下所示。u_iobuf_dqs(.I(out_dqs),//來自FPGA .T

2020-07-14 10:59:46

”),. IDELAY_TYPE(“VAR_LOADABLE”),. IDELAY_VALUE(0),. REFCLK_FREQUENCY(200.0),. SIGIG_PATTERN(“DATA”))ODELAY

2020-06-13 06:54:13

是 IDELAY2 和 ODELAY2 原語。這些原語為開發人員提供了一個由 32 個抽頭組成的可編程延遲線,可提供可調節或固定的延遲。實際可用的原語取決于我們正在使用的 IO bank 的類型。High

2022-10-09 16:00:19

大家好,我正在使用IDELAY原語來實現DDR的DQ和DQS延遲。這是我的代碼:IOBUF pad_xb_dq7(.O(bus_data_in_flh [7]),. IO(xb_dq [7

2020-06-01 16:57:41

我有一些源同步系統,它可以在8條線路上為FPGA提供DDR數據。時鐘頻率在> 500 MHz范圍內。我知道我需要使用ISERDES和IDELAY來正確捕獲這些數據。 8 ISERDES提供64

2019-04-15 14:18:39

我閱讀了UG381第71頁,DS162第47頁以及該主板上的各種主題,以幫助我了解如何正確配置抽頭延遲。我使用Spartan 6 IODELAY2塊來恒定數據總線的ODELAY,以滿足下游CPU

2019-07-17 08:47:54

您好!我有FPGA Cyvon和FX2LPB開發板。在我的項目中,我需要將流數據從FPGA發送到FX2LP,我使用流IVHDL代碼FROMAN61345項目和非周期化PLL,DDR和引腳分配為

2019-10-22 10:37:10

你好,我正在使用MCB連接fpga到DDR2內存。我可以從fpga端寫入內存,但是當我嘗試閱讀它時。數據沒有出現。有沒有辦法查看加載到內存中的數據。我正在使用模擬模型,但似乎沒有任何幫助。如果有

2019-05-27 13:52:30

怎么實現基于FPGA視頻采集中的I2C總線設計?

2021-06-03 06:51:15

Input3Input4Input8Input16Input32output信號Output1Output2Output3Output4Output8Output16Output32要使用上面快捷命令,需要明德揚的配置文件,歡迎關注明德揚公眾號“fpga520”,或群544453837索取。口號:多用模板,減少記憶,專注設計!

2017-11-29 15:19:11

DDR2控制和FPGA實現

2015-07-21 19:28:14

我的開發板是XEVMK2LX,板上使用的XC3S400 FPGA來控制編程CDCM6208,我需要FPGA的源程序,請問從哪里可以下載到?

2018-06-21 05:37:37

各位大哥大姐求一個 基于FPGA的PS/2鼠標接口的設計與實現的程序設計可有償~~~~聯系qq392404578

2016-05-11 14:17:48

` 本帖最后由 rousong1989 于 2015-6-11 13:17 編輯

特權同學FPGA搶樓贈書第2波活動規則:獲得贈書必須符合以下所有的條件:1.回復本帖報名。2.回復《特權

2015-05-31 20:41:07

嗨,各位,我正在與FX3S進行圖像流傳輸。是為FLIGIN模式的16位GPIF2設計器工作的FPGASTER Verilog代碼,請提供給我感謝和最好的關心 以上來自于百度翻譯 以下為原文Hi

2018-11-26 15:49:06

你好,世界,在我的設計中,我將有2個FPGA:Virtex 5和Virtex 6。FPGA將使用ACE文件從COMPACT FLASH配置。我是否必須在1中混合2個ACE文件,或者每個FPGA都有一

2019-01-18 08:50:08

”= PERIOD“Sysclk”16 ns HIGH 50%;OFFSET = IN 5 ns有效16 ns在“Sysclk”之前;我的問題是:Virtex5 FPGA如何通過路由資源,IDELAY或其他方式實現5 ns延遲?謝謝。克里斯

2020-06-13 19:23:05

下方法約束IDELAYE2實例時:set_property LOC IDELAY_X0Y48 [get_cells system_i / adc_8lvds_0 / inst / lvds0

2020-08-18 08:28:10

IDELAYE2提供數據,IDELAY2為GBUF提供數據。時鐘頻率為335 MHz。 IDELAY參考時鐘頻率為300 MHz。任何可能出錯的想法都可以解決這個問題嗎?PN是XC7VX485T-2FFG1157C。 - 保羅塔多尼奧

2020-07-15 06:06:24

親愛的先生/女士,請建議我使用Xilinx FPGA完全替代smartfusion2 FPGA。我們希望在我們的新設計中用Xilinx等效FPGA取代smartfusion(M2

2019-04-29 10:13:39

mode是指由Column和Row I/O混合。從表1中可以看出,Cyclone III只有6系列的FPGA在Top和Bottom BANK才支持200MHz頻率的DDR2。為了滿足設計要求,我們將4片

2019-05-31 05:00:05

NVIDIA DGX-2

2021-11-22 09:26:58

微信公眾號《FPGA2嵌入式》原創文章

2021-11-22 09:26:58

斑梨電子FPGA CycloneII EP2C5T144 學習板 開發板產品參數1. 采用ALTERA公司的CyclonellEP2C5T144芯片作為核心最小系統,將FPGA

2023-02-03 15:14:29

上千M。使用lvds來接收高速ADC產生的數據會很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR這種資源在FPGA的IOB中多得是(每個IO都對應有,最后具體介紹),根本不擔心使用。

2018-06-30 10:23:00 21423

21423

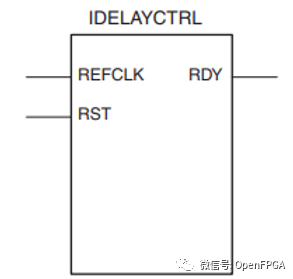

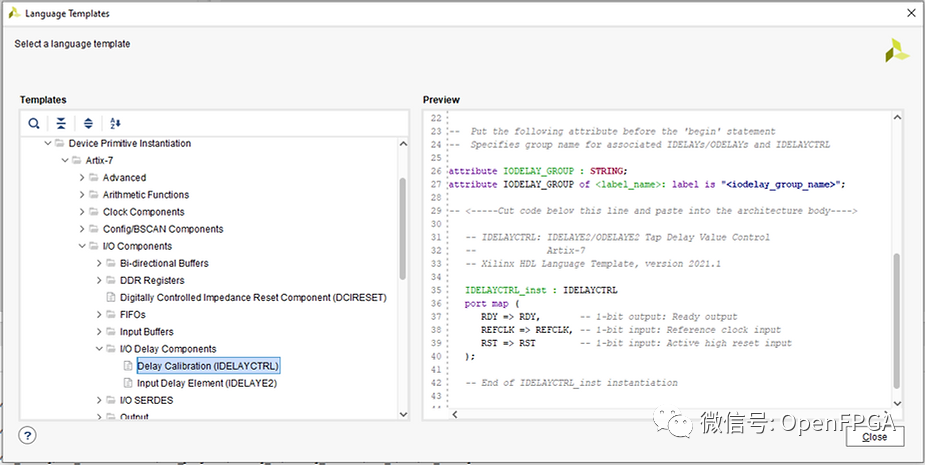

同樣,為了減小相同參考時鐘下Idelay2與IDELAYCTRL 的FPGA內部走線延時,必須使用IODELAY_GROUP將它們綁定在一起,使用方法參考上面的做法。

2022-08-20 10:50:23 3575

3575

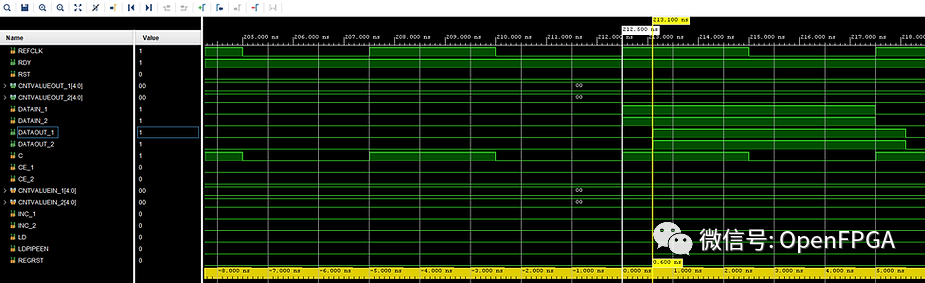

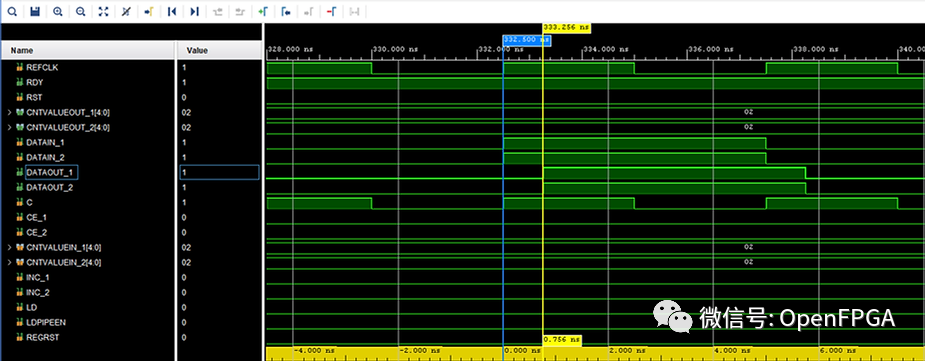

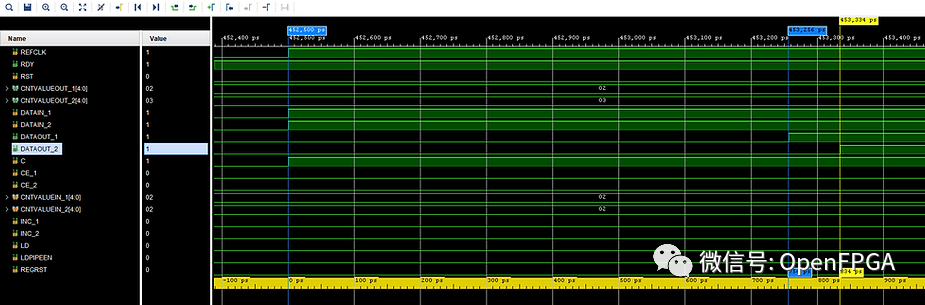

最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 1597

1597

電子發燒友App

電子發燒友App

評論