IP核可以兩種形式提供給客戶:軟核和硬核。兩種方式都可使客戶獲得在功能上經(jīng)過驗證的設計。軟核也被稱為可綜合內(nèi)核,需要由客戶進行綜合并在其SoC上實現(xiàn)。而硬核已完全實現(xiàn)(完成了版圖設計),可直接用于制造。(從技術上說,一種設計只有生產(chǎn)后才能實現(xiàn)。但是在此情況下,實現(xiàn)的意思是指安排布局并可直接投入生產(chǎn))。SoC團隊只需將硬核像一個單片集成電路片那樣置入芯片即可。軟核和硬核具有不同的問題和好處。

將IP核整合到一個芯片上需要很多步驟。這個過程是否能夠很容易地完成,主要取決于提供的交付成果。另外,客戶不僅必須對IP核進行評估,而且還要評估IP提供商。

軟核與硬核的對比

1. 性能

由于軟核沒有實現(xiàn),因此它天生在功能和實現(xiàn)方面比硬核更加靈活。另一方面,硬核開發(fā)者可能要花更多的時間來優(yōu)化他們的硬核,因為它們要在很多設計中使用。因此,這使人們覺得硬核會提供更高的性能。

事實上,為那些最先進工藝設計的高端、全定制硬核確實能夠提供比軟核更好的性能。通過使用鎖存、動態(tài)邏輯、三態(tài)信號、定制存儲器等,全定制設計團隊能實現(xiàn)比完全靜態(tài)綜合的設計更好的結果。對于需要達到現(xiàn)有工藝和設計技術極限性能的SoC來說,全定制硬核能夠更好地滿足這些要求。

然而,如果性能目標在一個軟核范圍內(nèi),那么硬核的優(yōu)勢就無關緊要了。SoC設計團隊能夠使用軟核來滿足性能要求,并利用其固有的靈活性優(yōu)勢。而隨著工藝技術的進步,軟核的最高頻率限制也在提高,使它們成為更多SoC設計師的一種選擇。在較低時鐘頻率下,硬核或許具有硅片面積方面的優(yōu)勢。但是情況往往并不是這樣。硬核經(jīng)常簡單地使用ASIC的方法進行固化,使之不能提供速度上的優(yōu)勢。在其他情況下,全定制內(nèi)核不能根據(jù)每一代工藝進行重新優(yōu)化,所以削弱了頻率和尺寸上的優(yōu)勢。

2. 技術獨立和可移植性

軟核的優(yōu)勢之一是技術獨立的,也就是說,Verilog或VHDL不需要使用一種特定的工藝技術或標準的單元庫。這意味著同一個IP核能夠應用到多種設計中,或現(xiàn)有設計的下一代中。一些軟核提供商采用使其內(nèi)核技術上非獨立的設計風格,但是這種方式看不到什么優(yōu)勢。

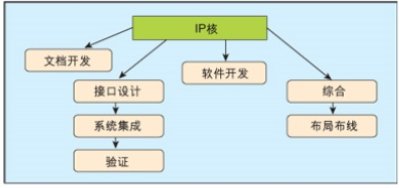

圖1:受IP核影響的開發(fā)任務。

另一方面,硬核在技術上是非常特定的。事實上,如果代工廠改變其工藝參數(shù)或庫,硬核可能就無法正常工作。這就產(chǎn)生了一個風險,因為在工藝參數(shù)改變時,IP提供商需要重新對硬核進行驗證。

硬核能夠移植到新的工藝技術,但是重新優(yōu)化全定制內(nèi)核的工作既費事又昂貴。對于一些先進的微處理器內(nèi)核,這可能要花兩年或更長的時間。因此,硬核經(jīng)常根據(jù)新的工藝進行光學調(diào)整。雖然這一方法既簡單又快速,但是它減少了由設計團隊針對現(xiàn)有工藝進行全定制優(yōu)化的許多優(yōu)勢。

不僅如此,光學調(diào)整同時帶來了另一個風險,因為它只能保證新的設計滿足設計規(guī)則,而不能保證準確的時序或功能,而且重新全面驗證經(jīng)過光學調(diào)整的IP核是非常困難的。

3. 速度/面積/功率優(yōu)化

對于要實現(xiàn)的技術來說,硬核通常比可比較的軟核運行速度更快。但是即使對于這單種技術來說,硬核也僅僅是針對一組目標而優(yōu)化。如果目標是在合理的性能上使芯片面積更小,那么對于這種應用來說,為高度可調(diào)性能而優(yōu)化的硬核可能就太大了。

軟核是能夠被“應用優(yōu)化”的。為適合特定的嵌入式SoC設計,時序、面積和功率目標可能需要進行調(diào)整。例如:如果SoC使用200MHz的時鐘,那么設計運行在250MHz的軟IP內(nèi)核可以改為準確地運行在200MHz上。這在得到更小尺寸和更低功率的同時滿足了設計約束。

這種應用優(yōu)化也適用于低層IO時序。軟內(nèi)核的IO約束可以進行調(diào)整,以準確配合內(nèi)核的使用環(huán)境。如果硬內(nèi)核有延遲輸出信號,SoC設計師幾乎無法改善時序。

如果SoC的速度、面積和功率目標與硬核的目標相符,那么硬核將極具競爭力。但對于大多數(shù)設計師來說,軟核在為特定的SoC優(yōu)化方面更具優(yōu)勢。

4. 可定制性

軟核相對硬核還具有另外一個優(yōu)勢:編譯時間定制化。這些是實現(xiàn)之前的設計選項。

高速緩沖存儲器的內(nèi)存大小就是一種常見的編譯時間用戶定制項目。根據(jù)特定嵌入式應用所需的高速緩沖存儲器的大小,軟核處理器能夠精確地被配置。而硬核在這方面就不能被定制。

另一種在許多軟核中應用的定制項目就是指令專用,或選擇性支持某種特殊指令。例如,一些SoC可能需要對外部協(xié)處理器的支持。然而,在一些不使用這些特性的系統(tǒng)中,多余的硬件可從軟核中去掉,以節(jié)省面積和功率。

軟核還可以包括實現(xiàn)配置參數(shù)。這是一種特殊的編譯時間定制,可幫助軟核更好地配合SoC團隊使用的設計風格。例如,微處理器內(nèi)核經(jīng)常通過使用門控時鐘電路來實現(xiàn),但這種時鐘不能與某些時鐘布線工具很好配合。如果處理器內(nèi)核可提供一種將所有門控時鐘變?yōu)橄嗟鹊?a href="http://www.asorrir.com/tags/多路復用器/" target="_blank">多路復用器(MUX)的編譯時間設置,SoC團隊可使實現(xiàn)更為容易。

5. 易于集成

軟核很可能更容易被集成到SoC設計團隊使用的流程中,除非內(nèi)部設計小組已經(jīng)實現(xiàn)了硬核。其原因是SoC設計團隊將在他們認可的IP核周圍添加RTL模塊。這些內(nèi)核看上去就像另外的SoC模塊,也可像它們一樣地實現(xiàn)。

另一方面,硬核看上去更像一個黑匣子RAM,特別是在它采用全定制技術實現(xiàn)時。這意味著硬核提供商將需要為該內(nèi)核提供更多的黑匣子模型,使SoC設計師能夠在其周圍設計其模塊。這本身就比使用軟核更困難。例如,全定制硬核也許沒有門級網(wǎng)表。這是因為該設計已經(jīng)在晶體管級完成,而沒有使用邏輯門。但是設計團隊可能需要通過背注時序運行門級功能仿真,因為缺少門級網(wǎng)表,這將難以進行。

附加提供物

一個有競爭力的軟IP核不只是一個Verilog或VHDL源文件的集合。出于同樣原因,一個好的硬核也不只是一個版圖數(shù)據(jù)庫。今天的IP核包含一系列可交付使用的提供物,可使SoC設計團隊將IP核整合到他們的設計中。這些附加提供物的目標是使IP核盡可能容易地整合到設計流程的各個環(huán)節(jié)。

圖1顯示了采用不同IP核的SoC開發(fā)活動。這里包括了軟核和硬核都必需的一些可交付使用的提供物。

1. 文檔創(chuàng)建

清晰和簡練的文檔是大多數(shù)技術產(chǎn)品的先決條件。然而,需要參考IP核文檔的人差異非常大,這使IP核技術文檔創(chuàng)建面臨非常大的挑戰(zhàn)。

在圖1中,每一個開發(fā)活動都有不同的文檔需求。例如,軟件開發(fā)者需要了解硬件的可編程特性,但他們可能不關心它是怎樣實現(xiàn)的。因此,一組好的文檔可使軟件開發(fā)者更容易發(fā)現(xiàn)他們所需的信息,而不致被大量無用的信息困擾。

最后,如果SoC團隊要為能復用部分IP核文檔的SoC創(chuàng)建文檔,IP提供商應該提供可編輯的源文件和引用權。

2. 接口檢查器

SoC團隊必須設計邏輯,以便與不同信號和IP核協(xié)議進行接口。為了確定其設計是否正確,IP提供商能夠提供接口檢查器模塊,以驗證所有接口信號和協(xié)議的正確運行。它可能與確認不變的靜態(tài)信號一樣簡單,也可能像驗證多周期總線協(xié)議的正確運行一樣復雜。

這些檢查器通過自動驗證給定接口處理類型是否正確運行的工作,大大簡化SoC團隊的工作。在一個非法處理的情況下,檢查器應該報告錯誤,使SoC設計師能夠容易地查明有缺陷的邏輯并排除故障。接口檢查器必須在SoC設計環(huán)境中準確工作。它們應該能夠非常容易地整合到功能仿真中,而不是以一種實際硬件的形式出現(xiàn)。

3. 協(xié)議制表器

IP提供商能夠提供另一種交付成果使接口驗證變得更加容易,這就是協(xié)議制表器。這是一個監(jiān)測接口處理的模塊,可觀察到各種特殊狀況。協(xié)議制表器保存所有可見的處理類型并報告沒被運行的“邊際”(corner case)。IP提供商必須提供一個進行接口完全驗證所需的邊角情況表。

在開發(fā)過程中,協(xié)議制表器將幫助SoC團隊決定哪些“邊際”情況需要繼續(xù)驗證。一旦開發(fā)結束,它同時確保通知SoC團隊已經(jīng)執(zhí)行了所有必需的“邊際”情況驗證。由于IP提供商對內(nèi)核接口具有最佳的理解,這個“邊際”情況表將比SoC團隊能夠想象的任何方案更加完善。

4. RAM檢查器

如果一個IP核擁有SoC團隊必須編譯和整合的內(nèi)部隨機存儲器,在處理過程中有可能引入瑕疵。排除由深度嵌入式RAM導致的故障對于SoC團隊是一件非常困難的事情,因為它經(jīng)常涉及通過內(nèi)核模塊跟蹤故障的工作。RAM檢查器能夠大大簡化排除RAM模塊導致的故障的工作。(當SoC團隊不得不通過一個IP核來排除故障時,這是一個非常糟的情況。他們應該能夠信賴它的正確運行。)

5. 快速仿真模型

對于SoC設計師來說,用一個大型IP核的RTL仿真完整的SoC可能非常緩慢。如果IP提供商能夠提供一個周期精確的內(nèi)核快速功能模型,客戶將從更快速仿真、更快速調(diào)試及更少地使用仿真授權中獲益。即使是一個非周期精確的模型,對于大多數(shù)SoC設計和調(diào)試已經(jīng)足夠好了。只要最后運行周期精確模型,在開發(fā)過程中就可以從快速功能模型中受益。

6. EDA工具支持

另一個內(nèi)核質(zhì)量指標是EDA工具的支持情況。由于不同設計團隊可能使用不同的工具,支持多種EDA工具的多種形式的可交付使用成果是目前先進內(nèi)核經(jīng)常能提供的。

例如,一個IP核使用Verilog設計而成,但那些使用基于VHDL的EDA工具和方法的客戶仍會要求VHDL。如果一個內(nèi)核只針對Verilog,那么SoC團隊在使用該內(nèi)核時,將不得不忍受一個麻煩且容易發(fā)生錯誤的轉(zhuǎn)換過程。

此外,IP提供商應該提供比需求格式更多的東西。不同的EDA工具可能有標準格式的不同實現(xiàn)方法。在以上的例子中,IP提供商不能僅為Verilog客戶提供Verilog RTL,它必須支持客戶使用特定的Verilog仿真器。否則,該客戶可能要調(diào)試與IP提供商所用的略微不同的Verilog仿真器相關的設計問題。

這個概念實際上適用于所有交付成果。對于硬核,這個概念同樣可在實現(xiàn)階段應用。硬核必須以一種被SoC團隊后端工具所支持的形式提供。而且IP提供商必須支持客戶使用的特殊后端工具。

對硬核來說,這個概念在實現(xiàn)階段同樣適用。硬核必須以能被SoC團隊后端工具支持的形式提供,而且IP提供商必須支持使用特定的后端工具。

7. EDA腳本實例

為了幫助快速展開各種設計活動,IP提供商應該提供所支持EDA工具的實例腳本。這是IP提供商幫助SoC團隊有效地使用IP核進行系統(tǒng)設計的另一種方法。該腳本可能如makefiles一樣簡單,可實現(xiàn)匯編功能仿真器。這些腳本也可能如一個全套的、針對功能回歸執(zhí)行的自動化設計腳本一樣復雜。在任何情況下,實例腳本對于SoC設計師來說總是很有用。

對于軟核來說,實例綜合腳本幾乎是必要的。至少它們應該提供頂層約束、故障路徑和多周期路徑。如果可能,應該同時提供實現(xiàn)若干工業(yè)標準綜合方法學的腳本。當然,這些實例腳本越簡單,對于SoC設計師來說就越容易理解、進行修改并集成到他們的流程中。

8. 功能內(nèi)核驗證

雖然SoC設計師不會修改軟IP核的RTL設計,但是他們確實會改變作為芯片設計常規(guī)部分的一些功能。這樣的例子包括掃描鏈接插入、時鐘緩存和RAM BIST集成。SoC設計團隊需要驗證這些改變不會對內(nèi)核的正確運行產(chǎn)生影響。

驗證新設計在功能上與以前設計沒有改變的一種方法是采用IP提供商提供的測試基準和測試套件,以全面驗證內(nèi)核是否正確運行。不幸的是,對于許多內(nèi)核來說,完整的測試套件太大了,以至于不能作為IP核的一部分來提供。因此,大多數(shù)IP提供商選用完整驗證套件組的子集,它同樣能夠驗證運行。大多數(shù)情況下,對于發(fā)現(xiàn)那些由以上設計變化類型引起的錯誤來說,這個子集已經(jīng)足夠了。

然而,形式驗證工具對于保證正確運行是一個更徹底的方法。這些工具可精確地驗證新設計與老設計的相同之處。支持形式驗證工具可使SoC團隊無需運行門級回歸。

9. 軟件協(xié)同開發(fā)工具

為新系統(tǒng)開發(fā)軟件的標準方式是,首先生產(chǎn)硬件樣片,然后開發(fā)運行在上面的軟件。然而,在很多情況下這延長了產(chǎn)品上市時間,因此軟件開發(fā)經(jīng)常與硬件開發(fā)平行進行。

軟件開發(fā)比硬件開發(fā)需要快得多的系統(tǒng)仿真。因此IP提供商必須提供一個非常快的IP核功能模型。這為低層固件的開發(fā)提供了足夠的性能。

對于更高的仿真速度,有時會使用硬件邏輯仿真器,它可比純仿真快一個數(shù)量級(雖然這仍然比實際硬件慢2至3個數(shù)量級)。這些工具非常難用,而且需要特殊的綜合。對于計劃進行硬件和軟件協(xié)同開發(fā)的SoC設計團隊來說,支持這些技術是對IP核的一個關鍵要求。

評估IP提供商

1. 是否設計成可復用?

例如,一個未對IP核產(chǎn)品做出完全承諾的IP提供商,它的產(chǎn)品可能只是將以前的設計重新封包成IP核。而一家認真致力于構建高質(zhì)量內(nèi)核的公司從一開始就把可復用作為設計理念。

首先,留意那些其源代碼為全定制硬核的軟核。由于這些原始設計不是針對可綜合的,與針對可綜合而設計的產(chǎn)品相比,其性能較差。在創(chuàng)建一個硬核時,可以基于已知實現(xiàn)風格進行優(yōu)化。但是,對于一個軟核,不應采用這種投機取巧的方法,因為它們可能導致非功能性的或非理想的實現(xiàn)。

在尋找一個軟核時,需要注意的另一個問題是寄存的接口信號。通過寄存IO,內(nèi)部邏輯在時序上可獨立于SoC設計團隊的任何方案。而且,它易于實現(xiàn)時序的可預測性,并為SoC設計師提供非常好的時序約束。所有這些使得SoC設計師更加輕松。

一個從一開始就針對可復用性而設計的軟核常常擁有更多的配置選擇,而且在執(zhí)行中有更好的靈活性。它同時很可能考慮用于多種設計環(huán)境。一個沒有考慮可復用的設計將在功能和實現(xiàn)方面缺乏靈活性。

2. 完整的產(chǎn)品線

好的IP提供商的另一個標志是擁有完整的IP核產(chǎn)品線。如果你選擇軟核,應該確認該公司提供的是考慮了未來產(chǎn)品改進的完整軟核產(chǎn)品線。如果你選擇硬核,應確認它可提供所有你將使用的工藝技術,他們是否計劃擴展其提供的軟核產(chǎn)品?他們?nèi)绾斡媱潓⒂埠艘浦驳叫乱淮に嚕?/p>

3. 維護與支持情況

產(chǎn)品維護和支持的質(zhì)量不是IP核特有的選擇因素,但是應小心那些缺乏全力支持的新興公司。即使是成熟的公司,維護IP核所必需的基礎架構一定程度上也是專門的。以下是注意事項匯總:

* 這家公司是否有一個清晰地為用戶提供文檔的方式,以幫助解答問題;

* 支持SoC隊伍的費用如何(你是否存在失去支持的危險);

* 這家公司能否坦白地披露設計中的缺陷;

* 這家公司發(fā)布修復缺陷新版本的頻率如何;

* IP提供商是否發(fā)布維護版本,為IP核增加新的功能或其他成果(如提供更多EDA工具支持);

* 一旦需要技術支持,這家公司的反饋如何?

* 如果技術支持反饋時間太慢,這個問題能改善嗎?

* 第一線的技術支持人員的素質(zhì)如何?

在很多情況下,技術支持的質(zhì)量并不是最初決定購買IP內(nèi)核的因素。但是在設計隊伍非常需要幫助的時候,支持不到位可能變成一個主要問題。最佳的技術支持是項目成功的必要因素。

責任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論