近年來,在數(shù)字通信、網(wǎng)絡、視頻和圖像處理領域,FPGA已經(jīng)成為高性能數(shù)字信號處理系統(tǒng)的關(guān)鍵元件.FPGA的邏輯結(jié)構(gòu)不僅包括查找表、寄存器、多路復用器、存儲器,而且還有快速加法器、乘法器和I/O處理專用電路.FPGA具有實現(xiàn)高性能并行算法的能力,是構(gòu)成高性能可定制數(shù)據(jù)通路處理器(數(shù)字濾波、FFT)的理想器件.如Virtex-II Pro FPGA包含高性能的可編程架構(gòu)、嵌入式PowerPC處理器和3.125Gbps收發(fā)器等.

但是,FPGA在數(shù)字信號處理領域的廣泛應用受限于幾個因素.首先,DSP開發(fā)人員不熟悉硬件設計,尤其是FPGA.他們使用Matlab驗證算法,運用C語言或匯編語言編程,通常不會使用硬件描述語言(VHDL或Verilog)實現(xiàn)數(shù)字設計.其次,雖然VHDL語言也提供了許多高層次的語言抽象,但是基于并行硬件系統(tǒng)的VHDL程序設計與基于微處理器的串行程序設計有很大的不同.

基于以上原因,Xilinx公司開發(fā)了基于Matlab的System Generator for DSP工具.System Generator for DSP是Simulink中一個基于FPGA的信號處理建模和設計工具.該工具可以將一個DSP系統(tǒng)表示為一個高度抽象的模塊,并自動將系統(tǒng)映射為一個基于FPGA的硬件方案.重要的是,該System Generator for DSP實現(xiàn)這些功能并沒有降低硬件性能.

1 System Generator for DSP的特點

Simulink為DSP系統(tǒng)提供了強有力的高層次建模環(huán)境,可大量應用于算法開發(fā)和驗證.System Generator for DSP作為Simulink的一個工具箱很好地體現(xiàn)了這些特性,同時又可以自動將設計轉(zhuǎn)換為可綜合的高效硬件實現(xiàn)方案.該硬件實現(xiàn)方案忠實于原始設計,因此設計模型與硬件實現(xiàn)在采樣點(在Simulink中定義)是一一對應的.通過使用Xilinx精心設計的IP(intellectual property)核可以使硬件方案具有較小的延遲和體積.雖然System Generator中的IP模塊是經(jīng)過功能抽象的,但是對于熟悉FPGA的設計者來說,該模塊也具有直接訪問底層硬件細節(jié)的能力.例如,可以指定System Generator乘法器模塊使用Virtex-II系列FPGA中的專用高速乘法器元件,用戶定義的IP模塊也能夠作為黑盒子插入系統(tǒng)之中,等等.

使用System Generator for DSP實現(xiàn)系統(tǒng)設計的主要特點有:

●在Simulink中實現(xiàn)FPGA電路的系統(tǒng)級建模,并自動生成硬件描述語言.

●自動生成Modelsim測試程序,支持軟硬件仿真.

●支持用戶創(chuàng)建的Simulink模塊.

●使用Xilinx FPGA自動實現(xiàn)硬件系統(tǒng).支持的Xilinx FPGA系列包括Spartan-II、Spartan-IIE、Spar-tan-3、Virtex、Virtex-E、Virtex-II、Virtex-II Pro.

2 使用System Generator for DSP實現(xiàn)系統(tǒng)級建模

傳統(tǒng)的DSP系統(tǒng)開發(fā)人員在設計一個DSP系統(tǒng)時,一般先研究算法,再使用Matlab或C語言驗證算法,最后由硬件工程師在FPGA或DSP上實現(xiàn)并驗證.典型的DSP系統(tǒng)設計流程如下:

(1) 用數(shù)學語言描述算法.

(2) 設計環(huán)境中使用雙精度數(shù)實現(xiàn)算法.

(3) 將雙精度運算變?yōu)槎c運算.

(4) 將設計轉(zhuǎn)換為有效的硬件實現(xiàn).

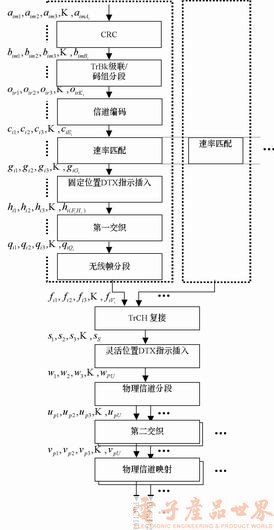

使用System Generator for DSP可以簡化這一過程.設計人員先在Matlab中對系統(tǒng)進行建模和算法驗證,經(jīng)過仿真后便可以直接將系統(tǒng)映射為基于FPGA的底層硬件實現(xiàn)方案.可用Simulink提供的圖形化環(huán)境對系統(tǒng)進行建模.System Generator for DSP包括被稱為Xilinx blockset的Simulink庫和模型到硬件實現(xiàn)的轉(zhuǎn)換軟件,可以將Simulink中定義的系統(tǒng)參數(shù)映射為硬件實現(xiàn)中的實體、結(jié)構(gòu)、端口、信號和屬性.另外,System Generator可自動生成FPGA綜合、仿真和實現(xiàn)工具所需的命令文件,因此用戶可以在圖形化環(huán)境中完成系統(tǒng)模型的硬件開發(fā).圖1為使用System Generator for DSP設計系統(tǒng)的流程圖.

在Matlab中,我們可以通過Simulink的庫瀏覽器使用Xilinx blockset庫中的模塊,Xilinx blockset庫中的模塊可以與Simulink其它庫中的模塊自由組合.Xilinx blockset庫中最重要的模塊是System Gen-erator,利用該模塊可完成系統(tǒng)級設計到基于FPGA的底層硬件設計的轉(zhuǎn)換工作.可以在System Generator模塊的屬性對話框中選擇目標FPGA器件、目標系統(tǒng)時鐘周期等選項.System Generator將Xilinx blockset中的模塊映射為IP庫中的模塊,接著從系統(tǒng)參數(shù)(例如采樣周期)推斷出控制信號和電路,再將Simulink的分層設計轉(zhuǎn)換為VHDL的分層網(wǎng)表,之后,System Generator即可調(diào)用Xilinx CORE Generator和VHDL模擬、綜合、實現(xiàn)工具來完成硬件設計.

由于一般的FPGA綜合工具不支持浮點數(shù),因此System Generator模塊使用的數(shù)據(jù)類型為任意精度的定點數(shù),這樣可以實現(xiàn)準確的硬件模擬.由于Simulink中的信號類型是雙精度浮點數(shù),因此在Xil-inx模塊和非Xilinx模塊之間必須插入Gateway In block和Gateway Out block模塊.通常Simulink中的連續(xù)時間信號在Gateway In block模塊中進行采樣,同時該模塊也可將雙精度浮點信號轉(zhuǎn)換為定點信號,而Gateway Out block模塊則可將定點信號轉(zhuǎn)換為雙精度浮點信號.大部分Xilinx模塊能夠根據(jù)輸入信號類型推斷輸出信號的類型.如果模塊的精度參數(shù)定義為全精度,則模塊將自動選擇輸出信號類型以保證不損失輸入信號精度,并自動進行符號位擴展和補零操作.用戶也可以自定義輸出信號類型來進行精度控制.

3 使用中需注意的問題

在FPGA系統(tǒng)設計中,時鐘的設計十分重要.因此必須正確理解System Generator中的時鐘和FPGA硬件時鐘之間的關(guān)系.Simulink中沒有明確的時鐘源信號,模塊在系統(tǒng)參數(shù)中定義的采樣周期點進行采樣.硬件設計中的外部時鐘源對時序邏輯電路十分重要.在System Generator模塊中,通過定義Simulink System Period和FPGA System Clock Period參數(shù)可以建立Simulink采樣周期和硬件時鐘間的關(guān)系,也可通過設置這些參數(shù)來改變Simulink中模擬時間和實際硬件系統(tǒng)中時間的比例關(guān)系.Simulink的系統(tǒng)周期一般是各模塊采樣周期的最大公約數(shù).FPGA的硬件時鐘是單位為ns的硬件時鐘周期.例如,若Simulink中有兩個模塊,采樣周期分別為2s和3s,而FPGA系統(tǒng)時鐘周期為10ns,則Simulink系統(tǒng)周期應該為兩個模塊采樣周期的最大公約數(shù)即為1s.這意味著Simulink中的1s對應實際硬件系統(tǒng)的10ns.在生成硬件系統(tǒng)前,System Generator將自動檢查用戶定義的Simulink系統(tǒng)周期參數(shù)是否與系統(tǒng)中模塊的采樣周期相沖突,如果沖突,則提示用修改Simulink系統(tǒng)周期參數(shù).

有些情況會導致System Generator模塊產(chǎn)生不確定數(shù)(NaN-not a number).如在雙端口RAM模塊中,兩個端口同時對模塊中的某一地址進行寫操作時,該地址中的數(shù)據(jù)將被標記為NaN.如果模塊中有不確定數(shù)出現(xiàn),則表明該模塊的最終硬件實現(xiàn)將會有不可預測的行為,當Simulink進行仿真時,System Generator將會捕捉該錯誤.

4 應用實例

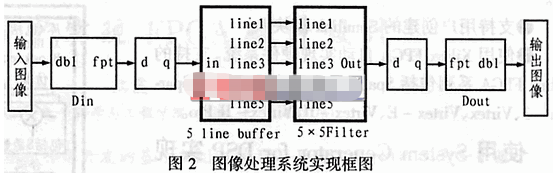

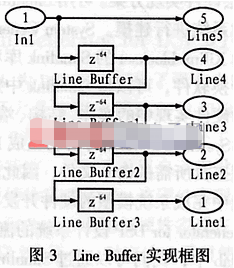

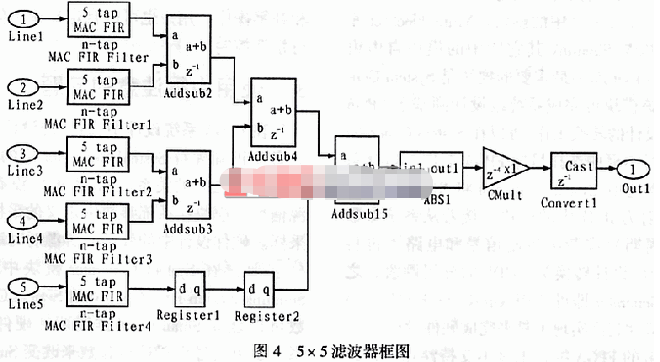

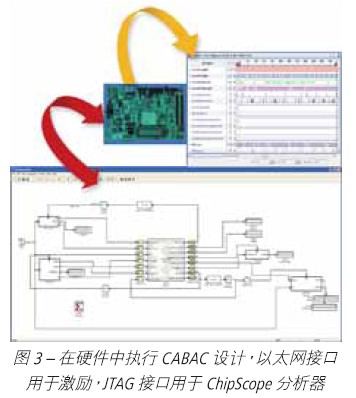

圖2是一個圖像處理應用實例的系統(tǒng)實現(xiàn)框圖.該應用實例使用5×5的二維FIR濾波器完成圖像增強預處理.該系統(tǒng)將輸入圖像分別延遲0×N(N為輸入圖像寬度)、1×N、2×N、3×N、4×N個采樣點后輸入5個Line Buffer,數(shù)據(jù)在Line Buffer中緩存后并行輸入5個5抽頭的MAC FIR濾波器.濾波器系統(tǒng)存儲于FPGA的塊RAM中,圖像數(shù)據(jù)經(jīng)濾波器處理后輸出.圖3為Line Buffer實現(xiàn)框圖,圖4為5×5濾波器框圖.

責任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論