,承擔(dān)FPGA最小系統(tǒng)運(yùn)行及高速數(shù)據(jù)處理和存儲(chǔ)的功能。FPGA選用紫光同創(chuàng)28nm工藝Logos2系列PG2L50H-6IFBG484。

PG2L50H和DDR3之間數(shù)據(jù)交互時(shí)鐘頻率最高533MHz,2

2023-12-28 11:29:51

:①使用傳統(tǒng)的串/并口。傳統(tǒng)的串口(如RS232),其傳輸速率為幾十kb/s到100 kb/s,而系統(tǒng)所要求的數(shù)據(jù)傳輸速率很高,而且還要實(shí)現(xiàn)數(shù)據(jù)的采集與傳輸同步進(jìn)行,串口的速率遠(yuǎn)遠(yuǎn)達(dá)不到實(shí)時(shí)要求;對(duì)于

2020-01-07 07:00:00

提高競(jìng)爭(zhēng)力,嵌入式系統(tǒng)開(kāi)發(fā)人員需要一種能夠幫助他們開(kāi)發(fā)獨(dú)具優(yōu)勢(shì)產(chǎn)品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實(shí)現(xiàn)方法具有低成本和快速面市等優(yōu)點(diǎn),是多芯片和ASICSoC非常有吸引力的替代

2021-07-14 08:00:00

FPGA芯片-XC3S50A-5TQ144C可由其他什么芯片代替?

2012-04-07 15:44:32

1 前言現(xiàn)場(chǎng)可編程邏輯器件(FPGA)在高速采集系統(tǒng)中的應(yīng)用越來(lái)越廣,由于FPGA對(duì)采集到的數(shù)據(jù)的處理能力比較差,故需要將其采集到的數(shù)據(jù)送到其他CPU系統(tǒng)來(lái)實(shí)現(xiàn)數(shù)據(jù)的處理功能,這就使FPGA系統(tǒng)與其

2011-11-24 16:10:01

概論(數(shù)字前端概述)、第1/2/3代數(shù)字接收機(jī)和發(fā)射機(jī)的結(jié)構(gòu)、寬帶數(shù)字下變頻(DDC)和數(shù)字上變頻(DUC)的原理和FPGA實(shí)現(xiàn)、Xilinx公司的無(wú)線通信解決方案、數(shù)字調(diào)制和解調(diào)(QPSK和OFDM

2009-07-21 09:22:42

的設(shè)計(jì)實(shí)現(xiàn)本方案的所有控制邏輯設(shè)計(jì)用一片Xilinx Spartan II系列XC2S200型FPGA器件實(shí)現(xiàn)。采用Spansion公司的NOR Flash存儲(chǔ)器來(lái)存放配置文件,其型號(hào)為

2019-06-10 05:00:08

隨著光纖傳感技術(shù)的發(fā)展,光纖傳感器已成功應(yīng)用于周界入侵探測(cè)等安全防范領(lǐng)域。目前,已經(jīng)應(yīng)用于光纖微擾動(dòng)傳感器或相似系統(tǒng)的數(shù)據(jù)處理方案比較多,有DSP、FPGA、FPGA+DSP、labview等多種

2020-09-04 09:56:23

FPGA進(jìn)行串口通信如何實(shí)現(xiàn)數(shù)據(jù)自動(dòng)換行?FPGA發(fā)的數(shù)據(jù)是16BIT位寬的通過(guò)串口傳給電腦的時(shí)候如何實(shí)現(xiàn)數(shù)據(jù)自動(dòng)接收換行?

2013-12-05 08:32:12

產(chǎn)物。Xilinx Virtex-II 系列平臺(tái) FPGA 提供了現(xiàn)有任何可編程邏輯解決方案的最高性能和最高密度。基準(zhǔn)測(cè)試程序表明,該系列產(chǎn)品在系統(tǒng)性能上比最相近的競(jìng)爭(zhēng)器件高出 38%。盡管容量從四萬(wàn)到八百萬(wàn)系統(tǒng)

2013-09-06 16:28:27

XC3S50A-4FTG256IFPGA的故障率是多少?我沒(méi)有在數(shù)據(jù)表中找到任何數(shù)據(jù)以上來(lái)自于谷歌翻譯以下為原文What is the failure rate ofXC3S50A-4FTG256IFPGA?I didn't find any data in datasheets

2019-01-10 11:05:53

和高端&高可靠設(shè)備。只做原裝正品!聯(lián)系人黃云艷一 XC5VLX50-1FF1153I的應(yīng)用領(lǐng)域Xilinx All Programmable 平臺(tái)和解決方案可提供各種性能和系統(tǒng)集成級(jí)別,它與

2018-10-27 08:17:30

(HKMG)工藝技術(shù)之上,可實(shí)現(xiàn)I / O帶寬2.9 Tb / s,200萬(wàn)邏輯單元容量和5.3 TMAC / s DSP極大地提高了系統(tǒng)性能,而功耗卻降低了50%7系列FPGA功能摘要?基于可配置為

2021-04-13 14:27:32

助手(TTL轉(zhuǎn)u***)發(fā)送數(shù)據(jù),數(shù)據(jù)可被串口助手正常接收,波形也正常。【猜想原因及解決方案】1.外設(shè)的TX驅(qū)動(dòng)能力不夠,需在外設(shè)和單片機(jī)之間加隔離芯片;2.想不到其他原因了。。。求各位的指點(diǎn)。。。`

2020-08-20 17:39:56

我寫(xiě)了一個(gè)STM32的程序,串口1接收數(shù)據(jù),然后串口2把串口1接收的數(shù)據(jù)輸出來(lái)?是通過(guò)串口中斷函數(shù)來(lái)實(shí)現(xiàn)嗎?

2015-06-02 19:57:49

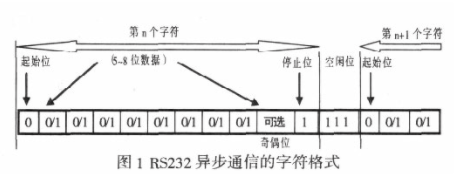

和USB_TXD的時(shí)序。USB_RXD的時(shí)序由CH340芯片產(chǎn)生,FPGA根據(jù)時(shí)序來(lái)接收數(shù)據(jù);USB_TXD的時(shí)序由FPGA芯片產(chǎn)生,FPGA要按規(guī)范來(lái)產(chǎn)生時(shí)序,使得CH340可以正確地接收。我們可以把產(chǎn)生時(shí)序

2018-11-13 10:38:10

實(shí)驗(yàn)?zāi)康模?b class="flag-6" style="color: red">實(shí)現(xiàn)芯片串口收發(fā)數(shù)據(jù),按鍵中斷串口發(fā)送數(shù)據(jù):按下按鍵,向串口發(fā)送數(shù)據(jù),并通過(guò)虛擬終端顯示出來(lái);串口接收數(shù)據(jù)中斷來(lái)控制LED亮/滅:通過(guò)串口助手向MCU發(fā)送數(shù)據(jù),“A”把LED燈點(diǎn)亮,“B

2021-12-16 08:22:39

有一個(gè)問(wèn)題,采用fpga, fpga, fpga讀取ad2-s80a (千兆瓦)輸出二進(jìn)制數(shù)據(jù),當(dāng)fpga, fpga, fpga設(shè)置采樣速率為500公里時(shí),數(shù)據(jù)沒(méi)有問(wèn)題,當(dāng)采樣速率設(shè)置為50mhz 50mhz時(shí),精機(jī)的芯片會(huì)出現(xiàn)死機(jī)

不發(fā)出數(shù)據(jù)的現(xiàn)象,請(qǐng)問(wèn)這個(gè)是什么原因引起的這個(gè)問(wèn)題。

2023-12-18 07:56:00

大家好,我想在PC和FPGA之間發(fā)送和接收數(shù)據(jù)。我有XC2S200E PQ208 FPGA和CY7C68001 u***接口設(shè)備(CyPress)。有沒(méi)有人有關(guān)于這個(gè)主題的信息和例子?以上來(lái)自于谷歌

2019-05-16 14:25:20

隨著光纖傳感技術(shù)的發(fā)展,光纖傳感器已成功應(yīng)用于周界入侵探測(cè)等安全防范領(lǐng)域。目前,已經(jīng)應(yīng)用于光纖微擾動(dòng)傳感器或相似系統(tǒng)的數(shù)據(jù)處理方案比較多,有DSP、FPGA、FPGA+DSP、labview等多種

2020-08-31 18:54:17

概論(數(shù)字前端概述)、第1/2/3代數(shù)字接收機(jī)和發(fā)射機(jī)的結(jié)構(gòu)、寬帶數(shù)字下變頻(DDC)和數(shù)字上變頻(DUC)的原理和FPGA實(shí)現(xiàn)、Xilinx公司的無(wú)線通信解決方案、數(shù)字調(diào)制和解調(diào)(QPSK和OFDM

2009-07-21 09:20:11

概論(數(shù)字前端概述)、第1/2/3代數(shù)字接收機(jī)和發(fā)射機(jī)的結(jié)構(gòu)、寬帶數(shù)字下變頻(DDC)和數(shù)字上變頻(DUC)的原理和FPGA實(shí)現(xiàn)、Xilinx公司的無(wú)線通信解決方案、數(shù)字調(diào)制和解調(diào)(QPSK和OFDM

2009-07-24 13:07:08

最近,我在使用LPC2378芯片開(kāi)發(fā)時(shí),遇到芯片串口在中斷方式下不能接收超過(guò)16個(gè)字節(jié)的幀數(shù)據(jù)的問(wèn)題,我很苦惱,請(qǐng)教高手解決方案。

2014-05-15 20:59:52

matlab串口接收數(shù)據(jù)學(xué)習(xí)【1】與STM32通信雖然可以把所有算法代碼集成到STM32中運(yùn)行,但最終還是希望能夠獲得運(yùn)算結(jié)果和中間過(guò)程的一些數(shù)據(jù)集,當(dāng)然日后也希望能夠在STM32于matlab

2021-08-17 07:03:00

本帖最后由 1154286643 于 2015-11-12 16:25 編輯

各位高手,大家好。我是FPGA新手,我有個(gè)14引腳的xilinx下載器,現(xiàn)在有一個(gè)XC3S50

2015-11-11 21:12:10

盤(pán)古50Pro核心板是一款基于紫光同創(chuàng)Logos2系列PG2L50H-FBG484主控芯片的全新國(guó)產(chǎn)高性能FPGA核心板,相較于第一代盤(pán)古50K器件全新升級(jí),具有高數(shù)據(jù)帶寬、高存儲(chǔ)容量的特點(diǎn)

2023-09-22 14:35:21

DSP和A/D芯片間增加FPGA。FPGA是整個(gè)系統(tǒng)的時(shí)序控制中心和數(shù)據(jù)交換橋梁,而且能夠實(shí)現(xiàn)對(duì)底層的信號(hào)快速預(yù)處理,在很多信號(hào)系統(tǒng)中,底層的信號(hào)預(yù)處理算法要處理的數(shù)據(jù)量大;對(duì)處理速度要求高,但算法

2019-07-05 06:41:27

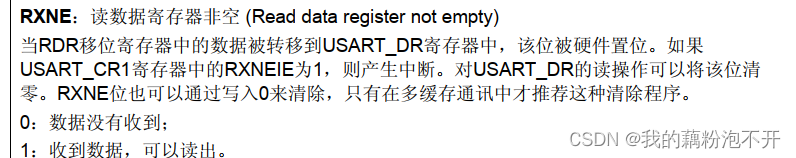

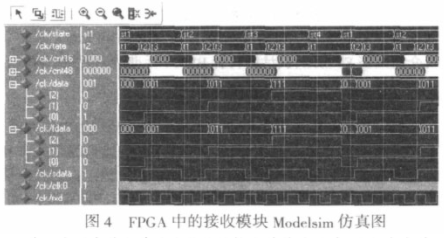

的UART的實(shí)現(xiàn)方法,具體描述了發(fā)送、接收等模塊的設(shè)計(jì),恰當(dāng)使用了有限狀態(tài)機(jī),實(shí)現(xiàn)了FPGA片上UART的設(shè)計(jì),給出了仿真結(jié)果。關(guān)鍵詞:通用異步收發(fā)器;串口通信;現(xiàn)場(chǎng)可編程邏輯器件;有限狀態(tài)機(jī)

2019-06-21 07:17:24

報(bào)警,擊穿故障時(shí)立即閉鎖出口。硬件設(shè)計(jì)的核心為兩塊相同的FPGA,該裝置的所有邏輯功能都是利用這兩塊FPGA芯片實(shí)現(xiàn)。該芯片選用XILINX的XC3S50AN,擁有50 k個(gè)系統(tǒng)門、1 584個(gè)邏輯

2019-06-06 05:00:39

不定長(zhǎng)數(shù)據(jù)接收的原理是什么?怎么實(shí)現(xiàn)串口數(shù)據(jù)的不定長(zhǎng)接收?

2021-11-16 08:11:09

完成主要部分設(shè)計(jì)的。2 機(jī)器視覺(jué)系統(tǒng)設(shè)計(jì)2.1 設(shè)計(jì)原理系統(tǒng)原理框圖如圖1所示。這個(gè)解決方案基于Xilinx低功耗低成本的Spartan 3E FPGA芯片上實(shí)現(xiàn),它提供了整合CameraLink

2019-05-05 08:30:00

。像Spartan 6 XC6SLX9FPGA這樣的低端FPGA是否足以實(shí)現(xiàn)這種數(shù)據(jù)速度?我應(yīng)該使用哪個(gè)記憶時(shí)間? 如果不是,任何想法?非常感謝您的關(guān)注。

2020-03-26 09:31:54

最近在做藍(lán)橋杯往屆試題,遇到了要求利用串口2接收數(shù)據(jù),還需要使用PA1,PA2輸出PWM信號(hào),但是USART2的TXD和PWM的PA2腳是同一個(gè)引腳,導(dǎo)致按照正常初始化步驟運(yùn)行,會(huì)發(fā)現(xiàn)串口可以正常

2021-08-16 07:36:08

STM32CUBEME--2USART通過(guò)DMA方式接收不定長(zhǎng)數(shù)據(jù)概述硬件準(zhǔn)備選擇芯片型號(hào)配置時(shí)鐘源配置時(shí)鐘樹(shù)串口配置中斷定時(shí)器配置概述本文利用中斷實(shí)現(xiàn)串口不長(zhǎng)接收(非DMA),使用HAL庫(kù),將接受

2021-08-11 07:07:58

。LCMXO2-640HC-4TG100C可編程邏輯器件FPGA芯片---LED控制解決方案實(shí)現(xiàn)普通LED傳輸條碼數(shù)據(jù)——條碼仿真參考設(shè)計(jì)能夠實(shí)現(xiàn)普通LED傳輸條碼數(shù)據(jù)。可驅(qū)動(dòng)LED來(lái)傳輸可供收款機(jī)讀取的脈沖數(shù)據(jù)

2019-09-20 15:13:30

1、在FPGA中實(shí)現(xiàn)串口協(xié)議的設(shè)計(jì)在FPGA中實(shí)現(xiàn)串口協(xié)議,通過(guò)Anlogic_FPGA開(kāi)發(fā)板上的“UART2USB”口接收從計(jì)算機(jī)發(fā)來(lái)的數(shù)據(jù)。實(shí)驗(yàn)設(shè)計(jì)思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

何時(shí)刻總線上只有一個(gè)主控器件(主節(jié)點(diǎn))實(shí)現(xiàn)總線的控制操作,對(duì)總線上的其他節(jié)點(diǎn)尋址,可分時(shí)實(shí)現(xiàn)點(diǎn)-點(diǎn)的數(shù)據(jù)傳送。因此總線上每個(gè)節(jié)點(diǎn)都有一個(gè)固定的節(jié)點(diǎn)地址。

I2C 總線上主節(jié)點(diǎn)的地址由軟件給定,此地

2023-08-14 18:21:26

提高競(jìng)爭(zhēng)力,嵌入式系統(tǒng)開(kāi)發(fā)人員需要一種能夠幫助他們開(kāi)發(fā)獨(dú)具優(yōu)勢(shì)產(chǎn)品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實(shí)現(xiàn)方法具有低成本和快速面市等優(yōu)點(diǎn),是多芯片和ASICSoC非常有吸引力的替代

2021-07-12 08:00:00

芯片必須通過(guò)PCI總線接口與FPGA進(jìn)行相連,實(shí)現(xiàn)數(shù)據(jù)的傳輸。如果只用FPGA和DSP來(lái)實(shí)現(xiàn)對(duì)PCI外設(shè)的控制,需要設(shè)計(jì)復(fù)雜的接口邏輯,在1394b高速數(shù)據(jù)傳輸系統(tǒng)中不僅會(huì)影響FPGA本身的性能,而且

2012-05-14 12:35:39

命令配置,LCD顯示部分測(cè)試結(jié)果,采用串口通信與下位機(jī)進(jìn)行命令和數(shù)據(jù)的交互,實(shí)現(xiàn)本地便捷控制與監(jiān)測(cè)。2、系統(tǒng)硬件及FPGA設(shè)計(jì)多路采集與切換系統(tǒng)的硬件設(shè)計(jì)主要由電源與時(shí)鐘模塊、FPGA邏輯控制模塊

2021-07-12 08:30:00

的數(shù)據(jù)發(fā)送和接收功能的實(shí)現(xiàn)。圖 9 W5500功能實(shí)測(cè)結(jié)果圖3 結(jié)語(yǔ)本系統(tǒng)實(shí)現(xiàn)了基于FPGA的,采用嵌入式以太網(wǎng)W5500芯片以硬件形式實(shí)現(xiàn)的TCP/IP協(xié)議棧,提高了CPU的處理效率,并且使得通信速率在很大程度上得到了提高,為以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設(shè)計(jì)提供了一種有效的方式。

2018-08-07 10:10:25

,基于ARINC664規(guī)范第7部分,提出符合該規(guī)范的基于FPGA的AFDX端系統(tǒng)協(xié)議芯片和相應(yīng)AFDX端系統(tǒng)板卡的設(shè)計(jì)方案,并給出關(guān)鍵模塊的具體實(shí)現(xiàn);通過(guò)對(duì)端系統(tǒng)協(xié)議芯片進(jìn)行測(cè)試驗(yàn)證,證明該端系統(tǒng)協(xié)議芯片

2010-05-13 09:09:08

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:04:25

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:06:43

FPGA(XC3S200),經(jīng)PID調(diào)節(jié)器控制電流環(huán);同樣,斬波電壓電流經(jīng)濾波通過(guò)A/D轉(zhuǎn)換也進(jìn)人FPGA。圖2所示為FPCA的最小系統(tǒng)電路,XCF02S為FPGA XC3S200的配置芯片

2016-02-01 14:44:30

大和數(shù)據(jù)精度高,結(jié)合片內(nèi)乘法器和存儲(chǔ)能力本文選一片ALTERA公司的StratixⅡ系列EP2S90 FPGA芯片。StratixⅡ系列的EP2S90器件具有152個(gè)接收機(jī)和156個(gè)發(fā)送機(jī)通道、支持

2015-02-05 15:34:43

充電器接收器解決方案,及其與基于FPGA的詳細(xì)系統(tǒng)架構(gòu)的關(guān)系。 2. WPC標(biāo)準(zhǔn)概述 WPC Qi標(biāo)準(zhǔn)提供無(wú)線充電器系統(tǒng)的詳細(xì)說(shuō)明,包括通信和傳輸協(xié)議。功率始終從充電板傳輸至移動(dòng)設(shè)備。充電板包含一個(gè)

2018-09-27 15:35:58

Xilinx公司的SPARTANIII OFP封裝的XC3S400-4PQ208C,總邏輯門為400k門。經(jīng)綜合、適配、仿真、布局布線后僅占用比較少的器件資源。整個(gè)系統(tǒng)下載到FPGA后在50MHz時(shí)鐘

2011-07-11 21:34:37

。 2 輸入輸出接口研究 Virtex Ⅱ-PRO系列是在Virtex Ⅱ系列FPGA的基礎(chǔ)上,嵌入了高速I/O接口和IBM PowerPC處理器,它能實(shí)現(xiàn)超高帶寬的系統(tǒng)芯片設(shè)計(jì),支持LVDS

2018-12-18 10:22:18

一片XilinxSpartanII系列XC2S200型FPGA器件實(shí)現(xiàn)。采用Spansion公司的NORFlash存儲(chǔ)器來(lái)存放配置文件,其型號(hào)為S29GL512N,容量為512Mb。系統(tǒng)總體框圖如圖3

2019-06-06 05:00:38

,無(wú)需更換硬件設(shè)備[1]。基于此,本文在研究LabVIEW的基礎(chǔ)上,開(kāi)發(fā)了基于LabVIEW的串口收錄系統(tǒng),以單片機(jī)為核心的硬件部分作為前端數(shù)據(jù)采集系統(tǒng),可實(shí)現(xiàn)200 kHz的采樣速率、16 bit

2014-12-24 11:10:33

,PC端,利用強(qiáng)大的串口調(diào)試工具——串口獵人,來(lái)實(shí)現(xiàn)數(shù)據(jù)的接收分析,并將數(shù)據(jù)分別以波形、碼表、柱狀圖的形式動(dòng)態(tài)顯示出來(lái),以讓使用者能夠直觀的看到ADC采集到的信號(hào)細(xì)節(jié)。同時(shí),用戶也可以使用串口獵人通過(guò)

2019-05-09 17:57:42

ARINC429總線接口板的研制,實(shí)現(xiàn)多通道ARINC429總線數(shù)據(jù)的接收和發(fā)送,成為目前對(duì)飛機(jī)機(jī)載總線接口研究的重點(diǎn)。 1 ARINC429總線簡(jiǎn)介 在現(xiàn)代民用飛機(jī)上,系統(tǒng)與系統(tǒng)之間、系統(tǒng)

2019-06-13 05:00:06

如何實(shí)現(xiàn)串口USART2的發(fā)送和接收功能呢?如何實(shí)現(xiàn)USART2中斷接收任意長(zhǎng)度和任意格式的數(shù)據(jù)呢?

2022-01-20 06:16:27

你好我是xilinx xc3s50an的新用途。我想將.bit文件或.mcs文件寫(xiě)入閃存系統(tǒng)內(nèi)閃存。如何寫(xiě)入系統(tǒng)內(nèi)閃存?我閱讀了文檔,并且有命令和地址,以便編寫(xiě)系統(tǒng)內(nèi)閃存。是否存在一系列操作以使

2019-05-15 10:20:08

,最終程序編譯通過(guò)了,但是出現(xiàn)了4個(gè)時(shí)序約束問(wèn)題,實(shí)際BULK OUT可以傳出數(shù)據(jù),但是BULK IN接收數(shù)據(jù)失敗。

請(qǐng)問(wèn)是否是我所使用的方式有誤?所提供的verilog文件是否有更詳細(xì)的使用說(shuō)明?

或者說(shuō),該如何使用FPGA與FX3實(shí)現(xiàn)數(shù)據(jù)的傳輸?

2024-02-28 07:44:14

求大神幫忙看看哪有問(wèn)題,用串口給發(fā)數(shù)據(jù)不能實(shí)現(xiàn)燈的亮滅#include #define uchar unsigned char#define S2RI 0x01#define S2TI 0x02

2019-09-29 06:54:22

請(qǐng)問(wèn)一下有沒(méi)有采用EEPROM對(duì)大容量FPGA芯片數(shù)據(jù)實(shí)現(xiàn)串行加載的實(shí)際方案?

2021-04-08 06:01:39

一種在FPGA中實(shí)現(xiàn)的基于軟判決的Viterbi譯碼算法,并以一個(gè)(2,1,2)、回溯深度為10的軟判決Viterbi譯碼算法為例驗(yàn)證該算法,在Xilinx的XC3S500E芯片上實(shí)現(xiàn)了該譯碼器,最后對(duì)其性能做了分析。 關(guān)鍵詞: OFDM;Viterbi譯碼;軟判決;FPGA

2009-09-19 09:41:24

目前四個(gè)接收數(shù)據(jù)的串口(串口2-5),能實(shí)現(xiàn)單獨(dú)接收連接手柄的數(shù)據(jù),通過(guò)發(fā)送串口發(fā)送,不能實(shí)現(xiàn)接兩個(gè)手柄讀數(shù)據(jù)及將手柄從一個(gè)串口取出放到另一個(gè)串口上讀數(shù)據(jù)。程序是在RT-Thread系統(tǒng)上實(shí)現(xiàn)的,芯片是STM32F4的。

2018-09-01 15:47:53

我的FPGA需要實(shí)現(xiàn)如下功能:接收一個(gè)兩字節(jié)的命令,如:16'h8003,8位字節(jié)接收,然后解析,我的實(shí)現(xiàn)如下,1)一共三個(gè)模塊,頂層模塊uart_top();2)子模塊uart_ctrl( )實(shí)現(xiàn)

2012-11-21 16:17:57

時(shí)間采樣實(shí)現(xiàn)2.1 系統(tǒng)硬件實(shí)現(xiàn)框圖系統(tǒng)的總體框圖如圖2,FPGA 控制的等效采樣時(shí)鐘連接到ADC 器件的時(shí)鐘部分,ADC 器件在時(shí)鐘的控制下對(duì)寬帶模擬信號(hào)進(jìn)行采樣,采集到的數(shù)據(jù)傳送到FPGA 中

2020-10-21 16:43:20

盤(pán)古50Pro核心板是一款基于紫光同創(chuàng)Logos2系列PG2L50H-FBG484主控芯片的全新國(guó)產(chǎn)高性能FPGA核心板,相較于第一代盤(pán)古50K器件全新升級(jí),具有高數(shù)據(jù)帶寬、高存儲(chǔ)容量的特點(diǎn),適用于

2023-09-18 17:02:58

1:在某些場(chǎng)合下,串口讀取數(shù)據(jù)時(shí),不能影響系統(tǒng)本身的電氣屬性,特別是在電容信號(hào)相關(guān)的電路中,串口的使用需要做到與原系統(tǒng)的隔離。2:紅外隔離方案是比較節(jié)約成本,而且相對(duì)穩(wěn)定的方案紅外發(fā)射管:紅外接收

2019-11-07 19:08:50

是整個(gè)溫控系統(tǒng)的硬件基礎(chǔ),其中涉及到溫度采集,與微處理器通信,串口輸出,控制數(shù)模轉(zhuǎn)換芯片等多個(gè)組成部分。本文提出一種高效實(shí)用的FPGA接口設(shè)計(jì),它能夠完成協(xié)調(diào)各個(gè)組成部分有序工作,準(zhǔn)確、快速實(shí)現(xiàn)數(shù)據(jù)

2020-08-19 09:29:48

USB協(xié)議芯片FT245BM,實(shí)現(xiàn)了FPGA與PC機(jī)的USB通信,該方法不用微控制器,減少了元器件的個(gè)數(shù),并且占用FPGA資源很少,FPGA仍然可以實(shí)現(xiàn)其他邏輯功能,系統(tǒng)設(shè)計(jì)的靈活性很大。二

2019-04-22 07:00:07

USB協(xié)議芯片FT245BM,實(shí)現(xiàn)了FPGA與PC機(jī)的USB通信,該方法不用微控制器,減少了元器件的個(gè)數(shù),并且占用FPGA資源很少,FPGA仍然可以實(shí)現(xiàn)其他邏輯功能,系統(tǒng)設(shè)計(jì)的靈活性很大。二

2019-04-26 07:00:12

XC2S200型FPGA器件實(shí)現(xiàn)。采用Spansion公司的NOR Flash存儲(chǔ)器來(lái)存放配置文件,其型號(hào)為S29GL512N,容量為512 Mb。系統(tǒng)總體框圖如圖3所示。上位機(jī)軟件包括Flash燒寫(xiě)

2019-05-30 05:00:05

ALINX SoM AC7A035,基于Artix-7 XC7A35T-2FBG484I,由FPGA + 2 DDR3 + QSPI FLASH組成,包括硬件的所有基本組件。適用于高速數(shù)據(jù)通信、視頻

2022-06-17 16:19:25

ALINX SoM AC7A200T,基于Artix-7 XC7A200T-2FGG484I,由FPGA + 2 DDR3 + QSPI FLASH組成,包括硬件的所有基本組件。適用于高速數(shù)據(jù)

2022-06-17 17:48:42

XC7A50T-1FGG484C FPGA可編程邏輯器件XILINX/賽靈思ALINX SoM AC7A50T,基于Artix-7 XC7A50T-1FGG484C,由FPGA + 2 DDR3

2022-06-17 17:53:59

,同時(shí)功耗比上一代設(shè)備低50%,為ASSP和ASIC提供完全可編程的替代方案。產(chǎn)品概述產(chǎn)品型號(hào)XC7A50T-1FGG484C描述IC FPGA 250 I/O 4

2022-08-03 16:23:43

串口通訊是上微機(jī)與下微機(jī)通訊過(guò)程中一個(gè)較為常見(jiàn)的問(wèn)題。本文提出了一個(gè)串口通訊中打包數(shù)據(jù)的接收方案,并用VB 語(yǔ)言對(duì)此方案進(jìn)行了實(shí)現(xiàn)。經(jīng)過(guò)實(shí)際測(cè)試,該方案不僅能滿

2009-09-17 10:47:34 51

51 本實(shí)驗(yàn)是基于EasyFPGA030 的串口接收設(shè)計(jì)。FPGA 除了需要控制外圍器件完成特定的功能外,在很多的應(yīng)用中還需要完成FPGA 和FPGA 之間、FPGA 和外圍器件之間以及FPGA 和微機(jī)的數(shù)據(jù)交換和

2009-11-02 17:04:13 33

33 net2.0實(shí)現(xiàn)多串口GPS數(shù)據(jù)接收設(shè)計(jì)應(yīng)用

2010-02-08 16:42:00 25

25 本實(shí)驗(yàn)是基于EasyFPGA030 的串口接收設(shè)計(jì)。FPGA 除了需要控制外圍器件完成特定的功能外,在很多的應(yīng)用中還需要完成FPGA 和FPGA 之間、FPGA 和外圍器件之間以及FPGA 和微機(jī)的數(shù)據(jù)交換和

2010-03-11 15:39:55 30

30 本文基于XILINX可編程邏輯器件XC4VLX25 FPGA開(kāi)發(fā)了一個(gè)中頻信號(hào)接收系統(tǒng),利用一個(gè)可配置的硬件平臺(tái)實(shí)現(xiàn)了模擬信號(hào)數(shù)字處理的設(shè)計(jì),為軟件無(wú)線電技術(shù)的研究提供了一個(gè)先進(jìn)的實(shí)驗(yàn)

2010-07-28 18:01:48 17

17 采用Actel FPGA的多串口擴(kuò)展方案

在當(dāng)前的多串口的擴(kuò)展應(yīng)用中,雖然市面上有部分的多串口擴(kuò)展芯片,但是其可擴(kuò)展的串口數(shù)量有限并

2010-03-18 11:11:51 2481

2481 本文介紹了一種實(shí)用的基于FPGA的以太網(wǎng)視頻廣播接收系統(tǒng),由于采用了FPGA技術(shù),使得系統(tǒng)結(jié)構(gòu)簡(jiǎn)單,可靠性高。最后進(jìn)行了波形仿真,結(jié)果表明了設(shè)計(jì)的正確性。

2011-09-27 16:39:44 1004

1004

本文主要介紹了python串口接收數(shù)據(jù)。其中涉及了Python使用線程來(lái)接收串口數(shù)據(jù),以及python3 Serial 串口助手的接收讀取數(shù)據(jù)。詳細(xì)了介紹了串口接收數(shù)據(jù)的程序開(kāi)發(fā)過(guò)程。

2018-01-15 09:52:42 45222

45222

X字節(jié)的數(shù)據(jù)。最后,用一個(gè)狀態(tài)機(jī)來(lái)實(shí)現(xiàn)相鄰兩個(gè)字符串的判斷。如果串口在相鄰兩個(gè)字符串之間接收時(shí)間大于50ms,則判斷為兩個(gè)獨(dú)立的字符串;如果小于50ms,則自動(dòng)拼接前后兩個(gè)字符串。

2018-01-15 15:49:34 65118

65118

資源。為簡(jiǎn)化設(shè)計(jì),降低硬件資源開(kāi)銷,可以在FPGA中利用IP核實(shí)現(xiàn)的嵌入式微處理器來(lái)對(duì)串口數(shù)據(jù)進(jìn)行處理。

2019-08-02 08:08:00 3816

3816 本文檔的主要內(nèi)容詳細(xì)介紹的是xc7z020和xc7z010 FPGA芯片的電路原理圖免費(fèi)下載。

2019-02-12 17:20:24 471

471 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA可編程邏輯器件芯片XC6SLX16的電路原理圖免費(fèi)下載。

2021-03-10 08:00:00 110

110 本文檔的主要內(nèi)容詳細(xì)介紹的是XC7A100T和2CSG324 FPGA可編程邏輯器件芯片的電路原理圖免費(fèi)下載。

2021-03-15 08:00:00 91

91 MCU-串口接收實(shí)現(xiàn)例程倉(cāng)庫(kù):https://gitee.com/ll0_0ll/MCU-UART1.串口接收中斷+空閑中斷空閑中斷是接受數(shù)據(jù)后出現(xiàn)一個(gè)字節(jié)的高電平(空閑)狀態(tài),就會(huì)觸發(fā)空閑中斷

2021-10-25 10:36:04 12

12 ,那么stm32串口是如何實(shí)現(xiàn)接收不定長(zhǎng)度數(shù)據(jù)的呢? 串口接收數(shù)據(jù)一般會(huì)采用串口中斷方式自動(dòng)接收,要想接收不定長(zhǎng)度數(shù)據(jù),就需要讓單片機(jī)在接收完成一幀數(shù)據(jù)之后,自動(dòng)告知系統(tǒng)數(shù)據(jù)已經(jīng)接收完成了,這個(gè)過(guò)程其實(shí)

2021-12-23 19:09:27 26

26 如何來(lái)優(yōu)化?比如四軸飛行器,當(dāng)在不停地獲取姿態(tài)控制方向時(shí),又要去接收串口數(shù)據(jù).答:使用DMA,無(wú)需CPU中斷便能實(shí)現(xiàn)接收串口數(shù)據(jù)1.DMA介紹DMA,全稱為: Direct Memory Ac...

2021-12-24 19:01:52 5

5 在串口+DTC功能時(shí)無(wú)法得知接收一幀數(shù)據(jù)是否接收結(jié)束。本例程配合ELC功能聯(lián)動(dòng)定時(shí)器來(lái)判斷串口接收字節(jié)與字節(jié)之間超時(shí)來(lái)判斷一幀數(shù)據(jù)的接收完成。

2023-05-04 10:50:59 502

502

UART接收數(shù)據(jù)部分是接收另一個(gè)串口設(shè)備發(fā)送的數(shù)據(jù),緩存到接收FIFO中。FIFO快要寫(xiě)滿時(shí),產(chǎn)生中斷通知CPU拿取數(shù)據(jù),實(shí)現(xiàn)串口數(shù)據(jù)的接收。

2023-06-05 15:24:28 2550

2550

如果采用查詢接收方式接受串口數(shù)據(jù),就會(huì)造成接收不及時(shí),還沒(méi)接收完數(shù)據(jù),下一個(gè)數(shù)據(jù)就發(fā)過(guò)來(lái)了,就會(huì)把上一個(gè)數(shù)據(jù)覆蓋了,造成數(shù)據(jù)丟失。

2023-07-21 17:07:24 4566

4566

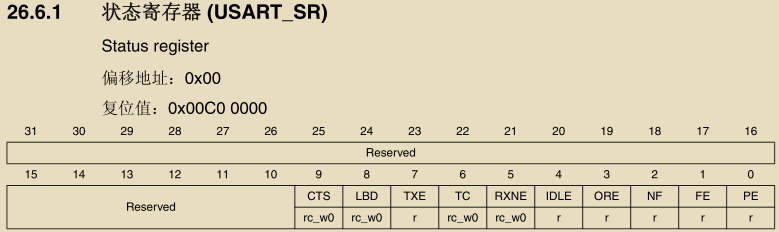

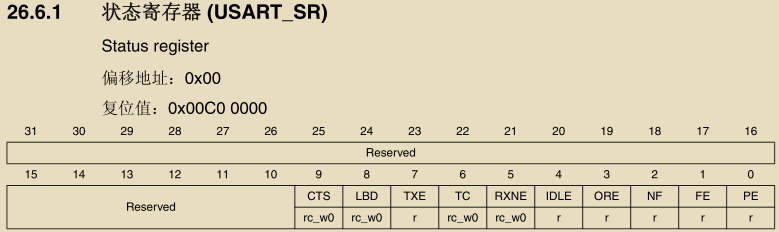

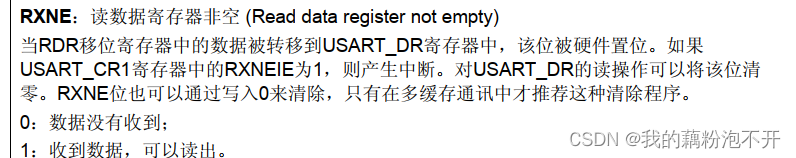

RXNE位的狀態(tài)來(lái)確定數(shù)據(jù)是否接收。 中斷方式就是通過(guò)配置接收輸出控制通道,配置NVIC,在中斷服務(wù)子函數(shù)里進(jìn)行數(shù)據(jù)的接收。 1. 需要更改的地方 既然我們要實(shí)現(xiàn)串口的接收,那么就要配置串口RX引腳,在串口模式中添加USART_Mode_RX模式。 初

2023-11-10 16:20:57 743

743

LabVIEW是一款功能強(qiáng)大的圖形化開(kāi)發(fā)環(huán)境,廣泛應(yīng)用于數(shù)據(jù)采集與處理、自動(dòng)化控制系統(tǒng)等領(lǐng)域。在串口通信應(yīng)用中,如何保證數(shù)據(jù)的穩(wěn)定傳輸是一個(gè)重要的問(wèn)題。本文將詳細(xì)介紹LabVIEW串口接收數(shù)據(jù)

2024-01-08 11:38:41 370

370 基于RA2L1實(shí)現(xiàn)串口DTC數(shù)據(jù)接收

2023-10-10 09:34:34 115

115

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論