1.引言

脈寬調制技術( Pulse Width Modulation, PWM)起源很早,隨著科學技術的發展,廣泛應用在電力、電子、微型計算機、自動控制等多個學科領域。自 80年代初以來,出現了多種 PWM實現方法,歸納起來有自然采樣法、規則采樣法或諧波消去法等等,其中自然采樣法最能真實地反映 PWM的控制思想,效果最好。對于傳統的控制器而言,自然采樣法算法是一個超越方程,需用計算機迭代求解,運算時間較長。如果事先算好存入存儲器,則不僅浪費了存儲空間,而且設計不靈活,精度低。近幾年推出的 DSP處理器雖然在芯片內部整合 PWM發生器模塊,但是這些模塊已經在硅片上實現了,不能夠隨意調整系統參數,缺乏靈活性,不能夠適應復雜的系統設計。

本課題在 FPGA上實現了高精度的PWM發生器,在 Xilinx公司的 Spartan3(-4速度級別 )主流低端 FPGA器件上可以約束到高達 200MHz工作頻率,并支持 14位以上的可調數據位寬。設計全參數化配置,作為可重用模塊能夠嵌入到更大的 FPGA應用系統中,具有較高的工程應用價值 。

2.高精度 PWM發生器的設計與實現

a) RTL級邏輯設計

本設計采用的是自然采樣法產生 PWM波形。首先對實際的模擬電壓值進行離散化,然后將離散化后的調制數據與載波數據進行實時比較,比較結果輸送給死區信號發生器模塊,該模塊將死區保護時間附加到比較結果中,并輸出 PWM波形。其中死區信號發生器的死區時間是可調的,以適應不同場合下的死區時間要求。

本設計主要有三個主要模塊組成,分別是載波發生器、時序等于比較器和死區保護發生器。設模塊位寬為 W,現分別介紹設計要點如下。

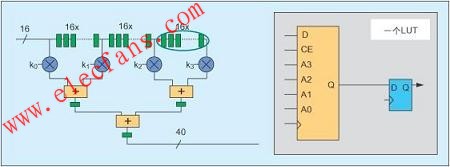

1、載波發生器:設計采用了鋸齒波作為 PWM載波。從電路的角度來講設計鋸齒波發生器會比設計三角波發生器使用更少的組合邏輯資源,從而有利于時序約束到較高的頻率。為減少寬位寬的計數器的進位鏈長度,采用 Prescaled結構的計數器,將其拆分為 2位計數器和(W-2)位計數器,

減少了組合邏輯延遲。在優化階段通過設定 MultiCycle約束,還可以進一步提高器件工作速度。

2、時序等于比較器:該比較器不同于普通的純組合邏輯等于比較器。通過例化 FPGA的底層子元件,在該等于比較器內部插入了一級 D觸發器,大大減少了由于數據位寬增加而增加組合邏輯延遲。由于存在一級寄存器,比較結果需要延遲一個時鐘周期才能夠輸出。對于 PWM調制這種應用場合,高精度情況下可以接受比較結果的一個時鐘周期延遲,因此使用該比較器造成的比較誤差非常小。

3、死區保護發生器:根據給定的死區長度數據,將輸入的 PX信號輸出為 PH和 PL信號,并在 PH和 PL數據的變沿時刻插入死區保護(同時置為高電平)。具體方式是通過上升計數器和下降計數器來實現的:上橋臂控制信號 PH在 PX信號為 1并且上升計數器計數完成后才置 1,此時上橋臂開通;下橋臂控制信號 PL在 PX信號為 0并且下降計數器計數完成后才置 1,此時下橋臂開通。這個機制能夠保證上下橋臂不會同時導通。

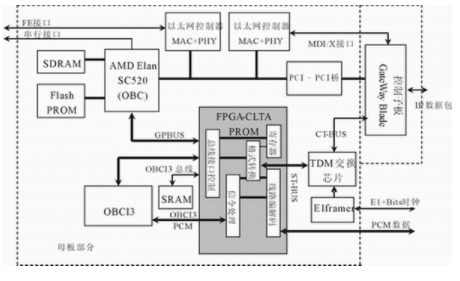

為了保證時序收斂,根據實際情況,考慮到死區保護發生器模塊的任務是插入保護時間,因此工作速度可以較低,故工作頻率設計為 100MHz;其余兩個模塊的工作頻率設計為 200MHz。如圖 2-1所示,跨越異步時鐘域的信號線只有 PX。由于這兩個時鐘域同相且具有二分頻關系,只需要對比較器輸出信號進行二倍脈沖展寬即可。

由于死區時間在不同的應用場合下也是不同的,且一般都在 1us以上。因此根據設計的技術指標,設計了一個 6位寄存器保存死區寬度數據,并在設計內部對輸入數據進行重新移位,以適應死區時間的區間可調特性。據設計測算,模塊工作頻率在 100MHz下,死區時間可以在 2.5us到 5us區間內實現 64檔調整。

b)結構優化實現

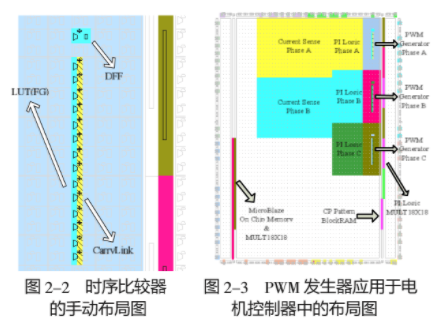

經過 RTL級設計之后,進行軟件默認的綜合和布局布線并不能夠收斂到 200MHz。根據靜態時序分析報告,發現關鍵路徑仍存在于比較器的組合邏輯上。根據路徑分析,雖然比較器進行了優化設計后減小了組合邏輯本身的延遲,但是軟件自動布局布線之后的網線延遲很大,沒有達到預期的優化效果。因此對該部分邏輯采用 Floorplanner工具進行手動布局,如圖 2-2所示。

圖 2-2中 DFF為 D觸發器,實現了中間結果的一個時鐘周期寄存; LUT為查找表,在此處用法為 FG(Function Generator,功能發生器 ),比較器的內含邏輯即保存在查找表中; Carrylink為進位鏈,布局到 FPGA中的直接進位鏈上,這樣進位延遲最小。通過手動布局約束,可以讓軟件在自動布局布線過程中預先分配好這些關鍵邏輯的布局資源,減小關鍵路徑上的連線延遲。

圖 2-3是本 PWM發生器應用在一個三相步進電動驅動器中的布局實例。該實例例化了三個本 PWM發生器以驅動三相橋臂,參見圖 2-2右上部分。通過該實例,充分說明了只要手動布局關鍵資源,模塊可以以同樣的優化結構復用到更大的 FPGA應用當中去。

經過 Floorplanner布局之后,時序收斂。靜態時序分析表明該模塊的最大周期時間為 4.642ns(折算過來的頻率達到 215MHz),其中 3.409ns為邏輯延遲 , 1.233ns為布線延遲,邏輯延遲占到了總延遲的 73.4%,達到這個優化效果是非常令人滿意的。

進行布局布線后仿真時發現設計有些情況下會出現模塊 reset失敗的現象。經過分析,發現是異步重置的 recovery time和 removal time無法滿足某些 200MHz工作的 D觸發器的要求。這是因為本模塊都是采用的異步 reset,而異步 reset網絡在 FPGA內部是唯一的,具有非常大的全局扇出,對于大型設計很容易造成數納秒級別的傳輸延遲。而 200MHz的 D觸發器工作周期才只有 5納秒,很容易造成時序錯誤。根據這一情況,對進行本模塊的異步 reset信號進行了本地同步化,將異步 reset信號同步到三個完全相同的 D觸發器內部,再分派給三個子模塊,有效的減低了扇出系數。修改后的設計就沒有再出現過 reset失敗的現象了。

3.設計的仿真與驗證本設計采用 ModelSim軟件進行仿真驗證。通過功能仿真驗證設計的正確性,通過布局布線后仿真驗證實際工作的正確性和穩定性。

圖 3-1是 PWM發生器的功能仿真波形。圖中的 ph和 pl兩根信號線就是 PWM發生器的輸出信號。該仿真采用了 14位數據寬度,其 PWM輸出的載波頻率為 200MHz / 214 = 12.2KHz。死區保護時間在 2.5us~5us時間內可調。在給定 pwm寄存器和 deadprotect寄存器的輸入后,該發生器能夠正確地產生指定的 PWM波形輸出。使用仿真波形圖中的游標進行測算,所有波形數據符合設計預期。功能仿真通過。

3-2是 PWM發生器的布局布線后仿真波形圖。根據同樣的方法,測算在不同輸入波形的寬度,并計算驗證,所有波形數據符合設計預期。布局布線后仿真通過。

本設計最終占用 FPGA資源如表 3-1所示。可見本設計經過優化后,綜合后工作速度高,資源占用非常小。參數化的設計,可重用性也非常好。

4.結束語

本文提出了一種在 FPGA器件上實現高精度 PWM發生器的設計方法 [4]。首先根據 PWM調制原理選擇了其中效果最好的采用自然采樣法調制 PWM信號。根據自然采樣法的思想,將設計分拆為三個子模塊,每個子模塊都相對功能簡單,并且易于設計和優化。考慮到以后工程應用的移植性,設計采用了參數化方式,主要的數據位寬和參數都可以直接在常數聲明文件中進行配置。在每一個子模塊的設計工程中,都分為了 RTL功能設計和結構優化兩部分——RTL功能設計實現模塊功能,結構優化是在功能不變的前提下,通過等效結構變換減小設計的組合邏輯延遲,避免高扇出網絡,提高設計穩定性。在結構優化中,還解決了 200MHz以上高速設計中異步 reset信號存在的潛在不穩定性問題。完成了設計和優化工序后,對設計進行了功能仿真和布局布線后仿真,經過人工計算比對, PWM發生器的輸出完全符合預期,保證了之前的設計工作的正確性。最后給出了 FPGA資源占用表格,供重用該模塊評估時使用。

本文作者創新點:在比較器部分的設計當中,創造性地設計了內部帶有一級 D觸發器的等于比較器,并給出了最佳的 Floorplanner布局圖,解決了高位寬下過長的進位鏈帶來的大延遲的問題,在控制精度和器件工作頻率之間找到了一個兼顧二者的契合點。采用了這種類型的比較器之后,本 PWM發生器可以在 200MHz的工作頻率下支持非常高的數據位寬,提供非常精確的 PWM調制波形。

責任編輯:gt

電子發燒友App

電子發燒友App

評論