1 引言

雷達(dá)高度表在飛機(jī)和導(dǎo)彈等的慣性導(dǎo)航和地形匹配導(dǎo)航中有著廣泛的應(yīng)用。雷達(dá)高度表是雷達(dá)向地面發(fā)射無線電電波,根據(jù)其反射回波的滯后時(shí)間來測(cè)量距離,用來取得距離地面的相對(duì)高度的一種裝置。另外通過對(duì)雷達(dá)回波的分析處理可以了解地形情況。由于機(jī)載彈載雷達(dá)的外場(chǎng)試驗(yàn)組織實(shí)施難度大,試驗(yàn)費(fèi)用昂貴,而且隨著對(duì)雷達(dá)技戰(zhàn)術(shù)指標(biāo)要求的提高,對(duì)雷達(dá)測(cè)試設(shè)備提出了更高的要求。例如要求系統(tǒng)的數(shù)字化小型化,要求系統(tǒng)具有獨(dú)立性和靈活性等,而且為了不丟失數(shù)據(jù),測(cè)試設(shè)備應(yīng)當(dāng)能夠連續(xù)長(zhǎng)時(shí)間的紀(jì)錄雷達(dá)的狀態(tài)和信號(hào)。

CPLD(復(fù)雜可編程邏輯器件)具有可編程性和實(shí)現(xiàn)方案容易改動(dòng)的特點(diǎn),可以極大的降低系統(tǒng)開發(fā)成本和縮短開發(fā)周期,而且易于實(shí)現(xiàn)系統(tǒng)的集成化小型化。Altera公司的CPLD器件具有布線能力強(qiáng),延遲可預(yù)測(cè)等優(yōu)點(diǎn),適合于完成各類算法和組合邏輯。其MAX系列器件性價(jià)比高,傳播延遲小,邏輯資源豐富,電路設(shè)計(jì)簡(jiǎn)單等特點(diǎn)使其特別適合用作邏輯控制電路控制。硬盤作為存儲(chǔ)介質(zhì)具有很高的容量?jī)r(jià)格比,且易于擴(kuò)充,數(shù)據(jù)利于轉(zhuǎn)存和后期數(shù)字處理。普通IDE硬盤受限于總線速率,其持續(xù)數(shù)據(jù)傳輸速率在15MBps左右。目前15000轉(zhuǎn)的小型計(jì)算機(jī)系統(tǒng)接口SCSI(Small Computer System Interface)硬盤,總線數(shù)據(jù)傳輸速率為80-320MBps,持續(xù)數(shù)據(jù)傳輸速率大于40MBps,性能遠(yuǎn)遠(yuǎn)高于IDE硬盤。鑒于此,雷達(dá)高度表數(shù)據(jù)采集存儲(chǔ)系統(tǒng)設(shè)計(jì)采用可編程邏輯器件和總線技術(shù),利用高速SCSI硬盤作存儲(chǔ)介質(zhì),并且脫離微機(jī)平臺(tái),實(shí)現(xiàn)了雷達(dá)信號(hào)的靈活采集和連續(xù)存儲(chǔ)。

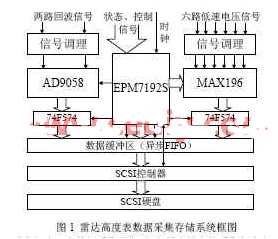

2 系統(tǒng)結(jié)構(gòu)

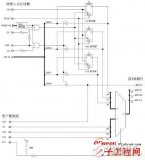

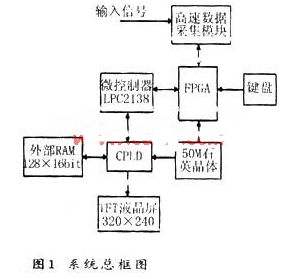

整個(gè)系統(tǒng)結(jié)構(gòu)如圖1所示。系統(tǒng)需要記錄兩路雷達(dá)脈沖回波信號(hào),六路雷達(dá)狀態(tài)信號(hào)(為緩變電壓信號(hào),輸入幅度不同),以及雷達(dá)系統(tǒng)同步脈沖和雷達(dá)信號(hào)波門之間的時(shí)間間隔。要求采集脈沖回波信號(hào)時(shí)采集起點(diǎn)可選為信號(hào)波門前沿或同步脈沖后延遲一定時(shí)間,且延遲時(shí)間手動(dòng)可調(diào)(調(diào)節(jié)范圍5~200us),采樣頻率可調(diào)。要求存儲(chǔ)數(shù)據(jù)具有固定的幀結(jié)構(gòu),利于事后分析處理。

兩個(gè)同步脈沖之間為一個(gè)數(shù)據(jù)采集周期:根據(jù)用戶設(shè)定的采集起點(diǎn)和采樣頻率采集一定點(diǎn)數(shù)的回波信號(hào),計(jì)算目標(biāo)距離,采集六路中速電壓,將上述數(shù)據(jù)按照一定的格式打包,加上幀標(biāo)志后組成一幀數(shù)據(jù),送入數(shù)據(jù)緩沖區(qū),等待SCSI控制卡將數(shù)據(jù)寫入SCSI硬盤。

3 系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)

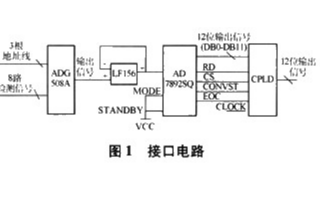

3.1數(shù)據(jù)采集電路

數(shù)據(jù)采集電路分高速和低速兩個(gè)部分。兩路雷達(dá)回波信號(hào)采用高速數(shù)據(jù)采集電路,模數(shù)轉(zhuǎn)換器采用美國(guó)AD公司生產(chǎn)的AD9058雙路模數(shù)轉(zhuǎn)換器(ADC)。AD9058在片內(nèi)集成了兩個(gè)獨(dú)立的高性能并行8位ADC,其單路最高轉(zhuǎn)換速率可達(dá)50MSps,模擬帶寬達(dá)175MHz;每個(gè)ADC有單獨(dú)時(shí)鐘及參考電壓輸入;AD9058本身帶有高穩(wěn)定的2V電壓參考源,可大大簡(jiǎn)化電路設(shè)計(jì);其數(shù)字地和模擬地分開,有利于設(shè)計(jì)優(yōu)秀的接地方案以消除干擾。

由于低速電壓有六路需要采集而且輸入幅度不同,但是要求的采樣率較低,只需每個(gè)采集周期采樣一次即可,所以低速數(shù)據(jù)采集電路采用了MAXIM公司的MAX196。MAX196為6路12位可編程ADC,每路模擬輸入幅度程序可控,最高輸入時(shí)鐘2MHz,滿足系統(tǒng)要求。

為產(chǎn)生高精度、高穩(wěn)定度、低噪聲、低抖動(dòng)的系統(tǒng)時(shí)鐘,時(shí)鐘分系統(tǒng)采用高精度低相噪的溫補(bǔ)、時(shí)鐘分路器、分頻器以及ET轉(zhuǎn)換(PECL電平到TTL電平的轉(zhuǎn)換)和TE轉(zhuǎn)換(TTL電平到PECL電平的轉(zhuǎn)換)來設(shè)計(jì)完成。高精度晶振作為時(shí)鐘源,輸出的純凈時(shí)鐘信號(hào)送到高精度單端轉(zhuǎn)差分時(shí)鐘芯片,輸出PECL差分信號(hào)經(jīng)分頻和變換后用作高速采集電路的采樣時(shí)鐘,時(shí)間延時(shí)的計(jì)數(shù)時(shí)鐘。PECL信號(hào)和器件在良好匹配的情況下其信號(hào)速度、對(duì)外輻射、器件延遲以及輸出信號(hào)抖動(dòng)有著TTL和CMOS器件所無法比擬的優(yōu)勢(shì),是設(shè)計(jì)高速數(shù)據(jù)采集系統(tǒng)時(shí)鐘電路的理想選擇[3]。

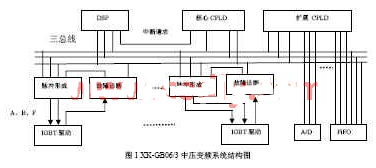

3.2邏輯控制電路

邏輯控制需要使用外部提供的同步和波門信號(hào),這兩個(gè)信號(hào)的優(yōu)劣直接關(guān)系到系統(tǒng)邏輯的正確性和時(shí)間延時(shí)計(jì)數(shù)的準(zhǔn)確性。對(duì)同步、波門信號(hào)調(diào)理的關(guān)鍵是將十幾伏的模擬脈沖衰減到5伏以下,并保證衰減器與輸入阻抗的匹配,避免信號(hào)反射。信號(hào)衰減后,送入高速比較器,獲得TTL脈沖信號(hào)。由于采用高速比較器,調(diào)理后信號(hào)的上升和下降時(shí)間要比調(diào)理前模擬脈沖信號(hào)小得多,小于4ns。信號(hào)上升和下降沿的改善提高了CPLD的對(duì)信號(hào)脈寬、脈沖間隔的測(cè)量精度,為AD轉(zhuǎn)換和時(shí)間延時(shí)計(jì)數(shù)提供了一個(gè)準(zhǔn)確的時(shí)間起點(diǎn)。

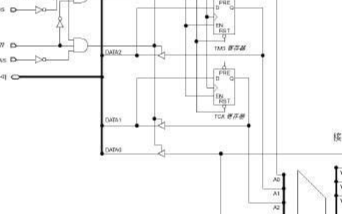

在本系統(tǒng)中,ADC采集結(jié)果緩存采用多體存儲(chǔ)結(jié)構(gòu),將存儲(chǔ)器芯片分為多個(gè)體,各體之間并行工作,從而滿足系統(tǒng)對(duì)數(shù)據(jù)存儲(chǔ)速度的要求。另外,SCSI硬盤的直接讀寫主要有SCSI硬盤適配器通過DMA方式法完成。由于SCSI硬盤在尋找扇區(qū)的過程中有2~9ms的間隔,在這段時(shí)間內(nèi)不能對(duì)SCSI硬盤進(jìn)行讀寫。為了保證數(shù)據(jù)的連續(xù)計(jì)錄和回放,必須有足夠深度的數(shù)據(jù)緩存,因此在設(shè)計(jì)中采用兩級(jí)緩存方式。在系統(tǒng)中,由AD轉(zhuǎn)換電路送出的兩路高速數(shù)據(jù)流,被存入到兩個(gè)緩沖鎖存器中,接著又被并行寫入到兩個(gè)高速異步FIFO中,這樣FIFO的平均寫周期為AD轉(zhuǎn)換電路數(shù)據(jù)更新周期的1/2,從而可使用相對(duì)低速的芯片來滿足系統(tǒng)要求。另外多路模擬信號(hào)采集后,不同速率的數(shù)據(jù)流要按一定順序,一定格式打包成幀,進(jìn)行SCSI硬盤存儲(chǔ),同時(shí)保持?jǐn)?shù)據(jù)流的連貫。所有高速、低速的數(shù)據(jù)流要通過一個(gè)SCSI控制器進(jìn)入SCSI硬盤或硬盤陣列大量數(shù)據(jù)存入硬盤,為了便于軟件處理,數(shù)據(jù)應(yīng)當(dāng)有一定格式,組成幀結(jié)構(gòu)。因此采用時(shí)序和控制邏輯電路協(xié)調(diào)多路模擬信號(hào)采集,進(jìn)行總線隔離控制、FIFO讀寫控制等。

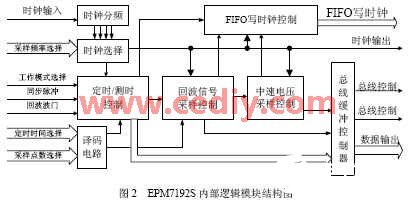

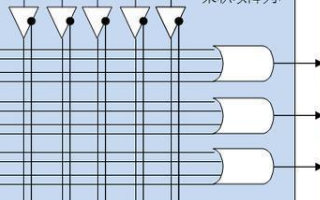

由于本系統(tǒng)控制邏輯的復(fù)雜性和使用的輸入輸出管腳較多,因此選擇了Altera公司MAX7000系列中容量較大的EPM7192SQC160[4]。設(shè)計(jì)采用模塊化設(shè)計(jì),每一個(gè)子控制模塊生成子模塊后組成整個(gè)完整的系統(tǒng)。這種設(shè)計(jì)方法極大地提高了設(shè)計(jì)效率,并且有利于閱讀和修改。控制核心EPM7192S內(nèi)部邏輯模塊結(jié)構(gòu)劃分如圖2所示。

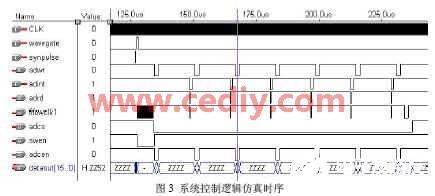

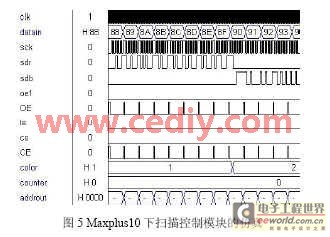

其中定時(shí)/測(cè)時(shí)控制模塊完成采集起點(diǎn)控制和時(shí)間間隔記錄;回波信號(hào)采樣控制模塊完成按照用戶設(shè)定的采集起始點(diǎn)、采樣頻率和采樣點(diǎn)數(shù)采集回波信號(hào);中速電壓采樣控制模塊完成每個(gè)采集周期內(nèi)對(duì)MAX196寫入6次控制字和讀取數(shù)據(jù)轉(zhuǎn)換的數(shù)據(jù);FIFO寫時(shí)鐘控制模塊提供數(shù)據(jù)存入緩沖區(qū)(異步FIFO)所需的寫入時(shí)鐘;總線緩沖控制器完成CPLD,高速A/D,低速A/D,F(xiàn)IFO間的數(shù)據(jù)交換。設(shè)計(jì)時(shí)采用同步電路設(shè)計(jì),使用一個(gè)時(shí)鐘作為全局時(shí)鐘,最后實(shí)現(xiàn)的系統(tǒng)控制邏輯時(shí)序波形如圖4所示。圖中僅列出了完成一幀數(shù)據(jù)采集存儲(chǔ)所需的幾路關(guān)鍵信號(hào):fifowclk1為異步FIFO的寫信號(hào),swen為高速A/D數(shù)據(jù)鎖存器的輸出使能信號(hào),adcen是中速A/D控制字的輸出使能信號(hào)。

3.3軟件設(shè)計(jì)

事后分析軟件主要負(fù)責(zé)將存放在SCSI硬盤中的測(cè)量數(shù)據(jù)通過SCSI轉(zhuǎn)接卡,利用動(dòng)態(tài)鏈接庫(kù)轉(zhuǎn)存到微機(jī)內(nèi)存,顯示并分析測(cè)量數(shù)據(jù)。事后分析軟件首先尋找到存儲(chǔ)數(shù)據(jù)的SCSI硬盤,依次讀取所有存儲(chǔ)數(shù)據(jù)文件屬性,包括文件大小、存儲(chǔ)時(shí)間、在SCSI硬盤中的初始扇區(qū)和終止扇區(qū)以及文件句柄等,并將采集數(shù)據(jù)文件名列出,供用戶選擇。用戶選出要顯示分析的文件,事后分析程序從中讀取一定數(shù)量的測(cè)量數(shù)據(jù)到緩沖區(qū),并連續(xù)尋找兩個(gè)數(shù)據(jù)幀頭,將兩個(gè)幀頭之間的數(shù)據(jù)經(jīng)過一定處理后顯示出兩路雷達(dá)回波波形、同步信號(hào)和波門信號(hào)之間的時(shí)間間隔、6路中速電壓值以及采集時(shí)設(shè)置的參數(shù)。

4 系統(tǒng)測(cè)試與應(yīng)用

系統(tǒng)性能測(cè)試主要分兩部分。首先是對(duì)多路模擬信號(hào)數(shù)據(jù)采集的測(cè)試,包括轉(zhuǎn)換有效位數(shù)、諧波失真等。其次是測(cè)試SCSI硬盤數(shù)據(jù)存儲(chǔ)的正確性和持續(xù)存儲(chǔ)速度。

模數(shù)轉(zhuǎn)換性能測(cè)試是對(duì)系統(tǒng)的靜態(tài)和動(dòng)態(tài)性能的測(cè)試,主要包括信噪比、總諧波失真、信噪失真比和有效位數(shù)的測(cè)試。實(shí)際的ADC存在噪聲和失真,從而影響了ADC的實(shí)際分辨率,降低了ADC的位數(shù),ADC實(shí)際可達(dá)到的位數(shù)稱為有效位數(shù)[3]。采用FFT相關(guān)頻譜分析方法對(duì)本系統(tǒng)進(jìn)行了測(cè)試。選擇DOFED &SCHWARZ DIGITALUHR CLOCK 銫原子時(shí)鐘輸出5MHz純正正弦信號(hào)作為模擬輸入,采樣時(shí)鐘來自系統(tǒng)板上晶體,對(duì)分辨率八位的ADC,采樣的點(diǎn)數(shù)選擇為1024點(diǎn),采樣頻率是40MHz,頻譜分辨率為0.125MHz。故此時(shí)滿足相關(guān)采樣的條件,采樣為相關(guān)采樣,根據(jù)采集數(shù)據(jù)和相關(guān)公式計(jì)算,最后測(cè)試結(jié)果表明ADC有效位為7.16bit,諧波失真約為44.92dB。

對(duì)高速數(shù)據(jù)流直接SCSI硬盤存儲(chǔ)性能測(cè)試使用的是Seagate公司生產(chǎn)的ST336752LW型硬盤。測(cè)試時(shí),在連續(xù)、高速存儲(chǔ)過程中,監(jiān)測(cè)異步FIFO的空滿標(biāo)志。若FIFO出現(xiàn)空標(biāo)志有效的狀態(tài),表明SCSI硬盤持續(xù)存儲(chǔ)速度高于數(shù)據(jù)流的速度;若FIFO出現(xiàn)滿標(biāo)志有效的狀態(tài),則表明數(shù)據(jù)流的速度高于SCSI硬盤持續(xù)存儲(chǔ)速度,即表明系統(tǒng)不具備該速度的持續(xù)存儲(chǔ)能力。測(cè)試表明,在單個(gè)SCSI硬盤、數(shù)據(jù)流速度在30MBps的情況下,沒有出現(xiàn)FIFO滿標(biāo)志有效的狀態(tài),系統(tǒng)具備最高36MBps持續(xù)存儲(chǔ)能力。另外,對(duì)確知數(shù)據(jù)流的存儲(chǔ)數(shù)據(jù)進(jìn)行了對(duì)比測(cè)試,通過近2G字節(jié)數(shù)據(jù)的比對(duì),沒有發(fā)現(xiàn)錯(cuò)誤的數(shù)據(jù),表明該系統(tǒng)的高速持續(xù)存儲(chǔ)具有很高的可靠性。

本系統(tǒng)先后應(yīng)用于多種雷達(dá)系統(tǒng)測(cè)試分析和外場(chǎng)試驗(yàn),有效地記錄和分析了雷達(dá)系統(tǒng)的動(dòng)態(tài)特性、目標(biāo)回波特性及干擾特性。特別是在機(jī)載雷達(dá)外場(chǎng)試驗(yàn)和雷達(dá)抗干擾試驗(yàn)中,獲得大量以往難以連續(xù)記錄的雷達(dá)中頻回波信號(hào)。并且大大提高試驗(yàn)測(cè)試效率,節(jié)省大量的實(shí)驗(yàn)時(shí)間和費(fèi)用,具有很高的經(jīng)濟(jì)效益。本系統(tǒng)采用模塊化設(shè)計(jì),采用CPLD器件和總線技術(shù),縮短了開發(fā)周期,提高了系統(tǒng)集成度和穩(wěn)定性。系統(tǒng)采樣點(diǎn)數(shù)、采樣頻率、采樣起始時(shí)刻可以靈活設(shè)置,可以脫離微機(jī)環(huán)境獨(dú)立使用,能夠廣泛地應(yīng)用于各種雷達(dá)測(cè)試、雷達(dá)目標(biāo)和環(huán)境特性分析、雷達(dá)外場(chǎng)試驗(yàn)和驗(yàn)收鑒定。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論