本帖最后由 發燒友LV 于 2014-12-29 20:13 編輯

在FPGA中實現PID算法,面臨著小數的計算,請問大家一般是怎么處理的?

2014-12-03 21:59:29

振蕩器的設計中,必須采用至少兩個極點,一個TL電路有兩個極點,從而它可提供180°的相移。但是在這里不考慮LC和LR振蕩器,因為低頻電感很貴、很笨重、體積又很大,所以是不理想的。在超出了電壓反饋運算放大器

2015-01-05 10:15:44

出現。 Plz幫助我解決這些問題,以便我盡快結束這部分...1.在頻率穩定性,負載電容和負載電流方面,xilinx spartan-6 FPGA的振蕩器要求/規格有哪些。我試過但未找到XILINX評估套件中使

2019-06-12 14:21:39

晶體振蕩器壓控振蕩器(VCXO) 能夠根據輸入電壓改變頻率 在指定電壓范圍內具有指定的頻率范圍 適合鎖相環應用溫度補償振蕩器(TCXO) 用于補償溫度變化 利用補償網絡來實現此功能 通常包含熱敏電阻和變抗器

2018-11-01 15:41:19

尊敬的技術支持專家,

我在研究你的 KBA237926 文章,它說傳感器 AR1335 使用板載振蕩器作為輸入時鐘。

CAN 請您告訴我振蕩器值? 是25MHZ嗎?

2024-02-26 07:02:32

`CRO或陶瓷諧振器系列振蕩器以提供出色的相位噪聲性能而聞名。 它們在范圍內可用從400 MHz到8 GHz的任何頻率,同時提供非常低的調諧靈敏度以優化性能。 獨特的構造CRO振蕩器及其實現低調

2021-04-03 16:50:57

`DRO系列壓控振蕩器是一種基本的窄帶信號源,它利用高Q介質諧振器實現了最佳的相位噪聲性能。目前,DRO VCO解決方案適用于在7至14 GHz范圍內工作的頻率。該可定制的超低噪聲振蕩器系列可提供

2021-04-03 16:55:11

【作者】:范樟;林偉;黃世震;【來源】:《電聲技術》2010年02期【摘要】:基于N阱0.5μmDPTMCMOS工藝,完成了D類音頻功放中電流控制振蕩器的設計。首先分析了電流控制振蕩器的工作原理

2010-04-22 11:28:36

概述:MAX7378是MAXIM公司生產的一款帶有復位的雙速率硅振蕩器,是陶瓷諧振器、晶體、晶體振蕩器模塊和分立復位電路的替代品。 MAX7378為3V、3.3V、5V應用中的微控制器提供主時鐘源

2021-05-17 06:57:10

振蕩器(GPSDO)可作為堅固的軍用或商用頻率參考,可在固定或移動平臺上實現銫原子鐘或Stratum I性能。 產品名稱:紀律振蕩器產品型號: GPSDO紀律振蕩器 GPSDO紀律振蕩器特征頻率輸出

2019-06-23 17:05:13

原因 在實際應用中,經常出現由于晶體振蕩器在運行中失去 作用,造成微處理器的時鐘源丟失,從而出現死機的現象,導致系統出錯。嚴重時,由于系統的死機造成監控失效, 導致無法挽回的損失!目的STM32作為

2021-08-16 06:09:41

嗨,我想知道其他人是否遇到了同樣的問題。在一個小型測試系統中,我使用12MHz的晶體,用適當的電容器作為外部振蕩器,用18F25K50芯片。使用XS振蕩器設置,振蕩器將無法啟動。我嘗試了中等

2020-04-26 13:59:16

”處理。二.擾碼的原理偽隨機序列是由一個標準的偽隨機序列發生器生成的,其中“0”與“1”出現的概率接近50%。用偽隨機序列對輸入的傳送碼流進行擾亂后,無論原始傳送碼流是何種分布,擾亂后的數據碼流中“0

2019-12-18 09:37:35

我想完成三種偽隨機碼發生器的設計,以7級m序列發生器為例介紹,而M序列發生器只是比m序列多一個全零狀態,Gold序列是由一對m序列模2加得到的。想請教高手,后兩種如何在m序列發生器的基礎上實現呢。 如果仿真波形想顯示起碼兩個周期的序列,該如何設置時鐘呢?謝謝指教!感激不盡~~!

2009-04-01 10:26:41

和接收設備的基本部件。隨著電子技術的迅速發展,振蕩器的用途也越來越廣泛,但是與普通晶振價格想 比,價格往往高于普通晶振幾倍。例如在無線電測量儀器中,它產生各種頻段的正弦信號電壓:在熱加工、熱處理、超聲波

2018-07-21 22:31:10

的能量來自彈簧。鐘擺在每次敲鐘時都得到一點推力,以彌補因摩擦而失去的能量。振蕩器在電路中能起到的作用振蕩器是用來產生重復電子信號(通常是正弦波或方波)的電子元件。其構成的電路叫振蕩電路。低頻振蕩器是指

2018-04-27 17:11:03

的頻率上不會發生振蕩。但是,在調諧頻率下,任何負反饋都可以忽略不計,從而允許由放大設備創建的正反饋路徑占主導地位,從而在一個單一頻率上產生振蕩(不同于維恩橋振蕩器,后者可以在較大的頻率范圍內進行調整

2020-09-15 10:04:18

為什么VC707中的振蕩器(系統clk)由2.5V供電? FPGA不包含任何HR IO。

2019-10-23 09:36:22

的不足,同時也方便在現場可編程門陣列(FPGA)中增加一些其他相關的應用功能,因此在FPGA中實現CVSD語音編譯碼調制功能的前景將是非常廣闊的。這里將詳細介紹什么是CVSD?其算法分析如何在FPGA中實現?

2019-08-07 07:04:27

我有一位客戶詢問有關在 RT1051 中實現外部 24Mhz 時鐘振蕩器的問題。他們計劃通過將現有的外部 48Mhz 振蕩器分頻為 24Mhz 并使用 RT1051 的外部時鐘振蕩器輸入功能來為

2023-05-18 06:15:20

最近在學習振蕩器,但是對于振蕩器里面各個參數是如何準確計算出來很有疑問,參考IEEE里面的論文,里面的內容在圖片上,我想請教各位公式部分是怎么得出來的,以及振蕩器設計的計算過程有什么需要注意的嗎

2016-03-17 14:36:36

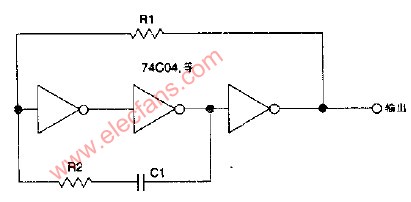

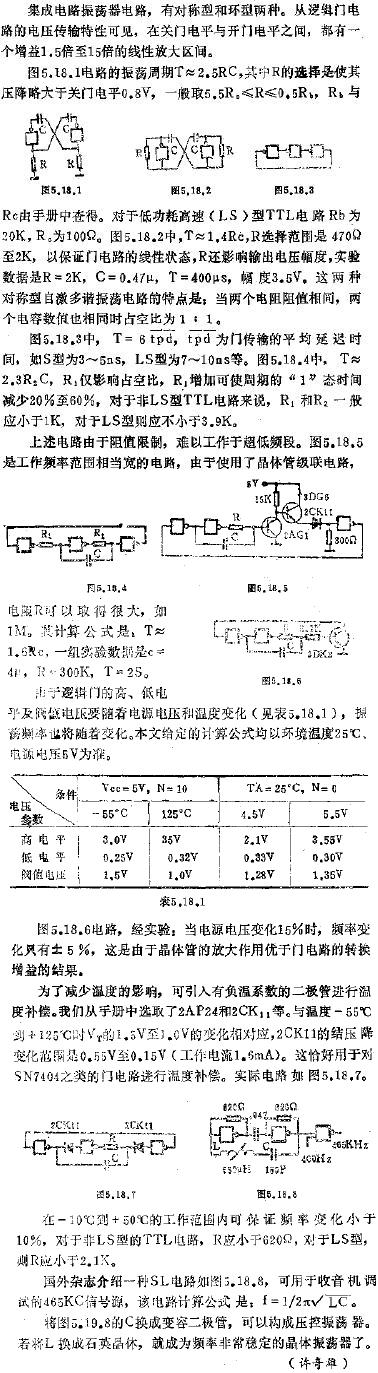

在此cmos電路構成的振蕩器中,假設最開始輸入為高電平,一級反相器輸出為低電平,再經一級反相器輸出為高電平,這個電路是如何實現振蕩原理的?兩個電阻的關系是如何確立的,電容在該電路中充當什么作用?

2024-01-26 17:59:10

將電源線插頭插入振蕩器對應的插孔內,然后將插頭插入電源插座中,此時,電源接通,如需要水平振蕩則打開水平振蕩開關;如需要垂直振蕩則打開垂直振蕩開關。振蕩速度可根據您的要求調整速度旋鈕。

2019-10-14 09:11:20

自適應光學SPGD控制算法對偽隨機序列有哪些要求?偽隨機序列的生成方法有哪幾種?基于FPGA的偽隨機序列有哪些應用?

2021-05-08 06:19:47

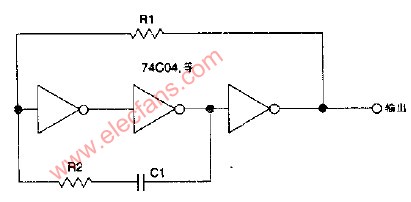

正余弦信號的實現過程,給出了在FPGA 中設計數控振蕩器的頂層電路結構,并根據算法特點在設計中引入流水線結構設計。在正交數字混頻器中,采用數字頻率合成技術,可以將數字處理延續到正交調制之后或正交解調

2021-07-15 08:00:00

求一種基于FPGA的任意時延偽碼序列產生方法?

2021-04-08 06:52:39

基于FPGA的壓控振蕩器是否能夠實現,相關文獻或論文有沒有,求大神指導

2014-12-02 14:09:21

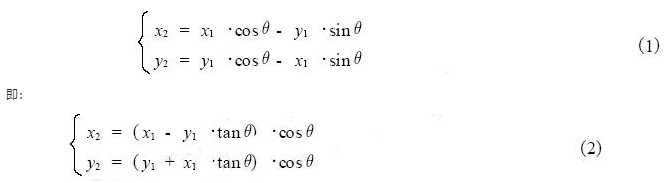

的CORDIC旋轉系數都存儲在ROM中,通過地址產生器的控制實現序列與相應的旋轉因子的復乘運算。與傳統CORDIC算法相比去掉了預旋轉角與已旋轉角之差的計算來確定下一次旋轉方向的結構,不但增加了系數寄存器

2011-07-11 21:32:29

1、引言 隨著現代高速處理器的迅猛發展,圖像處理技術也日益成熟。其中,移動目標的視頻檢測與跟蹤是圖像處理、分析應用的一個重要領域,是當前相關領域的研究前沿。移動目標視頻檢測與跟蹤技術,在機器人

2019-06-26 06:09:46

1 基于 DSP 的數字振蕩器的設計與實現 基于 DSP 的數字振蕩器的設計與實現 黃福瑩 陳華 徐金隆 廣西大學計算機與電子信息學院 南寧 530004 摘要 摘要 本文闡述了一種基于 DSP

2021-08-09 06:51:03

目標跟蹤算法作為一種有著非常廣泛的應用的算法,在航空航天、智能交通、智能設備等領域有著非常廣泛的應用。本系列博客將教大家在410c開發板上基于linux操作系統環境,采用QT+Opencv來實現

2018-09-21 10:42:31

對于碼分多址的擴頻通信方式而言,只有當接收端本地偽碼與發端偽碼處于相同相位狀態時,有用的信息才能被解出。因此,擴頻序列相位的捕獲與跟蹤是擴頻通信系統的關鍵,而偽碼序列相位的捕獲尤為重要。滑動相關法是常用的方法之一。為什么要應用FPGA ?

2019-08-08 06:01:26

本文介紹如何用FPGA(現場可編程邏輯門陣列)和SRAM(靜態隨機存儲器)實現高精度數控振蕩器。

2021-05-08 09:30:28

我正在開發代碼(PIC32 MZ),以便在一系列開發PCB上運行。有些有12MHz的振蕩器和24MHz的振蕩器。有人能建議一種代碼檢測方法嗎?

2019-10-28 13:56:41

隨著科學技術的發展,越來越多的振蕩器和天線集成在一起。小型化設計通常要求將多種器件集成到普通、緊湊的結構中。為了評價沒有輻射特性干擾下的有源天線振蕩特性,經過校準的傳感器被放置在天線的輻射邊沿,該天線具有最高電壓。正如所示,在實現振蕩頻率調整后,滿足了目標設計指標。

2019-08-13 06:01:16

截短Reed-Solomon碼譯碼器的FPGA實現提出了一種改進的BM算法,并在此基礎上提出了一種大量采用并行結構的截短RS碼譯碼器的實現方式。驗證表明,該算法能顯著提高基于FPGA的RS譯碼器

2009-09-19 09:39:43

怎樣去設計一款壓控振蕩器?壓控振蕩器在射頻通信電路中的應用是什么?

2021-06-04 07:17:00

本文設計了可應用于DRM/DAB接收機的壓控振蕩器,并對普通的電路結構進行改進,以降低功耗和相位噪聲,經仿真分析,性能滿足設計要求,但仍有些需要改進的地方,在后續設計中應通過進一步優化可變電容的偏置電壓及改進算法,提高壓控增益曲線的線性度及相位噪聲曲線的平滑性。

2021-04-06 06:35:30

求一種基于FPGA滑動相關法偽碼捕獲的研究與實現

2021-04-30 06:52:27

范圍的振蕩器來滿足要求,但VCO的頻率不能更寬。射頻系統中VCO用在哪里?有一種調制叫做頻率調制或FM,這是應用在調頻廣播信號中的調制。頻率調制通過使信息無線發射,同事通過使射頻載波的頻率變化將信息

2017-12-06 14:03:45

大家好,我目前正在研究FPGA的溫度分布測量,我們的想法是使用分布式環形振蕩器(RO)和計數器來測量不同位置的FPGA溫度。問題是:當我在FPGA上放置一些振蕩器塊并在器件上編程時,它們的輸出(RO

2018-11-09 14:10:53

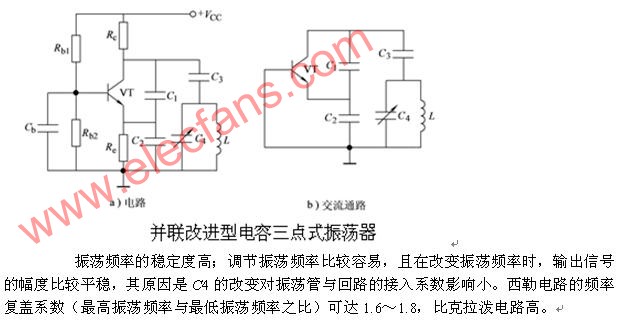

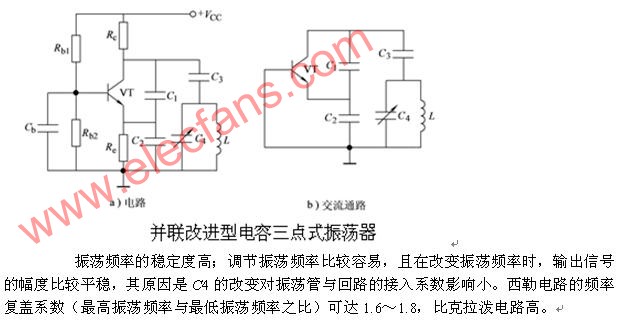

lc振蕩器或電感三點式振蕩器;如果反饋電壓取自分壓電容,則稱為電容反饋lc振蕩器或電容三點式振蕩器。 在幾種基本高頻振蕩回路中,電容反饋LC振蕩器具有較好的振蕩波形和穩定度,電路形式簡單,適于在較高

2018-10-22 15:15:45

有源晶振也稱之為石英振蕩器,因為石英精度要高于陶瓷的精度,所以,所有的振蕩器材質均為石英所成。石英振蕩器根據晶振在電路中不同的功能又分為溫補振蕩器,壓控振蕩器,普通振蕩器,壓控溫補振蕩器。溫補

2016-06-08 09:46:37

的元件組成。反饋網絡由石英晶體諧振器,和其他元件比如用來協調的可變電容等組成。晶體振蕩器特點?? 在振蕩頻率上,閉合回路的相移為2nπ。?? 當開始加電時,電路中唯一的信號是噪聲。滿足振蕩相位條件

2008-11-24 13:37:31

Turbo碼編碼器的FPGA實現Turbo碼譯碼器的FPGA實現Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

圖7所示的緩沖移相振蕩器在2.9kHz處振蕩(理想的頻率為2.76kHz),而且它是在增益為8.33的情況下振蕩(理想的增益為8)。緩沖器避免了各個RC彼此間的負載效應,從而緩沖移相振蕩器可運行于更

2015-01-09 11:02:42

組成串、并聯選頻網絡,R6 和R11 是串聯負反饋電阻,C7 是輸出電壓反饋電容,R3、R4 和R7、R8 分別是放大管VT1、VT2 的偏置電阻。圖6-28 典型RC橋式振蕩器提示在實際應用中,R6

2019-06-04 21:18:05

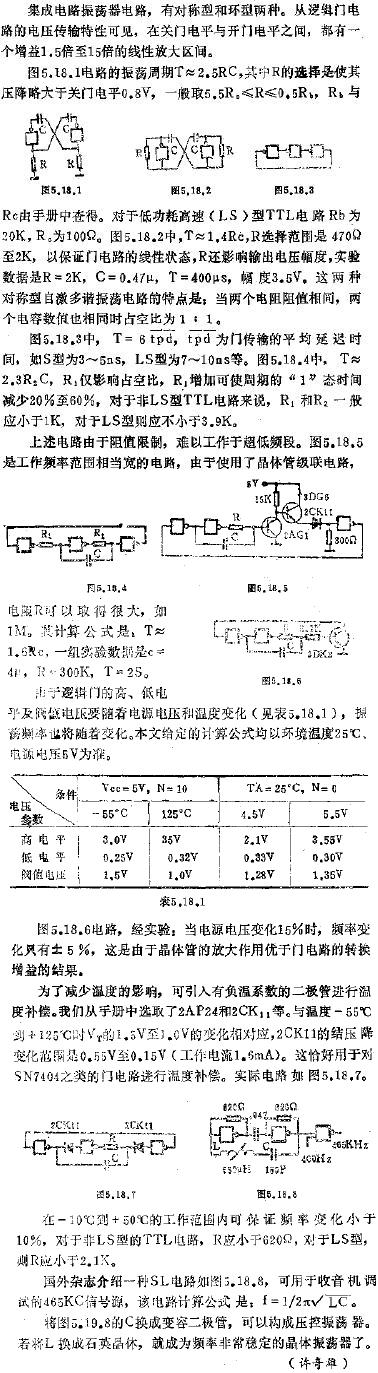

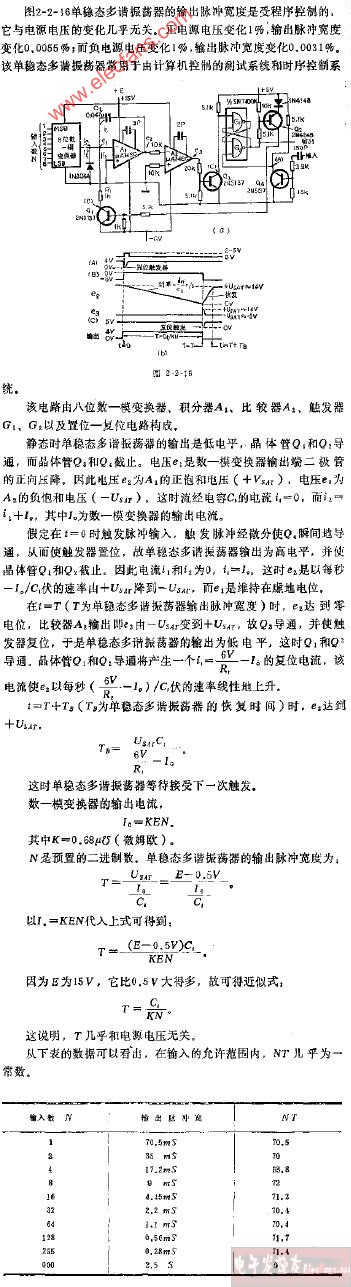

。該電路波形如圖6-34所示。圖6-34 非門多諧振蕩器工作波形(2)改進型非門多諧振蕩器改進型非門多諧振蕩器如圖6-35所示。該電路中,在非門D1 的輸入端增加了補償電阻R2,可以有效地改善由于電源電壓變化引起的振蕩頻率偏離現象。當R2>10R1時,振蕩周期T = 2.2RC。

2019-06-04 21:16:32

請問振蕩器如何生成精確時鐘源?振蕩的基本原理以及如何在晶體振蕩器中進行實現

2021-04-09 06:25:01

先生,PIC32 MX775 F256H中的主振蕩器和次振蕩器是什么? 以上來自于百度翻譯 以下為原文 Sir,what is primary and secondary oscillator in pic32mx775f256h.

2018-10-24 16:50:14

串聯改進型電容三點式振蕩器原理及電路

2019-09-27 08:49:57

找到FPGA數據表中FPGA最大允許振蕩器頻率的信息?也許有一些參考/信息以及關于如何為FPGA選擇振蕩器的示例。我可以購買一個產生20MHz的振蕩器以及一個產生200MHz的振蕩器。是否有輸入

2019-07-10 09:42:08

數控振蕩器的基本實現原理是什么?如何設計一種數控振蕩器?如何在FPGA器件中利用CORDIC迭代算法產生正余弦信號?

2021-04-14 07:05:17

請問怎么用vhdl語言,基于cordic算法設計一個數控振蕩器,哪位高手教教我,在下感激不盡!!

2012-04-07 21:28:50

隨著科學技術的發展,越來越多的振蕩器和天線集成在一起。小型化設計通常要求將多種器件集成到普通、緊湊的結構中。采用電壓串聯反饋來擴大有源器件的不穩定區,同時也將輸入和輸出反射最大化。在天線輸入端

2019-06-21 06:09:50

本文闡述了一種基于DSP 芯片TMS320C5409 的數字振蕩器的設計方法,該方法利用TMS320C5409 芯片的定時器和中斷通過迭代算法設計數字振蕩器。本文分別使用TMS320C5409 芯片的匯編語

2010-01-13 15:31:52 20

20

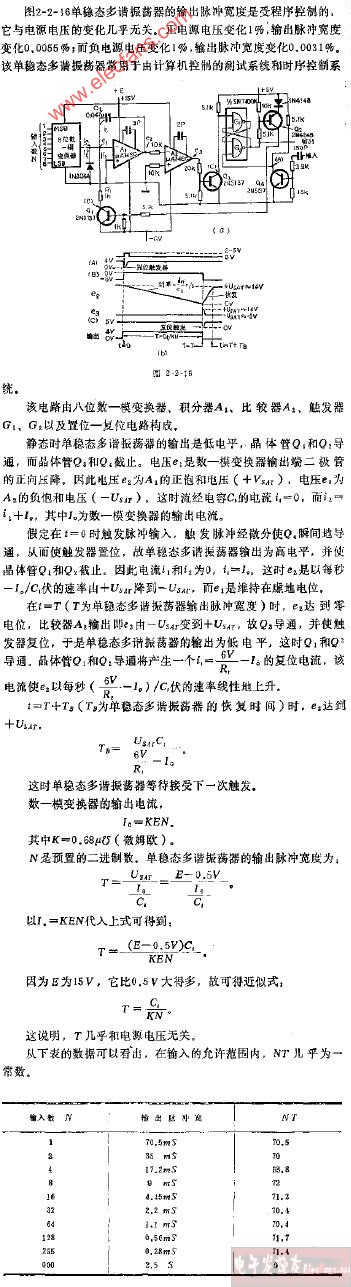

能抑制電源電壓漂移的數控單穩態多諧振蕩器

2009-03-29 09:23:48 334

334

數控單穩態多諧振蕩器

2009-03-29 09:25:03 403

403

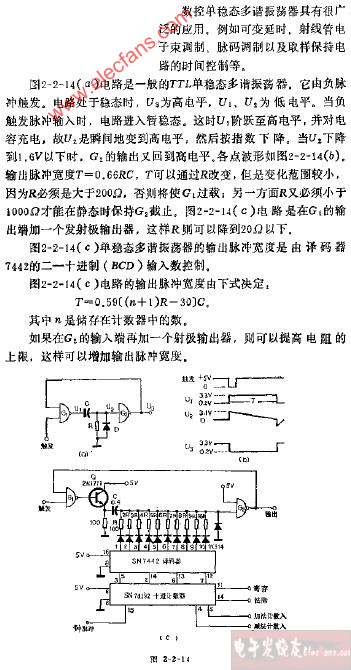

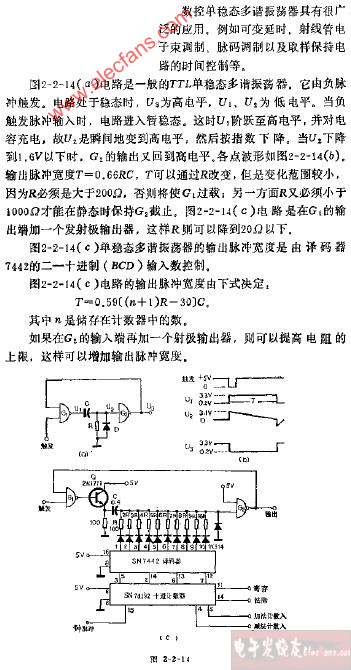

TTL集成電路振蕩器的改進電路圖

2009-04-20 11:12:23 654

654

改進型CMOS多諧振蕩器

在這個超低頻多諧

2009-09-26 16:52:32 579

579

基于FPGA和SRAM的數控振蕩器的設計與實現

1 引言 數控振蕩器是數字通信中調制解調單元必不可少的部分,同時也是各種數字頻率合成器和數字信號發生器的核心。

2010-01-07 10:35:53 786

786

振蕩器,振蕩器是什么意思

振蕩器

振蕩器(英文:oscillator)是一種能量轉換裝置——將直流電能轉換

2010-03-08 17:41:00 9219

9219 振蕩器,振蕩器的分類,振蕩器的特性

振蕩器定義振蕩器簡單地說就是一個頻率源,一般用在鎖相環中。詳細說就是一個不需要

2010-03-08 17:46:29 1242

1242 振蕩器,振蕩器的分類和原理是什么?

振蕩器定義振蕩器簡單地說就是一個頻率源,一般用在鎖相環中。詳細說就是一個不需要

2010-03-22 14:04:15 18191

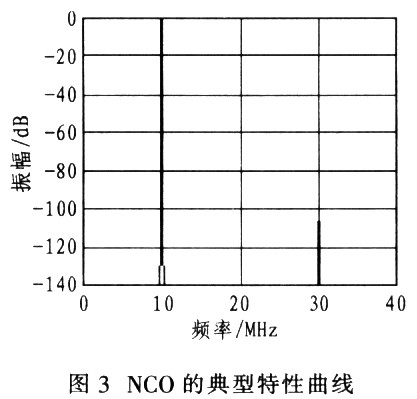

18191 數控振蕩器(Numerically Controlled Oscillators,NCOs)是軟件無線電的重要組成部分和研究內容,它廣泛應用于DSP中,如通信領域的信號調制解調,蜂窩電話、基站、雷達系統、數字電視、GPS

2010-03-24 10:46:58 1999

1999

并聯改進型電容三點式振蕩器原理及電路

振蕩頻率的穩定度高,調節振蕩頻率比較容

2010-04-16 17:53:12 4517

4517

串聯改進型電容三點式振蕩器原理及電路

2010-04-16 17:57:05 2829

2829

本文通過分析數控振蕩器的實現原理和性能,給出了通過FPGA來實現NCO的具體方法,同時通過QUARTUSⅡ中的仿真驗證了本設計的正確性。

2011-05-09 11:11:07 14048

14048

摘要: 傳統的基于查表法的數控振蕩器耗費大量的FPGA片內資源。為了解決這一問題,提出了一種基于CORDIC(coordinate rotation digital compute,坐標旋轉數值計算)算法的數控振蕩器的設計方

2012-05-28 16:04:59 39

39 摘要: 傳統的基于查表法的數控振蕩器耗費大量的FPGA片內資源。為了解決這一問題,提出了一種基于CORDIC(coordinate rotation digital compute,坐標旋轉數值計算)算法的數控振蕩器的設計方

2012-05-29 16:46:34 0

0 基于改進差分算法的運動目標檢測與跟蹤_王鎮西

2016-01-05 17:03:36 0

0 一種頻率穩定的改進型CMOS環形振蕩器參考設計。

2016-05-06 10:25:52 13

13 一種頻率穩定的改進型CMOS環形振蕩器,參考資料。

2016-05-06 10:25:52 0

0 實時圖像增強算法改進及FPGA實現,下來看看

2016-09-17 07:28:24 14

14 為解決目標外形、姿態變化以及被遮擋的難點,對壓縮跟蹤算法進行改進:以Kalman預測位置為中心,采用由粗到精的搜索策略,快速準確地找到具有最大分類分數的目標位置:根據目標在每一幀最大分類分數的變化

2017-11-14 15:44:07 2

2 數控振蕩器(NCO)因具有頻率精度高、轉換時間短、頻譜純度高以及頻率相位易編程等特點,而被廣泛應用于軟件無線電數字上、下變頻以及各種頻率和相位數字調制解調系統中。NCO是正交數字混頻器的核心

2017-11-23 15:27:01 3097

3097 正余弦信號的實現過程,給出了在FPGA 中設計數控振蕩器的頂層電路結構,并根據算法特點在設計中引入流水線結構設計。

2020-08-26 17:21:31 2648

2648

主要介紹了坐標旋轉數字計算(CORDIC)算法在US,g,鑒別器中的應用,包括碼跟蹤環、鎖頻環和鎖相環鑒別器,并進行了FPGA實現。在設計中,采用統一cORDIc算法優化方法減少硬件開銷,用非流水

2021-01-22 16:12:00 8

8 AD9830:一種正弦查找數據表--數控振蕩器

2021-04-29 16:23:28 8

8 電子發燒友網站提供《基于FPGA的神經振蕩器設計及優化.pdf》資料免費下載

2023-11-10 09:39:29 0

0 ,而MEMS差分振蕩器則采用微機械元件實現,因此能夠在尺寸和功耗上實現更大的優化。本文將深入探討MEMS差分振蕩器與傳統差分振蕩器之間的區別和優勢。 首先,MEMS差分振蕩器的最大優勢在于其微機械元件的制造方式。傳統差分振蕩器使用的元件需

2024-01-26 14:20:52 128

128

![]()

![]()

電子發燒友App

電子發燒友App

評論