1、引言

四相絕對(duì)移相鍵控(QPSK)技術(shù)以其抗干擾性能強(qiáng)、誤碼性能好、頻譜利用率高等優(yōu)點(diǎn),廣泛應(yīng)用于數(shù)字通信系統(tǒng)。隨著超大規(guī)模集成電路的出現(xiàn),FPGA在數(shù)字通信系統(tǒng)中的應(yīng)用日益廣泛,目前已提出了多種基于FPGA實(shí)現(xiàn)QPSK的方法。

本文基于FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS),通過對(duì)DDS信號(hào)f載波信號(hào)1輸出相位的控制實(shí)現(xiàn)調(diào)相,除DA轉(zhuǎn)換外,其它過程均口以FPGA實(shí)現(xiàn)。

2、 QPSK調(diào)制的基本原理

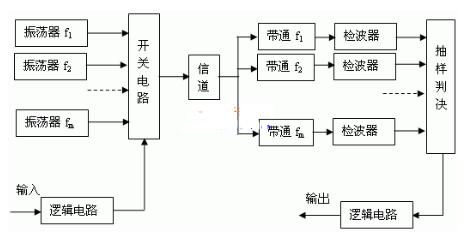

QPSK采用四種不同的載波相位來表示數(shù)字信息,每個(gè)載波相位代表2比特信息,其實(shí)現(xiàn)有兩種方法,相位選擇法與正交調(diào)制法,相位選擇法又分為A、B兩種方式。本文采用相位選擇法B方式來實(shí)現(xiàn)QPSK信號(hào),如圖1所示。

圖1相位選擇法產(chǎn)生QPSK信號(hào)

3、 QPSK調(diào)制電路的FPGA實(shí)現(xiàn)

3.1串并轉(zhuǎn)換電路

圖2串并轉(zhuǎn)換電路

調(diào)制信號(hào)(DATA)形成雙比特碼兀QI口】由圖2所不串并轉(zhuǎn)換電路實(shí)現(xiàn)。

假設(shè)涮制信號(hào)為01100011,其時(shí)序圖如圖3所示。從時(shí)序圖可以看出,從第3個(gè)時(shí)鐘脈沖開始,每2個(gè)時(shí)鐘脈沖,在Q3、Q6同時(shí)輸出DATA的連續(xù)2bit數(shù)據(jù),生成雙比特碼元QI,雙比特碼元速率為時(shí)鐘信號(hào)(CLKl)頻率的一半。為了配合后面的相位調(diào)制電路,時(shí)鐘信號(hào)(CLKl)頻率為系統(tǒng)時(shí)鐘頻率k的I/M,可以通過M分頻電路實(shí)現(xiàn)。

圖3串并變換電路時(shí)序圖

3.2四相載波產(chǎn)生器

四相載波產(chǎn)畢器甚干DDS構(gòu)成.如圖4所示。

圖4基于DDS的四相載波產(chǎn)生電路

(1)建立正弦查找表

ROM正弦查找表存儲(chǔ)了一個(gè)完整正弦波周期的抽樣值,設(shè)相位累加器的數(shù)據(jù)線寬度為N,則有2一個(gè)采樣點(diǎn)。先用其他工具計(jì)算出這2n個(gè)采樣點(diǎn)的幅度值,則相鄰2個(gè)采樣點(diǎn)的相位增三個(gè)時(shí)鐘后,相應(yīng)的載波初始相位、幅艘值與理論分析是一致量為2π/2n,這樣,各采樣點(diǎn)的位置就確定了該采樣點(diǎn)的相位;以ROM依次存儲(chǔ)2n個(gè)采樣點(diǎn)的幅度值,便建立了各采樣相位(存儲(chǔ)器地址)與幅值的影射關(guān)系。

然后用Quartus 5.1建立mif文件,調(diào)用LPM_ROM模塊,將mif文停的數(shù)據(jù)內(nèi)容寫入LPM_ROM。

(2)相位累加器

設(shè)相位累加器的初始值為0,累加步長(zhǎng)為頻率控制字K.則每一個(gè)時(shí)鐘周期(1/fclk)的相位增量為K×2π2n,一個(gè)完整正弦波周期需要進(jìn)行2π(Kx2/2n)=2N/K次累加,所以輸出信號(hào)周期10t=(I/fclk)X2N/K,輸出信號(hào)頻率fout=Kxfclk/2n。

(3)邏輯選相電路

雙比特序列QI作為相位控制字用于四種相位載波的選擇控制。本文取N:10,先計(jì)算出這210=1024個(gè)采樣點(diǎn)的幅度值,量化為8位二進(jìn)制數(shù)表示。相位為π/4和3π/4時(shí),對(duì)應(yīng)幅度值為38,存儲(chǔ)地址分別為000111111l和0101111111。

本義中用VHD語(yǔ)句來完成邏輯選相電路。

if clk“event and clk=’l’then

b《=QI(1);

c《=QI(0);

if (clklh=‘1’ or clkll=‘1’ or clk2h=1’or clk21=‘1’)then -- 每個(gè)雙比特碼元的上升沿

case QI is

when”00”=》uuu《=”100111111l”;reset《=‘1’;--5π/4載波

when”O(jiān)l”=》uuu《-”01011111Il”;reset《=‘1’;--3π/4載波

when”10”=》UUll《=”1101111111”;reset《=‘1’;--7π/4載波

when’’11”=》uuu《-”0001111111”;reset《=‘I’; --4載波

when others=》uuu《=”0000000000”;reset《=‘l’

end ease;

else uuu《=uuu+“0001000000”;reset《=‘0’;

endif;

(5)相位調(diào)制器

在每個(gè)雙比特碼元的上升沿產(chǎn)生一復(fù)位信號(hào)(RESET)使DDS的棚位累加器清零,則輸出裁波信號(hào)的初始相位僅由相位控捌字控制,以保證初始相位為0l碼元對(duì)應(yīng)的載波相位;而其它情提下將其與相位累加器的輸出相加,共同作為載波信號(hào)的相位,從而實(shí)現(xiàn)調(diào)相。

4、仿真實(shí)驗(yàn)及結(jié)論

仿真實(shí)驗(yàn)中,取fclk=294912Hz,M=48,K=32,則fclk=fclk/M=6144Hz,載波頻率fout=Kxfclk/2N=9216Hz。通過Quartusll 5.1軟件仿真.得到仿真結(jié)果如圖5所示。

在圖(5)中,當(dāng)QI為11時(shí)的第一個(gè)時(shí)鐘,RESET信號(hào)對(duì)DDS寄存器復(fù)位(T=0),累加器中的加法器輸出R=32,并保持一個(gè)時(shí)鐘;第三個(gè)時(shí)鐘后QPSK輸出為218,這與QI為11時(shí),載波初始相位為π/4、幅度值為218是一致的。間樣,當(dāng)QI為00、lO、Ol的仿真結(jié)果分剮如圖5(b)、5(c)、5(d)所示,在QI碼元到達(dá)三個(gè)時(shí)鐘后,相應(yīng)的載波初始相位、幅度值與理論分析時(shí)一致的。雖然QPSK信號(hào)有三個(gè)時(shí)鐘的延遲,但由于各QI碼元的延遲都是一致的,并不影響QPSK的實(shí)現(xiàn);另一方面,延遲時(shí)間不到系統(tǒng)時(shí)鐘周期的三分之一,可以忽略。

圖5仿真實(shí)驗(yàn)波形

5、結(jié)束語(yǔ)

本文采用FPGA實(shí)現(xiàn)QPSK調(diào)制器克服了傳統(tǒng)的模擬調(diào)制器的體積大、成本高、系統(tǒng)調(diào)試難和生產(chǎn)周期長(zhǎng)等缺點(diǎn)。本文作者創(chuàng)新點(diǎn)在予除了DA轉(zhuǎn)換外,系統(tǒng)全部由FPGA實(shí)現(xiàn),對(duì)于其它調(diào)制方式(如DQPSK、8PSK、QAM等)的FPGA實(shí)現(xiàn),以及FPGA在軟件無線電鐘的應(yīng)用具有一定的參考價(jià)值。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論