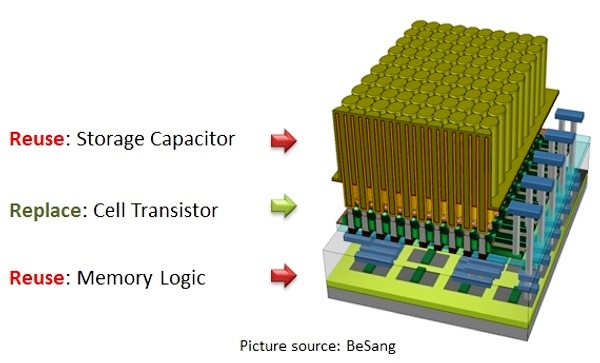

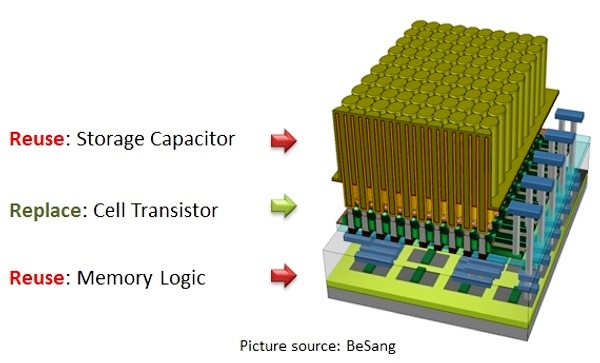

為了要延長DRAM這種內(nèi)存的壽命,在短時間內(nèi)必須要采用3D DRAM解決方案。什么是3D超級DRAM (Super-DRAM)?為何我們需要這種技術?以下請見筆者的解釋。

2017-03-17 09:42:04 2720

2720

基于最新大綱定制課程,讓你在最短時間內(nèi),快速掌握新大綱的重點考點。幫助你通過考試。適合人群:期望在最短的時間內(nèi)通過中級通信工程師考試的行業(yè)從業(yè)人員。

2019-07-11 16:45:04

如圖1.6所示。這個流程圖是一個相對比較高等級的FPGA開發(fā)流程,從項目的提上議程開始,設計者需要進行FPGA功能的需求分析,然后進行模塊的劃分,比較復雜和龐大的設計,則會通過模塊劃分把工作交給一個

2019-01-28 04:24:37

布線算法和很多細節(jié)問題,比如涉及到布線資源、PLL資源分布。但是這些對我們理解布線這個概念沒有很多益處,暫且不深入,本質(zhì)上就是一個線路求最優(yōu)的問題。FPGA開發(fā)—約束約束,在圖1上看到,在綜合和布局布線

2017-11-22 09:34:02

,再用AS模式把程序燒到配置芯片里去。FPGA開發(fā)—開發(fā)工具總結在圍繞圖1把FPGA開發(fā)流程講完后,這里對每個環(huán)節(jié)中設計的相關軟件進行總結,如下表所示。畢竟充分利用各種工具的特點,進行多種EDA工具的協(xié)同

2017-11-22 09:37:02

開發(fā)是門檻最高的行業(yè)之一,FPGA采用HDL(硬件描述語言)直接從最底層開發(fā)算法,對工程師的要求極高,沒有很好的方法,入門很難;2、5G的發(fā)展,深度學習,自動無人駕駛的興起,傳統(tǒng)純軟件處理方式已經(jīng)不能

2019-05-10 16:22:19

的開發(fā)環(huán)境要熟悉,具備縝密的邏輯能力。微處理器用C,FPGA用HDL,這個不用說了。論算法實現(xiàn)速度,FPGA肯定比微處理器快多了,因為FPGA可以算準每一個時鐘周期的任務,而微處理器執(zhí)行C程序可能會

2018-08-16 09:38:12

FPGA入門:基本開發(fā)流程概述 在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個流程圖是一個相對比較高等級的FPGA/CPLD器件開發(fā)流程,從項目

2019-01-28 02:29:05

FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義、設計輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實現(xiàn)與布局布線、時序仿真與驗證、板級仿真

2023-12-31 21:15:31

FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實現(xiàn)、布線后仿真

2021-07-23 09:12:07

流程效率有高度的要求等。鑒于日益升溫的FPGA市場,EDA業(yè)者加碼布局,加速FPGA設計進程、提高驗證效率,幫助廣大工程師在短時間內(nèi)進行準確無誤的設計。 FPGA市場需求急升 Cadence頻祭殺手锏

2013-04-17 11:20:14

開發(fā)流程FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般如圖2所示,包括電路設計、設計輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實現(xiàn)、布線后仿真、板級

2017-01-10 15:50:15

FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實現(xiàn)、布線后

2020-11-30 16:22:59

第二章 FPGA 開發(fā)流程FPGA 的設計流程就是利用 EDA 開發(fā)軟件和編程工具對 FPGA 芯片進行開發(fā)的過程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

本帖最后由 benben913 于 2016-8-17 17:00 編輯

labview和串口工具互相發(fā)送數(shù)據(jù),labview每100毫秒或更短時間內(nèi)向串口工具發(fā)送一次串口數(shù)據(jù),當串口工具向labview發(fā)送數(shù)據(jù)時,串口工具接收顯示部分有延遲不知道怎么回事,附labview源程序

2016-08-17 16:24:16

老師給舉了個例子,說是就像測試規(guī)定時間內(nèi)電燈開關的次數(shù)。這個課題的題目是壽命實驗,用的NI采集卡,采集對象是電壓,雙通道給的要求就是:用戶給出一個時間,測量在此時間內(nèi)雙通道的采集次數(shù)我的想法是,這個

2015-12-17 12:17:54

我的esp-01 需要大約 150 毫秒才能打開并接收一些數(shù)據(jù)(使用 esp-now),然后再回到睡眠狀態(tài)。

我可以讓它在更短的喚醒時間內(nèi)工作嗎?

2023-04-28 07:11:04

的要求和FPGA芯片設計的靈活性結合起來,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL語言編程,最后分別使用Quartus Ⅱ和Matlab軟件開發(fā)工具驗證實現(xiàn)

2010-05-28 13:38:38

如何在短時間內(nèi)學好LABVIEW

2013-05-24 13:58:47

LVDT位移不發(fā)生變化時,AD698所產(chǎn)生的輸出電壓在短時間內(nèi)不會發(fā)生變化,但時間一長就會有20mv~40mv的變化,電壓變大變小的情況都有。并且,在不接LVDT的情況下,把手指搭在AD698芯片上

2023-11-17 06:01:30

cc2640和安卓配對,短時間沒輸入密碼界面就自動消失了?我在用cc2640和安卓手機做配對和綁定實驗時,在ProcessPairStateCB()函數(shù)中,進入不了

2016-03-28 10:20:59

ch573按照官方的圖紙參數(shù)畫的pcb,短時間重新上電cpu不工作。需要等很長時間,大概幾分鐘再次上電才能工作。有什么好的建議?謝謝!

2022-08-08 07:07:06

labview密碼破解方法,在未知密碼長度的情況下可以在短時間內(nèi)破解密碼嗎?

2015-11-23 23:01:47

經(jīng)歷了布爾等式,原理圖輸入,硬件描語言這樣一個發(fā)展過程。隨著設計的日益復雜和可編程邏輯器件規(guī)模的不斷擴大,人們不停地尋求更加抽象的行為級設計方法,以便在盡可能短時間內(nèi)完成自己的設計構思。現(xiàn)狀與問題今天

2015-01-13 16:34:40

Type-C是近幾年大規(guī)模普及的充電接口,目前所發(fā)布的手機基本上都是該接口,而原來的Micro USB接口也逐漸減少使用,那為什么Type-C接口能在短時間內(nèi)迅速取代Micro USB接口呢?筆者

2021-09-14 07:34:39

基于軟件的革新性電子產(chǎn)品設計打開了大門,這就是一個很好的例子。簡言之,把設計的主要元素——在這兒是控制“智能”——轉(zhuǎn)入到軟領域后,設計工程師就可以在更短時間內(nèi)創(chuàng)建出更好、更智能、更廉價的產(chǎn)品。這個變化意味著

2020-07-21 15:09:16

的革新性電子產(chǎn)品設計打開了大門,這就是一個很好的例子。簡言之,把設計的主要元素——在這兒是控制“智能”——轉(zhuǎn)入到軟領域后,設計工程師就可以在更短時間內(nèi)創(chuàng)建出更好、更智能、更廉價的產(chǎn)品。 這個變化

2017-07-21 10:25:13

圖1,主電路拓撲結構圖2,變壓器輸入電壓uab波形 五電平uab中,零電平持續(xù)的最短時間是多少,怎么計算?

2019-04-18 15:57:00

的標準單元ASIC可以提供更高的性能,但是因為開發(fā)時間和成本而常常不能采用。 軟件被移植到選用于硬件實現(xiàn)的微控制器或者MCU/DSP組合上。一旦硬件/軟件的劃分完成以后,再要做出改變將非常難,而且非常

2008-09-27 11:42:55

。l實現(xiàn)在FPGA不同廠家之間以及從FPGA到ASIC的順利移植。l便于新員工快速掌握本部門FPGA的設計流程。由于目前所用到的FPGA器件以Altera的為主,所以下面的例子也以Altera為例,工具

2017-12-08 14:47:15

設計補丁)。由于自動HDL代碼生成流程比手工編碼快,工程師得以把節(jié)省下來的時間投入到詳細設計階段,生成更優(yōu)質(zhì)的定點算法。與手動的工作流程相比,這種方法使工程師能夠以更快的速度生成質(zhì)量更佳的FPGA原型

2020-05-04 07:00:00

隨著EDA平臺服務趨于網(wǎng)絡化,如何通過對資源和流程的有效管理,為用戶提供更為方便安全的遠程EDA平臺調(diào)用服務,已成為關鍵問題。在FPGA開發(fā)平臺上集成了EDA工具環(huán)境,并部署SGD軟件。在實現(xiàn)遠程

2019-07-16 21:09:34

RT-Thread 的源代碼(因為 RT-Thread 的代碼更新很快,短時間內(nèi)就有可能有很多的代碼更新)。然后我進入 rt-thread\bsp\stm32目錄下,找到了正點原子 F429 阿波羅...

2022-01-26 06:31:14

在visiual studio上開發(fā)調(diào)試了人臉識別算法,如何移植到DSP上?

2014-02-23 14:32:21

上的損失。代碼實現(xiàn)部分如下。下面是官方給的RGB888 to YCbCr的算法公式,我們可以直接把算法移植到FPGA上,但是我們都知道FPGA無法進行浮點運算,所以我們采取將整個式子右端先都擴大256

2017-10-28 08:48:57

訓練一個神經(jīng)網(wǎng)絡并移植到Lattice FPGA上,通常需要開發(fā)人員既要懂軟件又要懂數(shù)字電路設計,是個不容易的事。好在FPGA廠商為我們提供了許多工具和IP,我們可以在這些工具和IP的基礎上做

2020-11-26 07:46:03

系統(tǒng)設計性能的關鍵所在。針對高速實時信號處理的要求,軟件實現(xiàn)方法顯然滿足不了其需要。近年來現(xiàn)場可編程門陣列(FPGA)以其高性能、高靈活性、友好的開發(fā)環(huán)境、在線可編程等特點,使得基于FPGA的設計可以

2019-06-17 09:01:35

(較新的加速度計)的數(shù)據(jù)表中讀到,“為了確保擁有與所選 ODR 同步的第一個 DRDY 上升沿(避免圖 2 中的情況:“DRDY 信號同步”)在啟用 ODR 之前將 I1_ ZYXDA 位設置為“1”。沒有運氣。你能給我一個建議,如何在開機后的最短時間內(nèi)從 LIS2DH 讀取有效數(shù)據(jù)嗎?先感謝您!

2023-01-04 08:48:17

隨著 FPGA 在數(shù)字通信設計領域(蜂窩基站、衛(wèi)星通信和雷達)的高性能信號處理電路中成為可行的選擇,分析和調(diào)試工具必須包括能幫助您在最短時間內(nèi)得到電路最佳性能的新技術。

2019-11-01 07:54:28

第三章 如何改進和優(yōu)化RSA算法這章呢,我想談談在實際應用出現(xiàn)的問題和理解。由于近期要開始各種忙了,所以寫完這章后我短時間內(nèi)也不打算出什么資料了=- =(反正平時就沒有出資料的習慣。)在講第一章

2021-07-19 07:12:00

/4W型碳膜電阻器。XP用市售普通交流電兩極插頭。 三、制作與使用 短時間應急燈的裝配按照圖2所示進行。除熒光燈和電源插頭XP外,其余元器件全部焊裝在一個用薄木板自制的密閉小盒(體積約65mm

2021-05-28 07:22:43

安路軟件如何獲取?

2023-08-11 06:04:32

、編譯、優(yōu)化,用仿真工具進行邏輯功能仿真和系統(tǒng)時序仿真,可在短時間內(nèi)設計出高效、穩(wěn)定、符合設計要求的大規(guī)模或超大規(guī)模的集成電路。

2019-08-13 07:52:44

來糾正這些故障。例如:(1){WICEDDYRITSO DELAYY毫秒(100);}為了確保我的應用程序不會失敗,延遲的最短時間是多少?這是關于什么的? 以上來自于百度翻譯 以下為原文Hello

2018-10-26 15:58:03

本人在讀研,現(xiàn)在接觸的一個項目是要在FPGA上實現(xiàn)視頻圖像處理,現(xiàn)在手上的板子是Genesys Virtex-5 FPGA開發(fā)板,之前實現(xiàn)圖像處理都是使用OPENCV 的,現(xiàn)在要移植到FPGA上,哪位大神能夠指點一下。

2016-04-26 15:02:53

平臺跟GCC差別太大了,要修改的內(nèi)容巨多,而且ARM開發(fā)板很多功能其實沒必要移植到STM32上的,一下子覺得這個事情太龐大自己做不來,后面就放棄了。前段時間剛結束項目攻關,晚上有空閑時間就硬著頭皮去改...

2022-02-21 06:40:14

430 串口每間隔T就會受到一串數(shù)據(jù),怎樣讓430在2到3個T時間內(nèi),沒有收到數(shù)據(jù)時就休眠,數(shù)據(jù)來了就喚醒, 各位有什么好的方法,指教下。

2019-01-09 15:55:19

轉(zhuǎn)帖芯片是智能產(chǎn)品的核心,以FPGA來實現(xiàn)智能應用,具有非常大的優(yōu)勢,可以很輕松地進行各種修改或升級,以便在最短時間內(nèi)支持新的智能算法。隨著智能產(chǎn)品的廣泛應用,FPGA進入嶄新的黃金時代。那么

2017-12-29 16:45:29

芯片RTL實現(xiàn),AI芯片仿真測試,AI芯片工具鏈的完整全棧式的解決方案的教學。4、AI芯片設計思路復雜,實現(xiàn)步驟繁多。我們團隊從0到1的過程中走過很多彎路,通過本課程希望為后來者分享我們的經(jīng)驗和教訓;5

2019-07-19 11:54:01

上運行舊版固件時,RTC 非常準確。有沒有一種方法可以使 RTC 在短時間內(nèi)停止計數(shù)的地方“中斷”,因為其他原因正在暫停 LSE?TouchGFX 是否在后臺執(zhí)行任何可能導致此類問題的操作?感謝您的任何和所有輸入。我們現(xiàn)在很困惑。

2023-01-04 07:44:07

每秒出一個隨機數(shù),如何求10秒時間內(nèi)的數(shù)據(jù)總和

2016-08-03 18:19:57

給電容充好電之后,讓電容短時間大功率放電的問題?我想用一個普通的24V的開關電源給一個電容充電,把這個電容充到10V到20V之間的某個值,相當于把這個電容當作一個電源,然后,等待我需要讓這個電容放電

2018-05-30 18:39:40

請教一下大神單片機Io口檢測到高電平的最短時間是多少?

2023-03-06 14:12:59

ADC的采樣時鐘來實現(xiàn)這個需求,會不會有問題??隱隱覺得這樣做似乎有問題。如果不這樣做,我如何才能以最短的時間將ADC的采集和我的觸發(fā)信號同步起來呢?

2019-02-15 13:32:30

如何使用 EVAL-AD7903SDZ 及其配套軟件存儲一段連續(xù)時間內(nèi)的信號?現(xiàn)在只能存下視窗內(nèi)的數(shù)據(jù)。或者有沒有別的方法能夠讀取并儲存 EVAL-AD7903SDZ 板上的數(shù)據(jù)?

2023-12-07 07:28:31

1.XILINX ISE傳統(tǒng)FPGA設計流程利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現(xiàn)、布線后仿真與驗證和下班調(diào)試等步驟。如下圖所示。1)電路設計

2021-06-24 08:00:01

該文首先研究了單認知用戶能量檢測算法的檢測性能和檢測靈敏度與檢測時長和噪聲短時間內(nèi)平均功率波動性之間的關系,得出檢測性能和檢測靈敏度隨噪聲短時間內(nèi)平均功率波動

2010-02-10 14:43:10 23

23 以數(shù)學模型為基礎,提出了一種基于STC12C5410AD系列單片機的求干擾源各項參數(shù)的新算法。在復雜電磁環(huán)境下,實現(xiàn)干擾信號偵測、追蹤和定位,并在最短時間內(nèi)消滅干擾源,與現(xiàn)有

2010-12-23 16:43:14 0

0 當晚上突然遇到停電,周圍漆黑一片,這時就要用到 應急燈 啦!這種應急燈的作用時間很短,即當你在1min(分鐘)內(nèi)從容不迫地點亮蠟燭后,這盞燈才會慢慢熄滅。 一、短時間應急燈工

2012-06-05 14:34:31 4935

4935

的可擴展、高性能等優(yōu)勢使其可以在多領域大展身手,例如Intel、 百度等商業(yè)巨頭都開始著手使用FPGA作為他們的數(shù)據(jù)中心,利用FPGA實現(xiàn)一些深度學習、人工神經(jīng)網(wǎng)絡算法等。 六年前Xilinx便開始了一項打破傳統(tǒng)FPGA開發(fā)流程的研究項目,使軟件開發(fā)的一套流程能夠移植

2017-02-09 01:22:42 234

234

基于動態(tài)交通的最短時間路徑規(guī)劃方法研究_向冬梅

2017-03-17 16:13:55 3

3 的設計上對網(wǎng)表或是布局布線進行局部編輯,從而在最短時間內(nèi),以最小的代價完成個別的設計改動需求。ECO指的是Engineering Change Order,即工程變更指令。

2017-11-18 18:26:46 4987

4987

劉愛力表示,中國電信雖然大部分業(yè)務均在內(nèi)地,但如果不是能與用戶分享公司的發(fā)展,再加上要考慮公司未來股價走勢等諸多問題,故而公司短時間內(nèi)未有回A 股上市的決定。

但中電信是有計劃將旗下子公司如翼支付或一些資管公司分拆上市,只是還沒有決定在A股或者赴港上市。劉愛力表示,翼支付剛完成了新一輪融資。

2018-05-29 09:51:00 862

862 據(jù)e公司的直播(本文主要內(nèi)容來源于e公司直播),中興通訊總裁趙先明指出,絕大多數(shù)客戶耐心等待著中興通訊恢復運營,公司市場一線的同事堅持在一線,盡可能短時間內(nèi)恢復生產(chǎn)經(jīng)營,把耽誤掉的時間追趕回來,力爭

2018-07-27 10:25:24 5263

5263 ,并成功實現(xiàn)無束縛飛行。就外觀而言,該飛行器有兩大特色:一對額外的翅膀(四翼)和頂部的太陽能電池。它可以在短時間內(nèi)不受束縛地飛行。

2019-07-07 10:38:26 3756

3756 雖然深圳的企業(yè)運營成本在不斷上漲,但是深圳的優(yōu)勢在于制造業(yè)產(chǎn)業(yè)鏈非常的齊全,這不是其他城市短時間內(nèi)能夠趕上的。

2019-07-29 15:17:32 3555

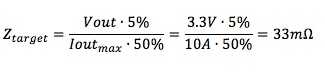

3555 任何關于電源完整性的討論都包括對目標阻抗和平坦阻抗要求的概念的大量強調(diào)。但我們?nèi)绾卧O計專門用于平坦阻抗的穩(wěn)壓器模塊(VRM)?本文不僅將討論該特定問題,還將解決如何在5秒或更短時間內(nèi)完成該問題。

2019-08-12 10:34:55 2095

2095

盡管在區(qū)塊鏈上投入了數(shù)十億美元,而且預計未來5年這方面的支出將呈指數(shù)級增長,但分布式賬本技術永遠不會在企業(yè)中引發(fā)一場技術革命,因為在企業(yè)中,人們的偏好總是傾向于集中式的控制。

2019-10-14 16:42:32 425

425 FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般如下圖所示,包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現(xiàn)、編程調(diào)試等主要步驟。

2019-10-15 11:25:07 3356

3356 FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現(xiàn)、編程調(diào)試等主要步驟。

2019-11-20 15:06:28 1545

1545 12月25日消息 根據(jù)網(wǎng)易暴雪游戲客服團隊的消息,暴雪游戲平臺近期受到了持續(xù) DDOS 攻擊,官方稱無法斷言能在短時間內(nèi)完全解決該問題。 暴雪表示,近期受到的一系列大型惡意“分布式拒絕服務(DDOS

2020-12-25 15:14:17 1666

1666 終止科創(chuàng)板上市”,這意味著,聯(lián)想的科創(chuàng)板IPO之路,只走了短短一個工作日。 為何聯(lián)想會選擇在這么短時間內(nèi)提交就撤回申請?這個問題在當時眾說紛紜,有人猜測聯(lián)想達不到科創(chuàng)板上市標準,有人猜測是因為聯(lián)想負債率過高,也有機構報告

2021-11-08 14:38:30 1249

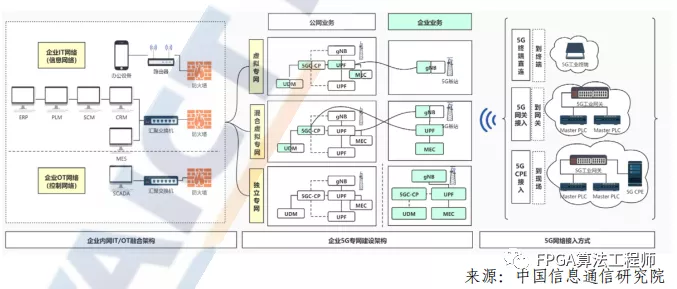

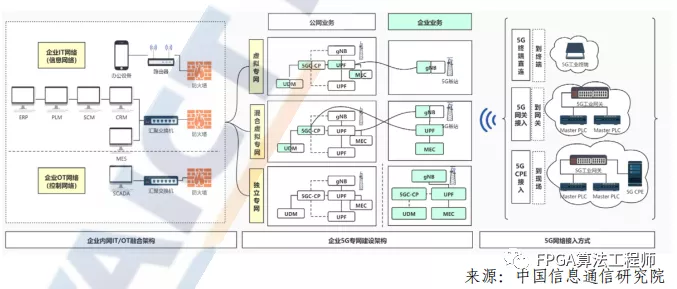

1249 一個完整的通信系統(tǒng),是十分龐大的,沒有幾百上千人,在短時間內(nèi)是做不好的。本文僅僅針對5G NR中的基帶算法部分,做一個簡單梳理。

2022-02-16 16:21:26 2224

2224

如何在短時間內(nèi)解決電廠鍋爐風機軸修復問題?

2022-05-25 16:10:50 0

0 華強北眾生相2021年,受到國內(nèi)外疫情的影響,加上2020年被壓抑的需求得到釋放,導致消費電子銷量大幅上漲,繼而使芯片需求在短時間內(nèi)暴漲,而本地芯片供應也很難跟上,大多只能向海外求購,但疫情導致物流受阻,芯片供應減少,市場中開始掀起炒作的浪潮,很多人的夢從這一刻開始。

2022-08-22 09:32:31 2395

2395 流程管理工具是一種能夠幫助集成電路設計者在最短的時間內(nèi)高質(zhì)量完成大規(guī)模復雜集成電路設計而采用的規(guī)范化工具。

2022-08-22 10:59:06 956

956 如果你的Linux服務器突然負載暴增,告警短信快發(fā)爆你的手機,如何在最短時間內(nèi)找出Linux性能問題所在?來看Netflix性能工程團隊的這篇博文,看它們通過十條命令在一分鐘內(nèi)對機器性能問題進行診斷。

2022-09-16 09:16:26 658

658 SAP 開發(fā)人員希望就基于云的壓縮即服務 (CaaS) 創(chuàng)建概念驗證 (PoC)。他們需要利用 FPGA 來加速運行計算密集型 Re-Pair 壓縮算法,并希望在基于 SAP 自有 Garden Linux 操作系統(tǒng) (OS) 的 SAP HANA 云中使用 Docker 容器。

2022-10-20 15:04:20 490

490 如果你的Linux服務器突然負載暴增,告警短信快發(fā)爆你的手機,如何在最短時間內(nèi)找出Linux性能問題所在?來看Netflix性能工程團隊的這篇博文,看它們通過十條命令在一分鐘內(nèi)對機器性能問題進行診斷。

2022-12-28 09:21:36 138

138 FPGA 的設計流程就是利用 EDA 開發(fā)軟件和編程工具對 FPGA 芯片進行開發(fā)的過程。原理圖和HDL(Hardware description language,硬件描述語言)是兩種最常用的數(shù)字

2023-03-21 10:26:50 2623

2623 設計實現(xiàn)流程后,引出了一個更細節(jié)的應用場景:如何利用 Tcl 在已完成布局布線的設計上對網(wǎng)表或是布局布線進行局部編輯,從而在最短時間內(nèi),以最小的代價完成個別的設計改動需求。

2023-05-05 15:34:52 1612

1612

確定算法:首先,你需要確保要移植的C語言算法是合適的。FPGA適合并行計算和高度可定制的應用。因此,你需要選擇一個適合FPGA實現(xiàn)的算法。

2023-09-12 17:20:58 901

901 在變壓器設計中,為什么要考慮短時過載能力? 在變壓器設計中,考慮短時過載能力是十分重要的。這是因為在實際應用中,變壓器常常會面臨短時間內(nèi)電流超過額定值的情況,而變壓器的短時過載能力可以影響其安全性

2023-11-23 14:18:59 422

422 在電力系統(tǒng)中,電容器是一種重要的電氣設備,常用于提高功率因數(shù)、改善電網(wǎng)穩(wěn)定性等方面。然而,電容器作為一種電壓敏感的元件,對于電壓波動非常敏感,特別是在短時間內(nèi)的過電壓情況下,可能引發(fā)嚴重的問題。為什么電力電容器不允許短時間內(nèi)過電壓運行?

2024-02-26 14:30:26 120

120

電子發(fā)燒友App

電子發(fā)燒友App

評論