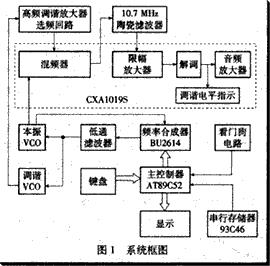

作為收音機(jī)重要組成部分的調(diào)諧電路和本振電路一直采用傳統(tǒng)的電容、電感手動調(diào)臺方式。近年來,隨著無線電通信技術(shù)的迅速發(fā)展,鎖相環(huán)和頻率合成技術(shù)在各個領(lǐng)域得到了廣泛的應(yīng)用。由于鎖相環(huán)具有跟蹤特性、窄帶濾波特性和鎖定狀態(tài)無剩余頻差存在,因此在頻率合成技術(shù)中采用鎖相環(huán)路可以產(chǎn)生頻率準(zhǔn)確度很高的振蕩信號源。

2018-12-21 08:50:00 6981

6981

的問題進(jìn)行了討論。 引言 鎖相環(huán)(PLL)技術(shù)在眾多領(lǐng)域得到了廣泛的應(yīng)用。如信號處理,調(diào)制解調(diào),時鐘同步,倍頻,頻率綜合等都應(yīng)用到了鎖相環(huán)技術(shù)。傳統(tǒng)的鎖相環(huán)由模擬電路實現(xiàn),而全數(shù)字鎖相環(huán)(DPLL)與傳統(tǒng)的模擬電路實現(xiàn)的PLL相比,具有精度高

2018-10-25 09:17:13 8237

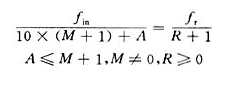

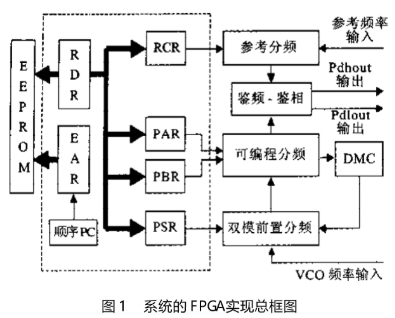

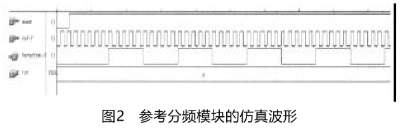

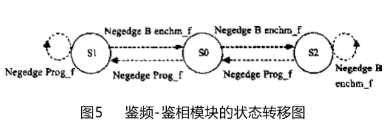

8237 數(shù)字鎖相環(huán)頻率合成系統(tǒng)的工作原理是:鎖相環(huán)對高穩(wěn)定度的基準(zhǔn)頻率(通常由晶體振蕩器直接或經(jīng)分頻后提供)進(jìn)行精確鎖定,環(huán)內(nèi)串接可編程的分頻器,通過編程改變分頻器的分頻比,使環(huán)路總的分頻比為N(可通過編程改變),從而環(huán)路穩(wěn)定的輸出 N倍的基準(zhǔn)頻率,而整個程序和系統(tǒng)的控制是要由CPU來完成的。

2020-07-23 16:47:49 1208

1208

該文章是完全原創(chuàng),用最簡潔的語言講清楚FPGA實現(xiàn)負(fù)反饋的精要。震撼!FPGA實現(xiàn)負(fù)反饋控制純數(shù)字鎖相環(huán)!.zip (225.26 KB )

2019-04-30 04:50:41

及打算進(jìn)階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性學(xué)習(xí)的機(jī)會。

系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對個人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,鎖相環(huán)使用教程。話不多

2023-06-14 18:09:08

,能夠減少對硬件電路參數(shù)的依賴,易于實現(xiàn),而且控制方便。所以在逆變器并網(wǎng)中應(yīng)用很多,但是數(shù)字鎖相環(huán)也存在穩(wěn)定性差,對過零檢測電路要求高的問題。下面結(jié)合筆者所作光伏并網(wǎng)逆變器的結(jié)構(gòu),提出了增加鎖相環(huán)穩(wěn)定性

2018-12-03 14:01:24

堆疊著鑒相、同相積分、中相積分、濾波等專用名詞。這些概念距離硬件設(shè)計實現(xiàn)數(shù)字鎖相環(huán)較遠(yuǎn)。Div20PLL Port(clock : in std_logic; --80M local clkflow

2012-01-12 15:29:12

數(shù)字鎖相環(huán)設(shè)計源程序PLL是數(shù)字鎖相環(huán)設(shè)計源程序, 其中, Fi是輸入頻率(接收數(shù)據(jù)), Fo(Q5)是本地輸出頻率.目的是從輸入數(shù)據(jù)中提取時鐘信號(Q5), 其頻率與數(shù)據(jù)速率一致, 時鐘上升沿鎖定在數(shù)據(jù)的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

問一下大家,labview的鎖相環(huán)怎么設(shè)計,我不知道怎么設(shè)計NCO,計算頻率控制字的時候需要系統(tǒng)時鐘頻率,但是這個不知道怎么弄,大家有知道的嗎,幫一下忙,謝謝!

2017-06-20 10:36:08

保證環(huán)路所要求的性能, 增加系統(tǒng)的穩(wěn)定性。壓控振蕩器受濾波器輸出的電壓控制, 使得壓控振蕩器的頻率向輸入信號的頻率靠攏, 也就是使差拍頻率越來越低, 直至消除頻率差而鎖定。鎖相環(huán)在開始工作時, 通常輸入

2022-06-22 19:16:46

頻率合成器的主要性能指標(biāo)鎖相環(huán)頻率合成器原理鎖相環(huán)頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

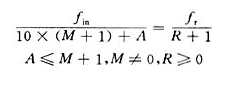

及可編程分頻器三部分組成。其中可編程分頻器是單片微機(jī)與鎖相環(huán)之間的接口,同時也是組成數(shù)字鎖相頻率合成器的關(guān)鍵部件,在移動通信陸地電臺等領(lǐng)域有著廣泛的應(yīng)用。</p><

2010-03-16 10:59:24

隨著現(xiàn)代電子技術(shù)的發(fā)展,具有高穩(wěn)定性和準(zhǔn)確度的頻率源已經(jīng)成為通信、雷達(dá)、儀器儀表、高速計算機(jī)及導(dǎo)航系統(tǒng)的主要組成部分。高性能的頻率源可通過頻率合成技術(shù)獲得。隨著大規(guī)模集成電路的發(fā)展,鎖相式頻率合成

2019-06-20 06:24:14

硬件鎖相環(huán)和軟件鎖相環(huán),這個很好理解,很多東西原來都是直接用硬件電路搞出來,現(xiàn)在有可編程器件了,再利用軟件來實現(xiàn)。傳統(tǒng)的硬件鎖相環(huán)在如諧波、頻率突變、相位突變等電壓畸變以及三相電壓不平衡情況下,很難

2015-01-04 22:57:15

ADI是高性能模擬器件供應(yīng)商,在鎖相環(huán)領(lǐng)域已有十多的的設(shè)計經(jīng)驗。到目前為止,ADI的ADF系列鎖相環(huán)產(chǎn)品所能綜合的頻率可達(dá)8GHz,幾乎能夠涵蓋目前所有無線通信系統(tǒng)的頻段。ADF系列PLL頻率合成

2018-10-31 15:08:45

ADI是高性能模擬器件供應(yīng)商,在鎖相環(huán)領(lǐng)域已有十多的的設(shè)計經(jīng)驗。到目前為止,ADI的ADF系列鎖相環(huán)產(chǎn)品所能綜合的頻率可達(dá)8GHz,幾乎能夠涵蓋目前所有無線通信系統(tǒng)的頻段。ADF系列PLL頻率合成

2018-11-06 09:03:16

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

鎖相環(huán)的原理,特性與分析所謂鎖相環(huán)路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環(huán)路自身調(diào)整作用,實現(xiàn)頻率準(zhǔn)確跟蹤的系統(tǒng),稱該系統(tǒng)為鎖相環(huán)路,簡稱環(huán)路,通常用PLL 表示。

2008-08-15 13:18:46

、壓控振蕩器(VCO) 四、環(huán)路濾波器(LPF) 五、固有頻率ωn和阻尼系數(shù)x 的物 理意義 六、同步帶和捕捉帶 ?第二部分:鎖相環(huán)實驗 ?實驗一、PLL參數(shù)測試 ?一、壓控靈敏度KO的測量 ?二

2011-12-21 17:35:00

本人在進(jìn)在做鎖相環(huán)的仿真,進(jìn)行頻率跟蹤的用的,可是怎么做都放不出波形,可有會仿真鎖相環(huán)的?

2014-06-23 11:14:38

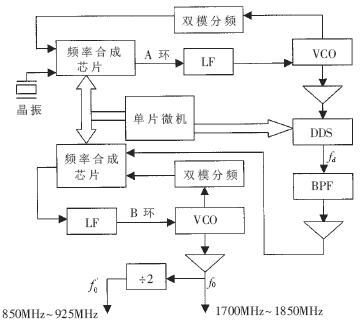

的頻帶,但是時鐘頻率較高的DDS價格昂貴。采用鎖相環(huán)合成,雜散性能與相位噪聲性能較好,可實現(xiàn)的工作頻帶寬,但頻率切換速度較慢,跳頻時間較長。由于系統(tǒng)并沒有對頻率切換速度提出過高要求,因此從價格方面考慮

2019-06-21 06:32:34

如題,AD9957的鎖相環(huán)一直失鎖,不用鎖相環(huán)輸出點頻信號時正常的,用了鎖相環(huán)后,PLL_LOCK信號一直為低,sync_clk輸出信號也不是穩(wěn)定的周期信號,環(huán)路濾波器的值有點誤差,因為現(xiàn)有的器件沒有那么精確的電容電阻值,問下鎖相環(huán)的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

LabVIEW鎖相環(huán)(PLL) 鎖相環(huán)是一種反饋電路,其作用是使得電路上的時鐘和某一外部時鐘的相位同步。PLL通過比較外部信號的相位和由壓控晶振(VCXO)的相位來實現(xiàn)同步的,在比較的過程中,鎖相環(huán)

2022-05-31 19:58:27

原理實現(xiàn)的頻率及相位的同步技術(shù),其作用是將電路輸出的時鐘與其外部的參考時鐘保持同步。當(dāng)參考時鐘的頻率或相位發(fā)生改變時,鎖相環(huán)會檢測到這種變化,并且通過其內(nèi)部的反饋系統(tǒng)來調(diào)節(jié)輸出頻率,直到兩者

2021-11-04 08:57:18

概述:SC9257是杭州士蘭微電子生產(chǎn)的一款數(shù)字調(diào)諧系統(tǒng)鎖相環(huán)(PLL FOR DTS)。該SC9257是鎖相環(huán)(PLL)的LSI數(shù)字調(diào)諧系統(tǒng)(DTS)與內(nèi)置的2模數(shù)預(yù)分頻器。所有功能都通過3根串行

2021-05-18 07:27:48

信號源的任何應(yīng)用的理想選擇,并且利用微帶或陶瓷諧振器拓?fù)浣Y(jié)構(gòu)可提供出色的相位噪聲性能。測試儀器雷達(dá)系統(tǒng)SFS10500H-LF鎖相環(huán)SFS10625H-LF鎖相環(huán)SFS10640H-LF鎖相環(huán)

2021-04-03 17:05:46

FPGA技術(shù)、鎖相環(huán)技術(shù)、頻率合成技術(shù),設(shè)計出了一個整數(shù)/半整數(shù)頻率合成器,能夠方便地應(yīng)用于鎖相環(huán)教學(xué)中,有一定的實用價值。

2019-06-25 06:36:13

介紹了鎖相環(huán)路的基本原理,分析了集成鎖相環(huán)芯片ADF4106的工作特性,給出了集成鎖相環(huán)芯片ADF4106的一個應(yīng)用實例,為高頻頻率合成器的設(shè)計提供了很好的思路。 關(guān)鍵詞:ADF4106,鎖相環(huán),頻率合成器,環(huán)路濾波器

2019-07-04 07:01:10

本文設(shè)計了一種寬頻率范圍的CMOS鎖相環(huán)(PLL)電路,通過提高電荷泵電路的電流鏡鏡像精度和增加開關(guān)噪聲抵消電路,有效地改善了傳統(tǒng)電路中由于電流失配、電荷共享、時鐘饋通等導(dǎo)致的相位偏差問題。設(shè)計了

2019-07-08 07:37:37

全數(shù)字鎖相環(huán)的設(shè)計及分析 1 引 言 鎖相環(huán)是一種能使輸出信號在頻率和相位上與輸入信號同步的電路,即系統(tǒng)進(jìn)入鎖定狀態(tài)(或同步狀態(tài))后,震蕩器的輸出信號與系統(tǒng)輸入信號之間相差為零,或者保持為常數(shù)

2010-03-16 10:56:10

有沒有大神有用Verilog代碼寫的數(shù)字鎖相環(huán)程序呀,求 。謝謝

2017-07-05 22:54:56

=rgb(0, 66, 118) !important] 鎖相環(huán)是個相位誤差控制系統(tǒng)。它比較輸入信號和壓控振蕩器輸出信號之間的相位差,從而產(chǎn)生誤差控制電壓來調(diào)整壓控振蕩器的頻率,以達(dá)到與輸入信號同頻

2019-03-17 06:00:00

HDL硬件描述語言對優(yōu)化前后的算法進(jìn)行了編碼實現(xiàn)。仿真和實驗結(jié)果表明,優(yōu)化后的數(shù)字三相鎖相環(huán)大大節(jié)省了FPGA的資源,并能快速、準(zhǔn)確地鎖定相位,具有良好的性能。關(guān)鍵詞:FPGA;三相鎖相環(huán);乘法復(fù)用;CORDIC

2019-06-27 07:02:23

一、內(nèi)容繼續(xù)無霍爾的學(xué)習(xí),根據(jù)原理及仿真,了解相關(guān)原理和實現(xiàn)方法。二、知識點1.基于鎖相環(huán)的轉(zhuǎn)子位置估計反正切函數(shù)的轉(zhuǎn)子位置估算由于是根據(jù)估算的擴(kuò)展反電動勢進(jìn)行計算的,但是由于滑模控制在滑動模態(tài)下

2021-08-27 06:54:13

(DS)、鎖相環(huán)頻率合成技術(shù)(PLL)、直接數(shù)字頻率合成技術(shù)(DDS)、混合頻率合成技術(shù)四種實現(xiàn)方式,其中鎖相環(huán)頻率合成器是射頻電路中最常使用的一種結(jié)構(gòu),相比于其他幾種結(jié)構(gòu),PLL結(jié)構(gòu)能夠在有限的功耗限制

2018-09-06 14:32:13

基于單片機(jī)和鎖相環(huán)MC14046頻率合成器的設(shè)計,要求是產(chǎn)生頻率在1MHZ左右,求大家指點。

2012-04-11 14:01:59

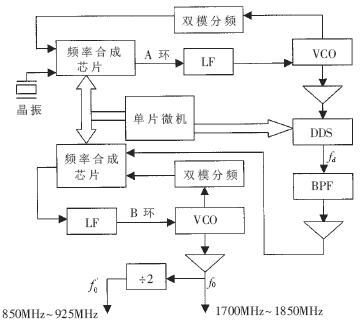

本文設(shè)計了一種多環(huán)鎖相頻率合成器。多環(huán)鎖相環(huán)路有直接數(shù)字頻率合成(DDS)環(huán)路和鎖相頻率合成環(huán)路(PLL)組成。充分利用兩個不同環(huán)路的優(yōu)點,既保證了高的輸出頻率,又得到了較高的頻率分辨率。【關(guān)鍵詞

2010-05-13 09:09:53

隨著集成電路技術(shù)的不斷進(jìn)步,數(shù)字化應(yīng)用逐漸普及,在數(shù)字通信、電力系統(tǒng)自動化等方面越來越多地運用了數(shù)字鎖相環(huán)。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現(xiàn)、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現(xiàn)了一個全數(shù)字鎖相環(huán)功能模塊,構(gòu)成了片內(nèi)鎖相環(huán)。

2019-10-10 06:12:52

。本文結(jié)合FPGA技術(shù)、鎖相環(huán)技術(shù)、頻率合成技術(shù),設(shè)計出了一個整數(shù)/半整數(shù)頻率合成器,能夠方便地應(yīng)用于鎖相環(huán)教學(xué)中,有一定的實用價值。那么有誰知道具體該如何利用FPGA設(shè)計PLL頻率合成器嗎?

2019-07-30 07:55:22

鎖相環(huán)是什么工作原理?如何采用FPGA與頻率綜合器ADF4111相結(jié)合的方法實現(xiàn)數(shù)字鎖相式頻率源的設(shè)計?

2021-04-14 07:00:20

鎖相環(huán)頻率合成器是什么原理?基于CD4046的鎖相環(huán)頻率合成器的設(shè)計

2021-04-12 06:28:35

全數(shù)字鎖相環(huán)由那幾部分組成?數(shù)字鎖相環(huán)的原理是什么?如何采用VHDL實現(xiàn)全數(shù)字鎖相環(huán)電路的設(shè)計?

2021-05-07 06:14:44

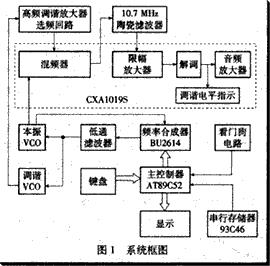

控制用微處理器的主要性能有哪些?處理器在調(diào)頻(FM)調(diào)諧器中的應(yīng)用是什么?數(shù)字調(diào)諧系統(tǒng)有哪些性質(zhì)?怎樣去設(shè)計一種基于PLL(鎖相環(huán))合成器的數(shù)字調(diào)諧系統(tǒng)?

2021-08-17 07:03:36

,與傳統(tǒng)鎖相相比,能夠減少對硬件電路參數(shù)的依賴,易于實現(xiàn),而且控制方便。所以在逆變器并網(wǎng)中應(yīng)用很多,但是數(shù)字鎖相環(huán)也存在穩(wěn)定性差,對過零檢測電路要求高的問題。下面結(jié)合筆者所作光伏并網(wǎng)逆變器的結(jié)構(gòu),提出

2018-12-05 09:53:26

fpga中的用鎖相環(huán)產(chǎn)生時鐘信號相比于用計數(shù)器進(jìn)行分頻有哪些優(yōu)點,看fpga中鎖相環(huán)的結(jié)構(gòu),其前期的輸入信號和后期的輸出信號不也是通過計數(shù)器進(jìn)行分頻實現(xiàn)的嗎

2014-10-06 10:46:05

模擬鎖相環(huán)與數(shù)字鎖相環(huán)的主要區(qū)別在哪里?

2023-04-24 10:48:52

經(jīng)典數(shù)字鎖相環(huán)路結(jié)構(gòu)及工作原理是什么?改進(jìn)的數(shù)字鎖相環(huán)結(jié)構(gòu)及工作原理是什么怎樣對改進(jìn)的數(shù)字鎖相環(huán)進(jìn)行仿真?

2021-04-20 06:47:12

數(shù)字鎖相環(huán)頻率合成系統(tǒng)的工作原理CPU控制數(shù)字鎖相環(huán)頻率合成系統(tǒng)FPGA實現(xiàn)

2021-04-09 06:20:37

大家好,我的課題是要用FPGA做一個高精度鎖相環(huán)。這個數(shù)字鎖相環(huán)的工作原理為:正弦模擬信號通過低通濾波器后,經(jīng)過模數(shù)轉(zhuǎn)換器(ADC)轉(zhuǎn)化為數(shù)字信號,與NCO(數(shù)控振蕩器) 的輸出信號相乘后濾波,從而

2016-08-15 11:31:56

最近在搞鎖相環(huán),總是有問題,功能無法實現(xiàn),特求一個可以鎖住輸入信號頻率為0.01~1Hz的數(shù)字鎖相環(huán)程序參考參考,最好有注。參數(shù)達(dá)不到也沒關(guān)系,我可以自己修改。謝謝大神們啦!

2016-08-28 17:33:56

本文介紹了電荷泵鎖相環(huán)電路鎖定檢測的基本原理,通過分析影響鎖相環(huán)數(shù)字鎖定電路的關(guān)鍵因子,推導(dǎo)出相位誤差的計算公式。并以CDCE72010 為例子,通過實驗驗證了不合理的電路設(shè)計或外圍電路參數(shù)是如何影響電荷泵鎖相環(huán)芯片數(shù)字鎖定指示的準(zhǔn)確性。

2021-04-20 06:00:37

數(shù)字鎖相環(huán)的參考信號可以是正弦信號嗎

2018-08-18 06:55:49

工程師您好:ADF4351內(nèi)部集成VCO振蕩器,如果結(jié)合外部環(huán)路濾波器和外部參考時鐘頻率能構(gòu)成數(shù)字鎖相環(huán)嗎?如果不能是不是因為ADF4351內(nèi)部沒有鑒相器,如果我想做數(shù)字鎖相環(huán)還要和ADF4002合用嗎?能實現(xiàn)位同步嗎?期待您們的答復(fù)!

2018-09-14 14:23:29

幾乎每個RF和微波系統(tǒng)都需要頻率合成器。頻率合成器產(chǎn)生本振信號以驅(qū)動混頻器、調(diào)制器、解調(diào)器及其他許多RF和微波器件。頻率合成器常被視為系統(tǒng)的心跳,創(chuàng)建方法之一是使用鎖相環(huán)(PLL)頻率合成器。傳統(tǒng)上

2019-07-31 06:55:58

驅(qū)動高壓鎖相環(huán)頻率合成器電路的VCO

2021-01-11 06:02:04

本帖最后由 gk320830 于 2015-3-7 16:40 編輯

高速數(shù)字鎖相環(huán)的原理及應(yīng)用

2012-08-17 10:47:04

智能全數(shù)字鎖相環(huán)的設(shè)計

摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字

2008-08-14 22:12:51 56

56 智能全數(shù)字鎖相環(huán)的設(shè)計:在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進(jìn)行動態(tài)智能配

2009-06-25 23:32:57 72

72 基于FPGA的全數(shù)字鎖相環(huán)設(shè)計:

2009-06-26 17:30:59 141

141 鎖相環(huán)被廣泛應(yīng)用于電力系統(tǒng)的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數(shù)字鎖相環(huán)。通過對其數(shù)學(xué)模型的分析,闡述了該鎖相環(huán)的各項性能指標(biāo)與設(shè)計參數(shù)的

2010-07-02 16:54:10 30

30 鎖相環(huán)的研究和頻率合成一、實驗?zāi)康模?. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環(huán)基本特性的研究3. 利用鎖相環(huán)實現(xiàn)頻率合成二、鎖相環(huán)原理:

2009-03-06 20:02:52 1939

1939

摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進(jìn)行動態(tài)智

2009-06-20 12:39:32 1408

1408

寬頻帶數(shù)字鎖相環(huán)的設(shè)計及基于FPGA的實現(xiàn)數(shù)字鎖相環(huán)(DPLL)技術(shù)在數(shù)字通信、無線電電子學(xué)等眾多領(lǐng)域得到了極為廣泛的應(yīng)用。與傳統(tǒng)的模擬電路實現(xiàn)的

2009-11-23 21:00:58 1187

1187

集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)

2010-03-23 11:45:44 770

770 數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

背景知識:

隨著數(shù)字電路技術(shù)的發(fā)展,數(shù)字鎖相環(huán)在調(diào)制解調(diào)、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 5474

5474 鎖相環(huán)路由于具有高穩(wěn)定性、優(yōu)越的跟蹤性能及良好的抗干擾性,在頻率合成中得到了廣泛應(yīng)用。但簡單的鎖相環(huán)路對輸出頻率、頻率分辨率等指標(biāo)往往不能滿足要求,所以要對簡單鎖相環(huán)

2011-05-28 13:42:13 943

943

基于FPGA的數(shù)字鎖相環(huán)設(shè)計與實現(xiàn)技術(shù)論文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源碼:用FPGA實現(xiàn)數(shù)字鎖相環(huán)

2016-06-07 15:07:45 37

37 一、設(shè)計目標(biāo) 基于鎖相環(huán)的理論,以載波恢復(fù)環(huán)為依托搭建數(shù)字鎖相環(huán)平臺,并在FPGA中實現(xiàn)鎖相環(huán)的基本功能。 在FPGA中實現(xiàn)鎖相環(huán)的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統(tǒng)計計算,多普勒頻偏

2017-10-16 11:36:45 18

18 鎖相環(huán)路是一種反饋控制電路,簡稱鎖相環(huán)( PLL)。鎖相環(huán)的特點是:利用外部輸入的參考信號控制環(huán)路內(nèi)部振蕩信號的頻率和相位。因鎖相環(huán)可以實現(xiàn)輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環(huán)通常

2020-08-06 17:58:25 24

24 本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實現(xiàn)方式入手.進(jìn)行改進(jìn),并使用VH DL語言建模,使用FPGA進(jìn)行驗證。

2021-01-26 15:03:00 65

65 本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實現(xiàn)方式入手.進(jìn)行改進(jìn),并使用VH DL語言建模,使用FPGA進(jìn)行驗證。

2021-01-26 15:03:00 18

18 用鎖相環(huán)實現(xiàn)超快頻率切換

2021-05-18 20:29:01 9

9 所設(shè)計的頻率合成器,要求相位噪聲低,輸出頻率800~1 000 MHz,共88個波道,通過單片機(jī)發(fā)送的頻率控制字進(jìn)行波道選擇。在對比各種大規(guī)模集成頻率合成芯片性能的基礎(chǔ)上,選用了單片大規(guī)模集成鎖相環(huán)頻率合成芯片PE3236作為核心電路,構(gòu)成鎖相式頻率合成器。

2021-05-28 10:30:08 4153

4153

基于FPGA的寬頻帶數(shù)字鎖相環(huán)的設(shè)計與實現(xiàn)簡介說明。

2021-06-01 09:41:14 26

26 數(shù)字調(diào)諧系統(tǒng)是現(xiàn)代收發(fā)信機(jī)的核心,其性能直接影響通信質(zhì)量的好壞,其主要部分是集成鎖相式頻率合成器。集成鎖相環(huán)與微處理器結(jié)合,可由微機(jī)控制完成頻率合成器的全部功能。

2021-06-14 17:29:00 3373

3373

模擬鎖相環(huán)和數(shù)字鎖相環(huán)的主要區(qū)別在于它們的控制方式不同。模擬鎖相環(huán)是通過模擬電路來控制頻率和相位,而數(shù)字鎖相環(huán)是通過數(shù)字信號處理技術(shù)來控制頻率和相位。此外,模擬鎖相環(huán)的精度較低,而數(shù)字鎖相環(huán)的精度較高。

2023-02-15 13:47:53 3623

3623 鎖相環(huán)頻率合成器的優(yōu)缺點? 鎖相環(huán)頻率合成器,又稱為PLL(Phase Locked Loop),是一種廣泛應(yīng)用的電路,能夠?qū)⑤斎胄盘柕?b class="flag-6" style="color: red">頻率合成為電路所需要的頻率,并且能夠實現(xiàn)對信號的相位和頻率

2023-09-02 14:59:33 1216

1216 數(shù)字鎖相環(huán)(DigitalPhase-LockedLoop,簡稱DPLL)是一種基于反饋控制的技術(shù),用于實現(xiàn)精確的時序控制和相位同步。通過相位比較、頻率差計算、頻率控制、濾波和循環(huán)控制,它能夠完成

2024-01-02 17:20:25 701

701

電子發(fā)燒友App

電子發(fā)燒友App

評論