引言

多節點系統,在目前的很多電子系統應用場合都可以看到。這種多節點系統由于具有結構可擴展性、功能配置的靈活性以及便于查找故障節點等良好的可維護性得到了越來越廣泛的應用。通常,多節點系統各個節點的主要硬件構成有很大的相似性。特別是近年來, FPGA 這個強大的平臺讓多節點系統各個節點的硬件構成擁有了更廣泛的通用性。尤其是隨著 IP 核技術的推廣,再加上一些功能強大的 CPU 核的出現,如 Xilinx 公司提供的 PicoBlaze 和 MicroBlaze 等,使得目前的許多系統的主要功能都可以由大容量的 FPGA 實現,而無需再使用比較昂貴的高性能微處理器。

對于節點系統,這將大大降低系統成本。對于由大容量 FPGA 構成的多節點系統,系統的升級是一個費時費力的工作。此時,FPGA 的遠程升級能力就顯得尤為重要。對于包含 arm、DSP、PowerPC 等高性能嵌入式微處理器的多節點系統,使用這些嵌入式微處理器,采用 SELECTMAP 對 FPGA 進行加載并實現遠程升級,無需增加過多的外部器件,是非常經濟和高效的。但對于核心器件就是大容量 FPGA 的系統,如果由 FPGA 本身來接收升級數據并寫入存儲配置數據的非易失性存儲器,一旦升級失敗,將無法再次升級,從而限制了它在許多需要高可靠性要求或者維護人員不便于到達的場合的應用;而如果單純為了實現系統的遠程升級而加入價格昂貴的嵌入式微處理器,又會較大地增加系統成本和復雜性。針對這種情況,筆者設計了利用 ATmega64 單片機和 RS485 總線,加上接入以太網的主控計算機構成的遠程升級系統,解決了上述問題。

1 系統設計

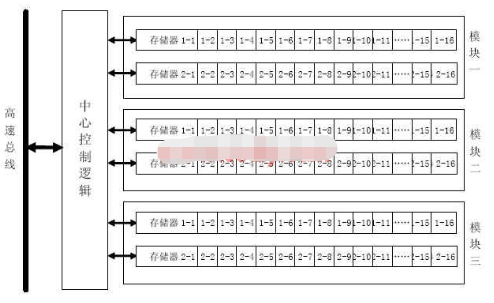

1.1 系統結構設計

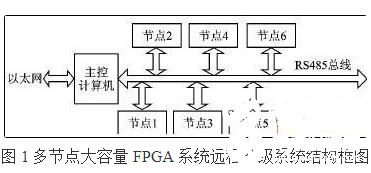

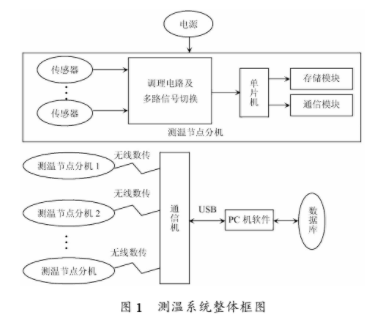

遠程升級系統主要由一臺接入以太網的主控計算機、半雙工 RS485 總線以及各個子節點構成,組成結構如圖 1 所示。主控計算機通過以太網從外部獲取整個系統各個節點的升級數據,然后通過 RS485 總線向各個子節點發送其對應的升級數據,完成多節點系統的升級。RS485 總線采用一主多從的半雙工方式,主控計算機為總線的主控制器,只能由它向各個節點發起通信連接,其余子節點只能響應主控計算機的控制命令。

1.2 節點升級原理

各個節點通過 RS485 總線與主控計算機相連,在無升級數據時,總線可以用來傳輸主控計算機對各個節點的查詢和控制命令。主控計算機與各個節點的通信協議可以采用具有查詢控制幀、應答幀和數據幀 3 種幀類型的協議。只有主控計算機可以發送查詢控制幀,查詢或設定各個節點的遠程升級狀態或工況信息。子節點接收主控計算機的命令和數據,發送應答幀,并完成自身的升級。

2 子節點的硬件設計

2.1 子節點硬件結構框圖

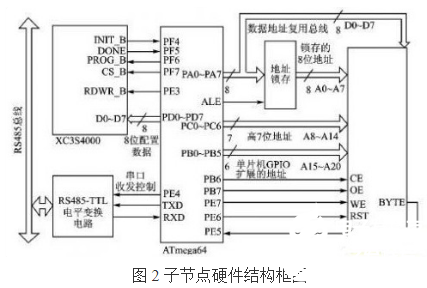

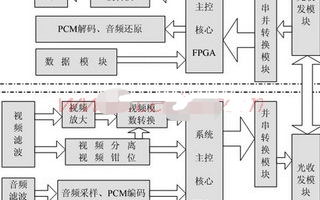

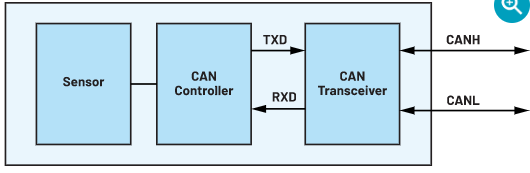

如圖 2 所示,以一個由 Xilinx 公司的 XC3S4000 大容量 FPGA 構成的系統為例,遠程升級系統子節點的硬件電路主要包括: ATmega64 單片機,用于存儲大容量 FPGA 配置數據的 Flash,以及接入 RS485 總線的半雙工總線收發器。ATmega64 單片機用于實現對大容量 FPGA XC3S4000 的加載,以及從 RS485 總線接收 FPGA 的升級數據并寫入擁有 2 MB 存儲空間的 Flash 存儲器 SST36VF1601C 中。RS485TTL 電平變換電路采用 RS485 收發器 SP485R。

2.2 子節點硬件設計說明

在子節點的硬件設計中,ATmega64 單片機是實現整個升級功能的關鍵。ATmega64 是基于增強的 AVR RISC 結構的低功耗 8 位 CMOS 微控制器。由于其先進的指令集以及單時鐘周期指令執行時間,ATmega64 的數據吞吐率高達 1 MIPS/MHz,從而可以緩解系統在功耗和處理速度之間的矛盾。AVR 內核具有豐富的指令集和 32 個通用工作寄存器,并且所有的寄存器都直接與算術邏輯單元(ALU)相連接,使得 1 條指令可以在 1 個時鐘周期內同時訪問 2 個獨立的寄存器。這種結構大大提高了代碼效率,并且具有比普通的 CISC 微控制器最高至 10 倍的數據吞吐率。ATmega64 有如下特點:

① 64 KB 的系統內可編程 Flash(具有同時讀寫的能力,即 RWW),2 KB 的 EEPROM,4 KB 的 SRAM,32 個通用工作寄存器;

② 53 個通用 I/O 口線;

③ 實時計數器(RTC);

④ 4 個具有比較模式與 PWM 的靈活的定時器 / 計數器(T/C),具有片內振蕩器的可編程看門狗定時器;

⑤ 2 個 USART,面向字節的雙線串行接口(TWI),1 個 SPI 串行端口;

⑥ 8 路 10 位具有可選差分輸入級可編程增益的 ADC;

⑦ 與 IEEE 1149.1 標準兼容的,可用于訪問片上調試系統及編程的 JTAG 接口。

ATmega64 是以 Atmel 高密度非易失性存儲器技術生產的。片內 ISP Flash 允許程序存儲器通過 ISP 串行接口(或者通用編程器)進行編程,也可以通過運行于 AVR 內核之中的引導程序進行編程。通過將 8 位 RISC CPU 與系統內可編程的 Flash 集成在一個芯片內,ATmega64 成為一個功能強大的單片機,為許多嵌入式控制應用提供了靈活而低成本的解決方案。

利用 ATmega64 單片機實現對大容量 FPGA 的遠程升級,涉及的主要技術問題有三點:一是如何將 ATmega64 單片機接入 RS485 總線;二是在接收到升級數據后和加載 FPGA 時,如何利用 ATmega64 單片機對大容量的 Flash 存儲器進行讀寫操作;三是 ATmega64 單片機實現 FPGA 的 SELECTMAP 加載。

2.2.1 RS485 接口電路設計

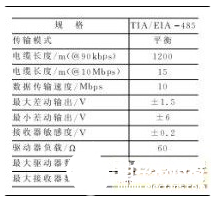

如表 1 所列, RS485 總線標準具有控制方便、價格低廉以及高噪聲抑制、相對高的傳輸速率、傳輸距離遠和寬共模范圍等優點。在過去的 20 年時間里,建議性標準 RS485 作為一種多點差分數據傳輸的電氣規范,被應用在許多不同的領域作為數據傳輸鏈路。

表 1 TIA/EIA485 串行通信標準的性能

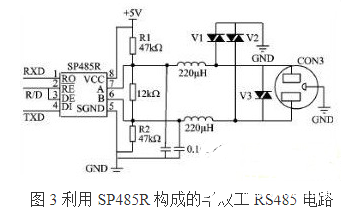

子節點的 ATmega64 單片機通過 Sipex 公司設計生產的高性能 RS485 收發器接入 RS485 總線。

SP485R 是一款與流行的標準 RS485 芯片完全兼容,而且包含更高的 ESD 保護和高接收器輸入阻抗等性能的 RS485 收發器。接收器輸入高阻抗可以使 400 個收發器接到同一條傳輸線上,又不會引起 RS485 驅動器信號的衰減。該收發器的特點如下:

① 允許超過 400 個收發器接到同一條傳輸線上;

② 接收器輸入高阻抗(標準值 RIN=150 kΩ);

③ 半雙工配置與工業標準引腳一致;

④ 共模輸入電壓范圍為 -7~+12 V;

⑤ 低功耗(250 mW);

⑥ 獨立驅動器和接收器使能引腳。

其典型應用電路如圖 3 所示。

ATmega64 單片機的標準串行口通過 RXD 直接連接 SP485R 芯片的 RO 引腳,通過 TXD 直接連接 SP485R 芯片的 DI 引腳。由單片機輸出的 R/D 信號直接控制 SP485R 芯片的發送器 / 接收器使能:R/D 信號為 1,SP485R 芯片的發送器有效,接收器禁止,此時單片機可以向 RS485 總線發送數據字節;R/D 信號為 0,SP485R 芯片的發送器禁止,接收器有效,單片機可以接收來自 RS485 總線的數據字節。上拉電阻 R1、下拉電阻 R2 用于保證未連接總線時的 SP485R 芯片處于空閑狀態,以提高每個 RS485 節點的工作可靠性。6.8 V 的 TVS 管 V1、V2、V3 用來保護 RS485 總線,避免 RS485 總線受外界干擾時產生的高壓損壞 RS485 收發器。

2.2.2 ATmega64 存儲空間的擴展

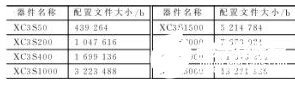

ATmega64 的尋址空間為 64 KB,利用 ATmega64 自身的尋址系統,只能訪問 0x0000~0xFFFF 的地址空間。顯然,這對于存儲和加載大容量 FPGA 的配置數據是遠遠不夠的。以 Xilinx 公司的 Spartan3 系列 FPGA 為例,其配置數據所需的存儲空間如表 2 所列。

表 2 Spartan3 系列 FPGA 配置文件大小

以 XC3S4000 型 FPGA 為例,它的配置文件所需的存儲空間約為 1.35 MB,已遠遠超出了 ATmega64 單片機的尋址空間。因此,為了能夠利用 ATmega64 單片機來實現對 FPGA 配置數據的讀寫,必須對其尋址空間進行擴展。擴展的硬件連接框圖如圖 2 中的單片機與 Flash 的連接部分所示。

本設計中是使用通用 I/O 來擴展 ATmega64 單片機的尋址空間的。ATmega64 單片機的總尋址空間為 64 KB,但片內 4 KB 的 SRAM 及各種寄存器占用了前面的部分尋址空間,故其片外存儲器尋址空間是 0x1100~0xFFFF。因此將 Flash 的低 15 位地址直接接到 ATmega64 單片機的低 15 位地址總線上,其余 6 位高位地址用單片機的通用 I/O 進行選擇。尋址時單片機的專用地址口只輸出 0x8000~0xFFFF 的地址數據,與通用 I/O 輸出的地址組合后給出 Flash 的讀寫地址。

通過以上對 ATmega64 單片機尋址空間的擴展方法,可以實現 ATmega64 單片機對合適的 Flash 存儲器的尋址操作,從而解決了大容量 FPGA 配置數據的存儲和讀取問題。

2.2.3 用 ATmega64 實現 FPGA 的 SELECTMAP 加載

Xilinx 公司的 Spartan3 系列 FPGA 加載方式分為 5 種: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

按照 FPGA 是否控制加載過程,加載方式可分為 Master 方式和 Slave 方式;按照加載數據時的數據位寬,可分為 Serial 方式和 Parallel 方式。用于加載的引腳主要有: PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP 和 JTAG 接口(TDI、 TMS、TCK、TDO)。加載過程大體分為 3 個步驟:配置的建立、配置數據的加載和加載完成。

SELECTMAP 即 Slave Parallel 方式,是由外部控制器控制 FPGA 的加載過程,并以 8 位數據的形式向 FPGA 寫入加載數據的加載方法。圖 2 中 FPGA 與 ATmega64 的連接部分為 ATmega64 單片機采用 SELECTMAP 方式對 FPGA 進行加載的硬件連接框圖,具體實現過程如下:

ATmega64 通過將 FPGA 的 PROG_B、CS_B 和 RDWR_B 引腳置低來開啟加載過程,FPGA 在 PROG_B 置低后開始清除內部配置 RAM,并將 INIT_B 腳置低。PROG_B 重新置 1 后,在 INIT_B 由低變高的上升沿,FPGA 采樣 M[0~2]引腳獲取配置方式信息。 ATmega64 監視 FPGA 的 INIT_B 腳,當 INIT_B 腳由低變高時,說明 FPGA 已經完成了內部配置 RAM 的清除工作,并準備好接收配置數據。在 ATmega64 給出的 CCLK 配置時鐘的上升沿,配置數據 D[0~7]寫入配置 RAM。當 FPGA 接收完所有的配置數據后,DONE 引腳被 FPGA 置為高電平。ATmega64 可以通過監視 DONE 引腳來判斷 FPGA 是否加載完成。對于 Spartan3 系列的 FPGA,如果配置 FPGA 的 CCLK 的頻率高于 50 MHz,則外部控制器還需要監視 FPGA 的 BUSY 引腳。當 BUSY 腳為高時,說明 FPGA 還未完成上一個配置數據的處理,此時外部控制器需要繼續保持上一個配置數據在 D[0~7]引腳,直至 BUSY 引腳回到低電平。對于本設計的應用,ATmega64 給出的配置時鐘頻率遠低于 50 MHz,不必考慮 BUSY 引腳的控制作用。

3 軟件設計

3.1 主控計算機的軟件設計

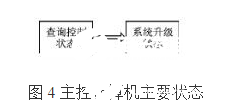

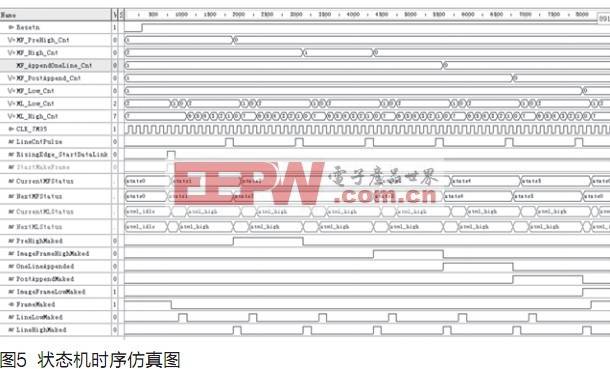

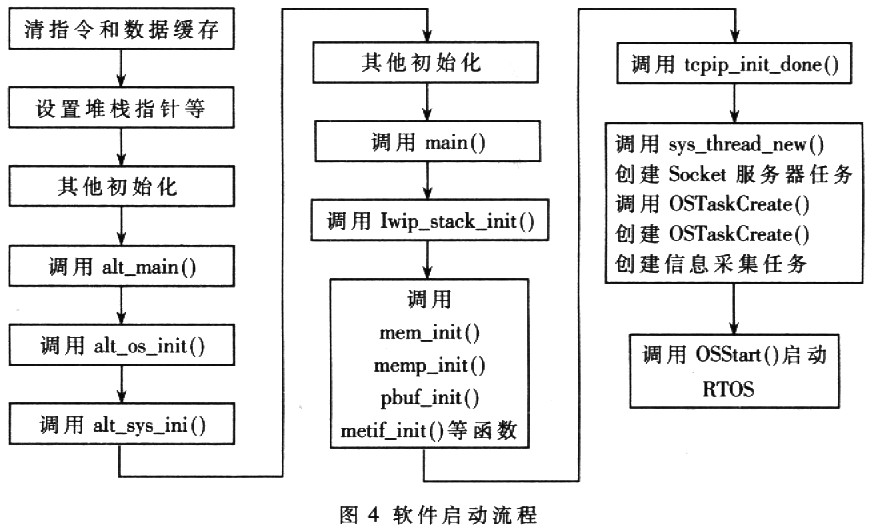

主控制計算機的軟件運行狀態應該分為兩種:一是平時的查詢控制狀態,用來查詢和控制系統中各個節點的工作狀態;二是系統的升級狀態,用來執行對各個子節點的升級控制。如圖 4 所示,這兩種狀態是可以相互轉換的。

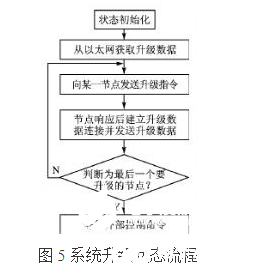

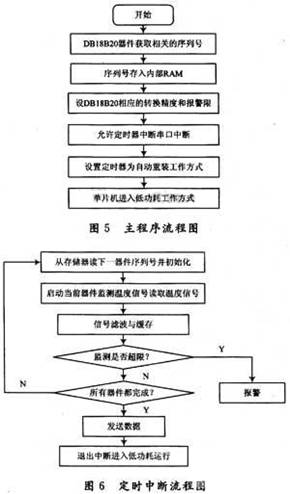

軟件的查詢控制狀態,是由系統所要實現的主要功能決定的,不屬于本文所討論的范疇。在系統的升級狀態,主控計算機先要通過以太網獲得系統各個節點的遠程升級數據,待全部升級數據接收完成后,向系統的一個節點發送升級指令。節點響應并建立起通信連接后,將該節點的升級數據全部發送到該節點。接下來,主控計算機判斷上一個節點是否為最后一個需要升級的節點,如果不是,則繼續進行下一個節點升級數據的傳輸。系統所有的節點升級完成后,等待外部輸入的控制命令。例如,讓整個系統重新啟動,加載新的數據;或暫時不重新啟動而返回查詢控制狀態。軟件流程如圖 5 所示。

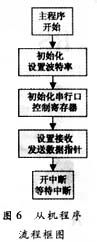

3.2 子節點的軟件設計

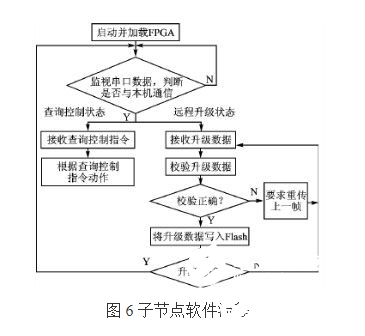

對于子節點的軟件設計,與主控計算機一樣,也分為平時的查詢控制狀態和系統升級狀態,并且它們之間也能夠與主控計算機一起相互轉換;但 ATmega64 單片機還要承擔對 FPGA 的加載任務。開機運行后,ATmega64 單片機先加載子節點 FPGA,使子節點能夠正常工作。子節點正常工作后,監視 RS485 總線并判斷有無對本節點的通信。當主控計算機要求與本節點建立通信連接時,發送反饋信息,與其建立通信連接。子節點根據主控計算機發送的命令,進入查詢控制模式或者遠程升級模式。進入遠程升級模式后,子節點接收主控計算機發來的遠程升級數據,升級數據經過校驗后寫入 Flash。升級完成后繼續等待主控計算機的命令,重新啟動或繼續運行。其具體的軟件設計流程如圖 6 所示。

結語

FPGA 既繼承了 ASIC 的大規模、高集成度、高可靠性的優點,又克服了普通 ASIC 周期長、投資大、靈活性差的缺點,逐步成為許多系統實現的理想選擇。特別是隨著 FPGA 容量和性能的提升,加上其獨特的硬件升級能力,其應用范圍越來越廣。本文所提出的對大容量 FPGA 構成的多節點系統的遠程升級方法,系統構成簡單、技術成熟,而且具有明顯的成本優勢。

電子發燒友App

電子發燒友App

評論