1.?????? 下面關于PLL電路表述正確的是:

A.????? PLL屬于模擬電路,無法用全數字電路實現

B.????? PLL相對于參考時鐘,可以輸出分頻、倍頻、分數頻的時鐘

C.????? PLL輸入的參考時鐘jitter,在PLL輸出是會變大,也有可能變小

D.????? PLL的jitter值等于同步數字電路中clock uncertainty的設定值

解析:jitter在線路傳輸過程中也會被改變。

?

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

?

2.? 如圖所示時序路徑示意圖,橢圓表示組合邏輯,FF1/FF2表示寄存器,A表示數據輸入端口,CLK表示時鐘輸入端口,Z表示數據輸出端口,下圖選項描述正確的是:

A.? 只要在端口CLK上創建時鐘,即可約束A->Z之間的組合邏輯的延時

B.? 只要在端口Z上設置輸出延時,即可約束FF2 -> Z之間的組合邏輯的延時

C.? 只要在端口CLK上創建時鐘,即可約束FF1->FF2之間的組合邏輯的延時

D.? 只要在端口A上設置輸入延時,即可約束A->FF1之間的組合邏輯的延時

?

解析:

?

如上圖所示,共有四條時序路徑。

???? 1:從輸入端口A到FF1的D端;

要滿足的時序要求為(其中Tsetup為寄存器建立時間要求):

Tclk - Tin_delay - T1 - Tsetup > 0;

故只要有了Tclk ,Tin_delay的的信息,EDA工具便可以完成對T1(A->FF1之間的組合邏輯的延時)的約束。

2:從FF1的CLK端到FF2的D端;

要滿足的時序要求為(Tcq(寄存器輸出延時),Tsetup(建立時間要求)):

Tclk - Tcq - T2 - Tsetup > 0;

故只要有了Tclk的信息,EDA便可以根據上面的要求去約束T2(FF1->FF2之間的組合邏輯的延時)。

3:從FF2的CLK端到輸出端口Z;

要滿足的時序要求為:

Tclk - Tcq - T3 - To_delay - Tsetup > 0;

其中Tcq(寄存器輸出延時),Tsetup(為Z端口后面寄存器的建立時間要求)為工藝庫有的信息,因此只要有了Tclk,To_delay(輸出端口延時),EDA就可以去約束T3(FF2 -> Z之間的組合邏輯的延時)。

4:從輸入端口A到輸出端口Z。

?

對于A至Z之間的組合邏輯F的延時的約束。可以看到,A到Z端兩邊有寄存器。對于時序約束條件如下:

Tclk - Tin_delay -TF - To_delay - Tsetup > 0;

如果只是建立了clk,也就只是有了Tclk。而沒有設置端口Z端的輸出延時To_delay ,以及輸入端口A端的延時Tin_delay故因此EDA不能完成對TF的約束。

?

?

3.? 一個線性反饋移位寄存器(LSFR)的特征多項式為F(x)=x4+x+1,初始態為全1,則以下哪些描述是正確的?

A.? 輸出的m-序列為11100101

B.? 該LFSR包含四個寄存器

C.? 寄存器的狀態不會出現全零

D.? 該LFSR能夠產生的不重復序列最長為15位

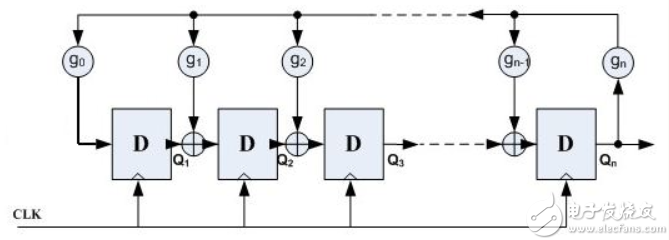

解析:LSFR如下,由n個D觸發器和若干個異或門組成的。

?

?

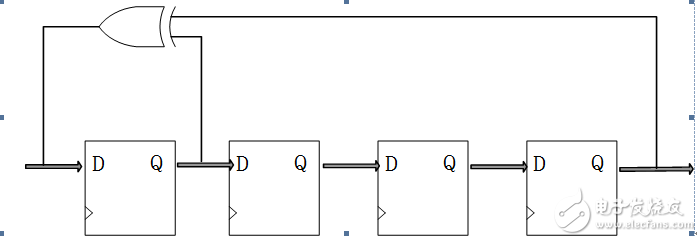

多項式中的指數代表從左至右的抽頭位。第一個和最后一個比特一般相應的是輸入和輸出位。故對于多項式F(x)=x4+x+1對應的電路如下:最開始第一個寄存器初始值為1。

?

故四個寄存器的輸出隨時鐘節拍為:

??????? 1000 -> 1100 -> 1110 -> 1111 -> 0111 -> 1011 -> 0101 -> 1010 -> 1101 -> 0110 -> 0011 -> 1001 -> 0100 -> 0010 -> 0001 -> 1000。

故輸出的序列為 0001111010110010。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

4.?????? 以下關于驗證的描述,正確的是

A. 驗證平臺使用checker檢測DUT的行為,只有知道DUT的輸入輸出信號變化之后,才能根據這些信號變化來判定DUT的行為是否正確

B. SystemVerilog區別于verilog的一個重要特征是其具有面向對象語言的特性:封裝、繼承和多態

C. UVM是synopsys、cadence、mentor等EDA廠商聯合發布的驗證平臺

D. Verilog,SystemVerilog, SystemC, UVM 都是驗證常用的硬件語言

解析:(1)checker是根據當前的輸入值去判斷輸出值的正確性。(2)UVM由mentor發布。(3)UVM不是語言,而是一套驗證系統。

電子發燒友App

電子發燒友App

評論