本文討論如何針對FPGA或微處理器配置各種電壓輸出跟蹤和時序控制選項,來幫助實現靈敏多電源軌系統的正確啟動和關斷。

2015-07-22 17:30:27 1157

1157

微處理器、FPGA、DSP、模數轉換器 (ADC) 和片上系統 (SoC) 器件一般需要多個電壓軌才能運行。為防止出現鎖定、總線爭用問題和高涌流,設計人員需要按特定順序啟動和關斷這些電源軌

2019-08-26 10:33:10 7755

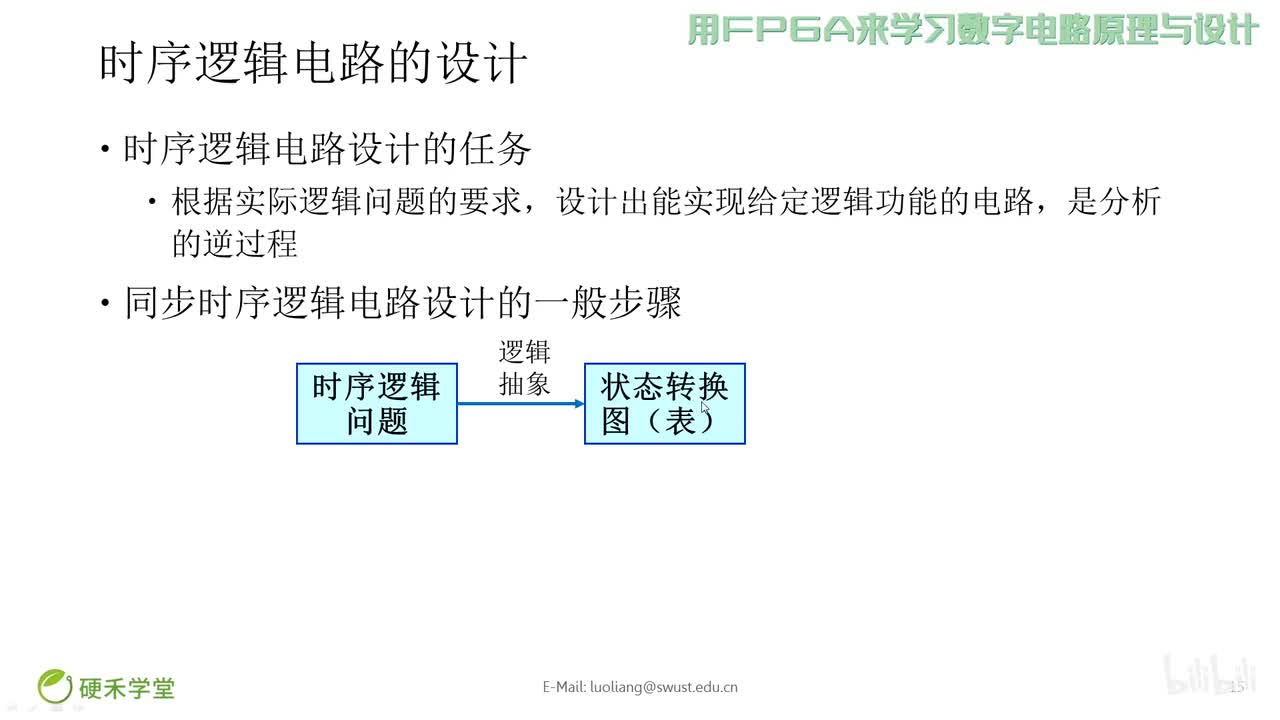

7755 時序路徑 典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。 對于所有的時序路徑,我們都要明確其起點和終點,這4類時序路徑的起點和終點分別如下

2020-11-17 16:41:52 2767

2767

對于每個轉換器,各電壓上電的延遲也會不同。這導致不同電壓域中的電壓爬升不受控制,有可能引起功能問題并損壞系統。

2021-03-24 10:34:46 2500

2500

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1229

1229 時序路徑作為時序約束和時序分析的物理連接關系,可分為片間路徑和片內路徑。

2023-08-14 17:50:02 451

451

技術和外觀質量。電連接器除了電流節氣本身的可靠性以外,應用可靠性要求也至關重要。下面是華碧實驗室為你整理的一些應用可靠性要求。電氣問題 電壓和電流要求在低電流和低電壓條件下要求電鍍層不會產生氧化,因為

2021-12-30 16:05:43

采用AD9789,遇到以下問題,求大神解答!上電手動復位后,對芯片進行寫操作無響應,無論寫入什么數據,讀取狀態寄存器結果都是0xFF,示波器觀察SPI管腳時序無誤,上電后,不進行任何配置,從SDO

2018-11-14 11:02:18

我這邊產品做了100多個,有3-4個出現上電偶爾不輸出現象,更換片子后正常。我想問一下,這個A9854有這個低概率事件會沒有輸出嗎,ARM直連配置芯片并且時序測量正常,片子發熱,Reset引腳高

2018-08-08 07:49:36

相對于其他上電模式,這種上電模式對處理器的性能是否有限制,如工作頻率的限制。2. 圖示中VDD_CORE和VDD_MPU都是1.1V的,若兩者電壓不同該如何上電。3. 上電時序的間隔時間是否有嚴格要求,Datasheet中未給出相關數據。

2018-06-04 06:24:11

請問能提供C6678上電芯片時序控制,以及配置端口電平和時序的Verilog代碼嗎?

2018-06-21 04:32:03

master 的I2S數據。CS5343是一款音頻DAC,其通過I2S信號中的SDOUT的電平狀態來確定主從模式。在CS5343和TAS5731M結合使用時,兩顆芯片精確的上電時序控制是至關重要的,否則

2022-11-09 07:48:07

為什么有不同的上電時序

2023-11-02 08:13:09

如果要求輸出是vdd=3.3v,我是不是可以這樣設計上電順序:首先設置Vgg=-2V,再VCtrl=1V,再Vdd=3.3V,然后調節Vgg,使Igg=140mA,那么它們之間的上電時序是如何控制的。

2023-11-22 07:14:57

關斷波形如下所示,然后管子就壞了,求解

2017-07-14 13:41:21

上運載一個時鐘頻率 fPP 時,這個插入的卡必須要正確地復位(重置)。如果這個熱插入特性是在主機內實現的,則該主機要經得起 VDD 和 VSS 之間短路而不損壞。上電時序如圖:(SPI模式不支持CMD15,詳見SD/MMC card 命令)

2012-01-12 11:06:39

按照TAS5711的datasheet中的上電時序進行上電,芯片正常工作,但是無法編輯寄存器,是時序有問題嗎?我是按照這個上電時序來上電的:AVDD/DVDD上電(3.3V),上電之前A_SEL

2019-08-07 10:02:22

電路,并解決了TPS65105的上電時序問題。實踐表明,該方案是一個穩定可靠的TFT液晶的電源設計方案。 0 引言 TPS65105 是一個混合式DC/DC變換器集成電路芯片。它專門為薄膜式晶體管

2018-09-29 17:01:44

0-50ms,我特意測試了一下DEMO板上的5個電壓上電時序,根據截圖可見實際并非如手冊上講的那么嚴格,截圖是兩兩比較的,前級為黃色,后級為紅色。截圖在附件似乎只要前面4個滿足要求,0.9V都不是很重要,看

2018-05-25 04:36:15

使用TPS65218給ZYNQ7010供電時官方給出的方案是DCDC1和DCDC2給ZYNQ供1.0V,DCDC3供1.5V,DCDC4供1.8V,但是ZYNQ電壓啟動時序中要求1.0V上電時序最早

2016-07-08 16:29:24

ZL6205是如何保障MCU可靠上電的

2021-03-11 06:45:33

2440上電會自動復制nand flash前4k的代碼到內部sram,那么2440是如何知道nand flash的時序的,不同型號的nand flash時序不同,2440如何讀取

2019-04-26 06:04:07

之前參考了control card設計

請教一下,

1,TMS320F2802x的XRS引腳只有上拉電阻,沒有電容,沒問題么?

2,F2802X,F2803X的上電有什么注意的地方?時序或原理圖要做的調整?

3,如果加電后,要對芯片進行復位,是直接拉低一次XRS么?

2018-05-14 11:31:15

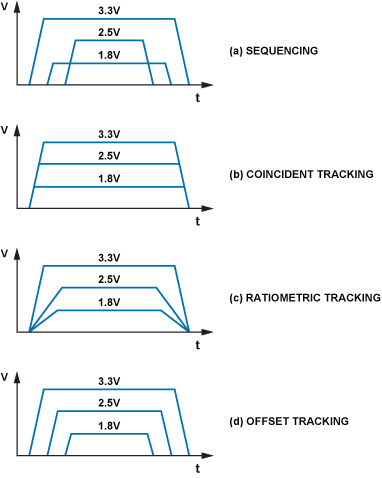

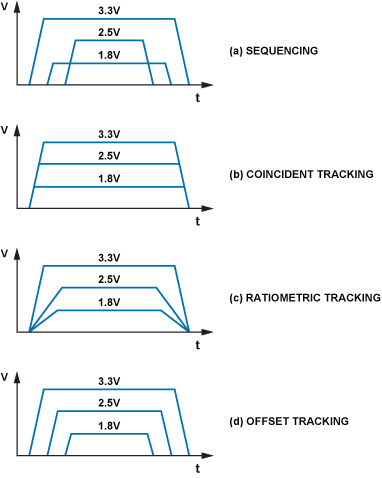

稱為電源時序控制或電源定序,目前有許多解決方案可以有效實現定序。對于需要電壓定序的復雜器件,其內核和模擬模塊的電壓軌可能需要在數字 I/O 電壓軌之前上電。有些設計可能會要求不同的順序,但是

2019-07-30 10:43:06

情況下的行為表現(參見表2),分析可能的問題及原因,并提出一些建議。上電時序問題多種多樣上電時序問題可能出現于多種不同情況。例如,在一個客戶應用中,AD8616配置為緩沖器,在電源建立之前輸入為0 V(圖

2018-05-09 16:32:40

為什么復雜可編程邏輯器件需要重新上電才能工作?如何去解決AVR單片機上電復位不可靠的問題?

2021-07-07 06:53:08

本帖最后由 buhuile 于 2017-6-12 23:17 編輯

用安捷倫示波器測量上電時序或者掉電時序時,觸發電平和時間怎么設置?時間設得不對,抓到的波形是不對的

2017-06-12 23:16:14

用安捷倫示波器測量上電時序或者掉電時序時,觸發電平和時間怎么設置?時間設得不對,抓到的波形是不對的.

2017-06-17 14:41:18

電路被關斷或電源被關斷,系統中只有值守電路在工作。因此,靜態運行下的系統不存在軟件的可靠性問題,其可靠性主要表現在值守電路的抗干擾能力、系統中器件的靜態參數余度,如直流特性參數余度、工作電壓、工作穩定

2021-01-11 09:34:49

GTO導通時,L1中建立電流,因而儲存一定的能量。當GTO關斷后,由于L1中的電流不能突變,D3處于導通狀態。于是儲存在L1中的部分能量便傳送到CL和負載上,旦輸出電壓Eo高于電源電壓Ed。若濾波電容

2018-01-12 09:35:28

為確保芯片能可靠的工作,應用處理器的上下電通常都要遵循一定時序, 本文以i.MX6UL應用處理器為例,設計中就必須要滿足芯片手冊的上電時序、掉電時序,否則在產品使用時可能會出現以下情況,第一,上電

2019-10-18 07:53:02

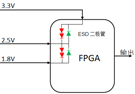

。無論如何,正確的上電和關斷時序控制可以防止閂鎖引發的即時損壞和ESD造成的長期損害。此外,電源時序控制可以錯開上電過程中的浪涌電流,這種技術對于采用限流電源供電的應用十分有用。 本文討論使用分立器件

2018-09-30 16:01:35

LM3881芯片的在上電后不啟用,在電路某個點的電壓輸入后再啟用,可以通過控制EN引腳還是別的腳來實現?該如何實現芯片的關斷和打開功能?假如有個引腳可以控制芯片使能,假如拉低是使芯片無法使用,那上電后還是低,等電路某部分連接后,讓它啟用時序,改變狀態。

2019-07-31 11:17:18

如何實現對DTS中mipi屏幕上電時序的獲取及其發送呢?其程序代碼該怎樣去實現呢?

2022-02-16 07:35:45

問一下啊,在寫時序約束的時候,如何根據設計的要求進行時序上的約束啊,看了好多網上的資料,說的都是有關約束的一些原理。有沒有那位大俠給個設計實例啊!

2023-04-23 11:42:16

我想用adp5050給zynq供電,而zynq各電源有上電時序要求,請問這個應該怎么處理?

2024-01-08 10:57:14

(例如淺休眠模式)也可以讓I/O外設保持上電,同時確保在關斷模式期間芯片外設與內核之間的操作得到驗證。 這使得芯片在保持低功耗的同時,能夠處理激活狀態下的使用情形。 此外,該系統降低了功率開關的成本

2018-12-21 11:34:33

板階 (BLR) 車電可靠性驗證iST宜特可提供汽車電子及零部件一站式整合驗證服務。車用電子測試不僅著重于產品壽命測試,更重要的是,將產品結構及產品組裝質量觀念,帶入試驗中,例如推拉力測試、錫球接合

2018-09-06 16:56:38

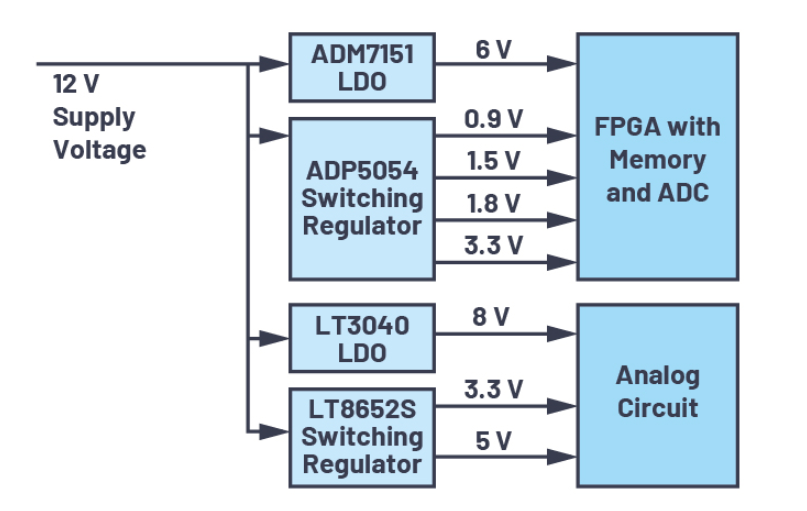

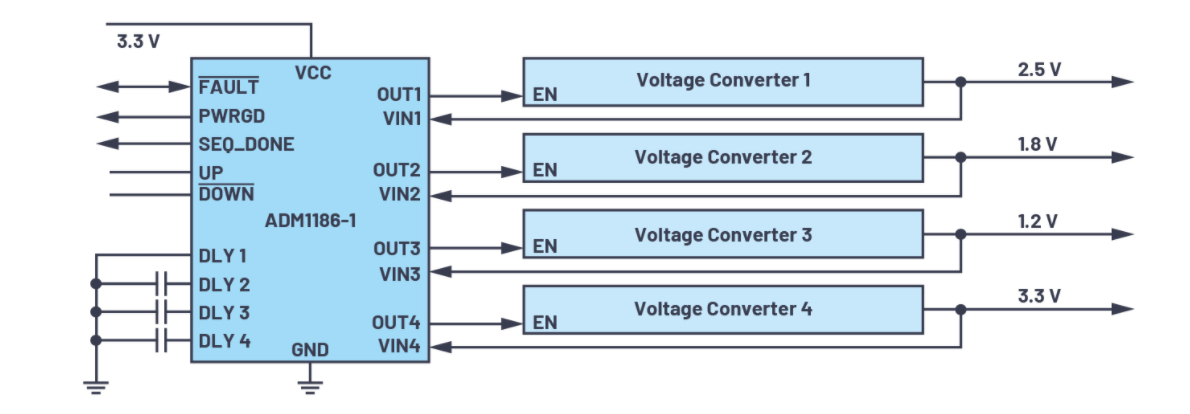

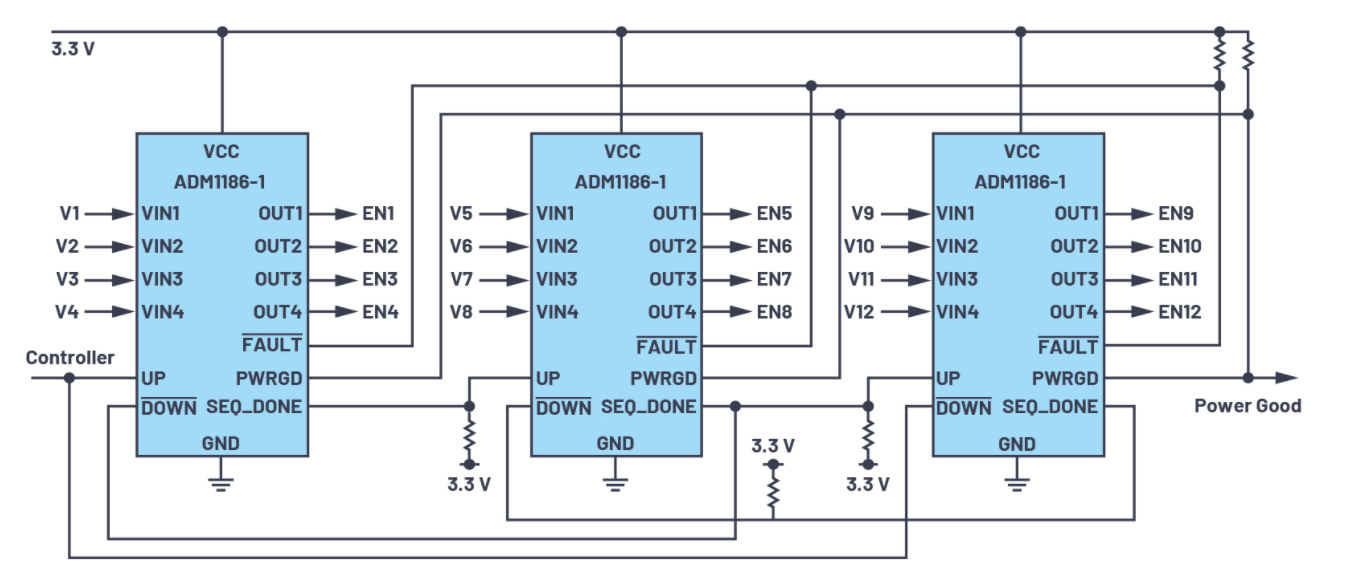

IC的可能性,但它們僅支持各個電壓的受控斜坡上升,而不支持這種菊花鏈星座中的受控關斷時序(即電壓關斷)。圖3.多個ADM1186-1器件鏈接在一起,可控制12個電壓的上電和關斷時序可靠且受控的上電

2021-04-12 07:00:00

Hi,你好,想請問下關于AD2S1210的上電初始化時序問題,

1、硬件復位引腳RESET引腳如果在VDD達到規定電壓之前沒有存在低電平的時間,會出現什么問題?

2、硬件復位引腳RESET引腳在

2023-12-06 06:55:32

現在的FPGA還嚴格要求上電時序嗎?想請教一下大家

2017-09-26 15:39:07

晚于3.3V,同理1.2V的產生要晚于1.8V,這樣就解決了上電先后問題。而圖(b),由于三個DCDC同時輸出,芯片本身及PCB設計均有延遲差異,就不能保證哪個電源先產生了,對于有電源輸入時序要求的芯片就可能引發問題了。

2016-05-30 15:19:13

工程師以為是軟件的問題,花費了很大的時間和精力來找BUG,問題仍然沒有很好的得到解決。后來查翻手冊發現,發現該系列的MCU對于上電時間是有一定要求的(其實幾乎所有品牌的MCU都有上下電時序要求)。圖1

2019-09-01 07:00:00

啟動和關斷這些電源軌。此過程稱為電源時序控制或電源定序,目前有許多解決方案可以有效實現定序。對于需要電壓定序的復雜器件,其內核和模擬模塊的電壓軌可能需要在數字 I/O 電壓軌之前上電。有些設計可能會要求...

2021-11-12 06:01:50

立即失效。當超過邊界條件的狀況多次發生且系統承受壓力時,長期可靠性會降低。此外,連續違反時序控制模式會損壞片內保護電路并產生長期損害,導致現場操作故障。不僅在上電和掉電期間,而且在常規工作期間優化偏置

2017-11-22 09:28:58

。無論如何,正確的上電和關斷時序控制可以防止閂鎖引發的即時損壞和ESD造成的長期損害。此外,電源時序控制可以錯開上電過程中的浪涌電流,這種技術對于采用限流電源供電的應用十分有用。 本文討論使用分立器件進行

2019-07-03 08:15:19

鉤:和上電時序有一定關系... 3. 上電回溝的問題,如果你認為你的上電時序設計的沒問題,那么還要考察一下芯片自己的問題,打個比方,芯片有3.3V和1.5V的輸入,1.5V先上電, 3.3V后上電,現象是 3.3V...

2021-12-31 06:59:38

的暫態失控問題,但執行電路先于控制系統建立工作條件或在要求更高可靠性時須采用互補邏輯或翻轉邏輯設計,互補邏輯設計指一系列由特定01交替邏輯的組合為有效值,否則就判為無效;翻轉邏輯則是通過時序上01邏輯

2011-12-08 10:54:52

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行

2019-07-18 08:10:11

最近做一款產品,用到AD2S1210此款芯片,問題是芯片沒有激勵波形輸出,這款芯片是上電就有激勵波形還是時序操作后才有激勵波形輸出,軟件已經按照示例上操作了 還是沒有波形EXC和EXC非 輸出一個接近3V一個接近5V都是直流,請問下有經驗的朋友們 問題可能出在什么地方

2018-09-18 10:00:33

你好,AD7982的VREF與VDD/VIO之間是否有時序要求?手冊里沒查到。在目前我們的設計中,VREF(5V)先于VDD(2.5V)和VIO(2.5V)上電,不知是否會有問題。謝謝。

2019-01-08 13:56:41

。2、測量±13V電源的上電時序,發現-13V上電略早于+13V幾十ms,調整-13V上電到略晚于+13V幾十ms后,運放初次上電后也輸出為0V左右。綜合以上現象,初步判斷ADA4522-2對電源的上電時序比較敏感,請問這個現象是正常的嗎?之前同樣電路用過幾種其他的運放,都沒有出現過這樣的問題。

2018-08-14 07:20:54

我想用adp5050給zynq供電,而zynq各電源有上電時序要求,請問這個應該怎么處理?

2019-03-01 13:37:09

本帖最后由 一只耳朵怪 于 2018-6-21 15:44 編輯

技術支持你好,AM335x開機時候有上電順序要求,但是在關閉芯片有時序要求嗎?我看到手冊中提及:power-down

2018-06-21 06:23:53

本帖最后由 一只耳朵怪 于 2018-6-21 11:05 編輯

你好:AM5718上電時序不對,會燒AM57188嗎?

2018-06-21 06:39:46

F28377D需要3.3V和1.2V, controlsuite里用 TPS64240為芯片供電,請問這兩個電壓有沒有上電先后時序?

2018-11-23 09:42:13

有哪位大神能幫我看看著上電時序怎么看啊,都看不懂

2018-09-04 22:07:05

我用ucc27324這片驅動芯片給驅動,分別給低邊的MOS和高邊的MOS驅動。高邊的MOS和驅動芯片之間已加隔離變壓器和隔直電容,但是占空比很小,所以關斷時候負壓很小,總是會被誤觸發。低邊的MOS關斷時候是零電壓,也不可靠。有沒有什么辦法在改動很少的情況下加上可靠的負壓關斷(至少-2V)?

2019-06-27 09:12:37

為什么電源紋波不能直接一鍵捕獲呢?為什么多路上電時序前后分析對比這么麻煩呢?為什么分析調制信號時波形對比度這么差呢?事實上,用戶的每一次體驗感,都是產品隱形的提升空間。以上這三個麻煩,現在也許有了

2018-12-03 11:17:59

些設計可能需要采用其他序列。無論如何,正確的上電和關斷時序控制可以防止閂鎖引發的即時損壞和 ESD 造成的長期損害。此外,電源時序控制可以錯開上電過程中的浪涌電流,這種技術對于采用限流電源供電的應用十分

2018-10-23 14:30:34

的行為表現(參見表2),分析可能的問題及原因,并提出一些建議。上電時序問題多種多樣上電時序問題可能出現于多種不同情況。例如,在一個客戶應用中,AD8616配置為緩沖器,在電源建立之前輸入為0 V(圖1

2019-06-18 08:30:00

的行為表現(參見表2),分析可能的問題及原因,并提出一些建議。上電時序問題多種多樣上電時序問題可能出現于多種不同情況。例如,在一個客戶應用中,AD8616配置為緩沖器,在電源建立之前輸入為0 V(圖1

2019-10-10 08:30:00

和SDR為低電平有效,當其處于低電平時電路處于關斷狀態,所以一上電就使電路處于關斷狀態就不會產生POP聲。原來的電路一上電關斷腳是高電平,關斷功能失效,所以在該腳對GND接一個22uF左右大電容后,關斷

2018-11-10 21:16:51

時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 可關斷晶閘管(GTO),可關斷晶閘管(GTO)是什么意思

可關斷晶閘管

turn-off thyristor

2010-03-03 11:54:13 10619

10619 ADM108x簡單時序控制器可在上電期間對兩個電壓軌進行簡單的時序控制,時間延遲可通過電容進行編程。利用該系列的兩個器件可構成一個簡單的電路,從而以各自可編程的時間延遲對兩

2011-09-01 15:57:19 34

34 基于時序模擬的并網型微網可靠性分析_王玉梅

2017-01-08 10:30:29 0

0 針對航空航天產品高可靠性、長壽命的特點,通過綜合時序模型對隨機序列自擬合性強與短期預測精度高的優點,提出了兩類基于性能退化數據的產品可靠性評估時序模型方法。 首先,從性能退化量分布的角度出發,在假設

2019-03-08 15:58:13 16

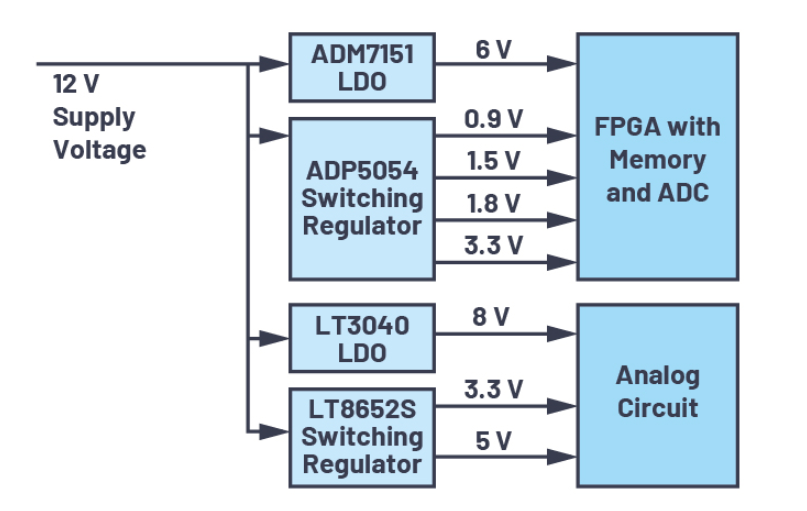

16 現今,電子系統往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統中,尤其如此。為實現可靠、可重復的操作,必須監控各電源電壓的開關時序、上升和下降速率、加電順序以及

2019-04-09 08:14:00 3557

3557

微處理器、FPGA、DSP、模數轉換器 (ADC) 和片上系統 (SoC) 器件一般需要多個電壓軌才能運行。為防止出現鎖定、總線爭用問題和高涌流,設計人員需要按特定順序啟動和關斷這些電源軌。此過程稱為電源時序控制或電源定序,目前有許多解決方案可以有效實現定序。

2019-09-15 09:22:00 647

647

AN-1080: 利用簡單時序控制器ADM108x進行上電和關斷時序控制

2021-03-21 00:41:43 6

6 原標題:控制電源啟動及關斷時序微處理器、FPGA、DSP、模數轉換器 (ADC) 和片上系統 (SoC) 器件一般需要多個電壓軌才能運行。為防止出現鎖定、總線爭用問題和高涌流,設計人員需要按特定順序

2021-11-07 18:37:03 10

10 ??本文主要介紹了時序設計和時序約束。

2023-07-04 14:43:52 691

691 時序:字面意思,時序就是時間順序,實際上在通信中時序就是通信線上按照時間順序發生的電平變化,以及這些變化對通信的意義就叫時序。

2023-07-26 10:06:03 1641

1641 器是一種電子設備,它的作用是控制多個電源單元間的開啟和關閉時序,從而保證系統的穩定性和可靠性。電源時序器通常由微控制器或者FPGA實現,可以根據用戶需要編寫相應的程序控制電源單元的開啟和關閉時序。電源時序器通常被

2023-10-16 16:16:27 1857

1857 igbt怎樣導通和關斷?igbt的導通和關斷條件 IGBT(Insulated Gate Bipolar Transistor)是一種晶體管,可以用作開關。IGBT由P型注入區、N型襯底

2023-10-19 17:08:02 8163

8163

電子發燒友App

電子發燒友App

評論