SATA3.0 Host Controller IP

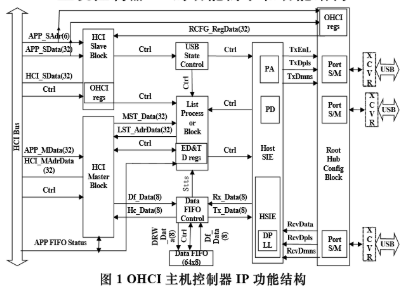

SATA3.0 Host IP不僅實(shí)現(xiàn)了SATA協(xié)議的PHY(物理層)、Link(鏈路層)和TRN(傳輸層),并且實(shí)現(xiàn)了CMD(命令層)和APP(應(yīng)用層),支持1.5、3和6Gbps傳輸速率,和SATA規(guī)范完全兼容。

SATA3.0 Host IP給用戶使用SATA存儲(chǔ)設(shè)備提供一種高效且易于使用的接口。無需用戶干預(yù),SATA3.0 Host IP自動(dòng)完成連接、診斷、識(shí)別以及初始化SATA存儲(chǔ)設(shè)備,輸出SATA設(shè)備的Identify Data Structure。SATA3.0 Host IP內(nèi)置DMA控制器,用戶不但可以通過IO接口訪問SATA存儲(chǔ)設(shè)備,還可以使用DMA接口高效讀寫SATA存儲(chǔ)設(shè)備。

SATA3.0 Host IP不局限連接SATA存儲(chǔ)設(shè)備的個(gè)數(shù),即連接SATA存儲(chǔ)設(shè)備的數(shù)量是可編程的。

內(nèi)核特性:

1.????? 與SATA 1.5Gbps、3.0Gbps以及6.0Gbps業(yè)界規(guī)范完全兼容

2.????? AXI-Lite或應(yīng)用寄存器(ARI)接口,同時(shí)支持IO(包括PIO和Trim)和DMA操作

3.????? IO數(shù)據(jù)接口采用RAM設(shè)計(jì),DMA數(shù)據(jù)接口采用AXI-Stream或FIFO設(shè)計(jì)

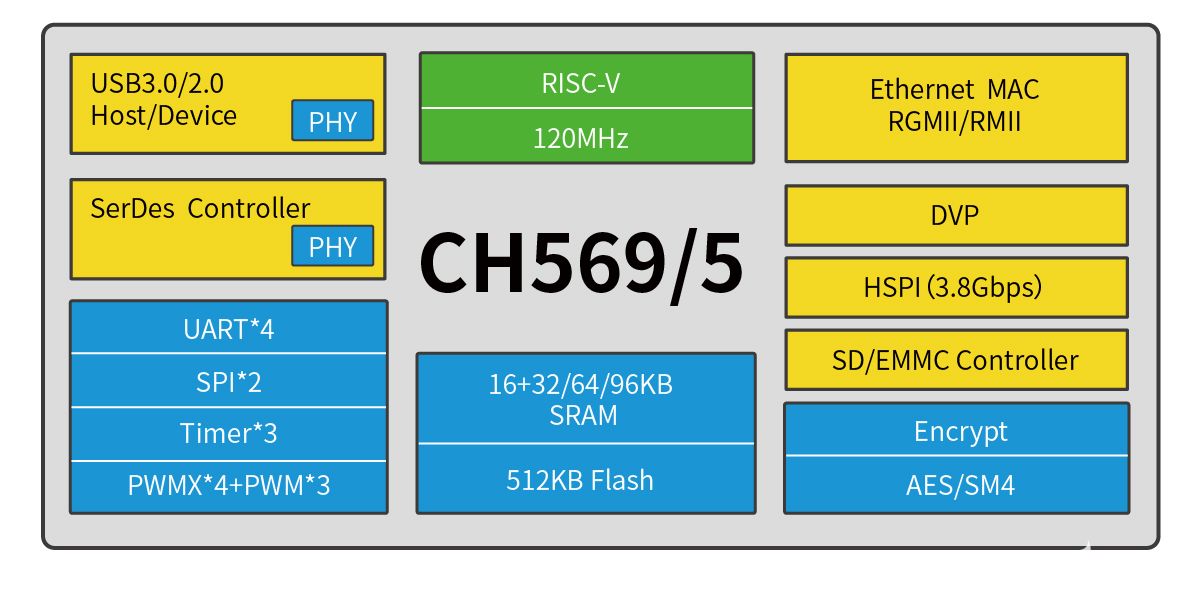

4.????? 支持SerDes接口,并且SerDes接口個(gè)數(shù)可編程(即可連接的SATA存儲(chǔ)設(shè)備的數(shù)量是可編程的,數(shù)量取決于FPGA的GT個(gè)數(shù))

5.????? 支持SATA存儲(chǔ)設(shè)備帶電熱插拔

6.????? 支持Xilinx器件:Spartan-6,Virtex-5,Virtex-6,Artix-7,Kintex-7,Virtex-7,Kintex Ultrascale,Kintex Ultrascale+,Virtex Ultrascale,Virtex Ultrascale+

7.????? 易于集成的同步、可綜合Verilog設(shè)計(jì)

8.????? 通過完全驗(yàn)證的SATA3.0 IP

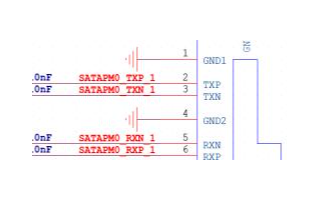

對(duì)外接口:

1.????? AXI-Lite或應(yīng)用寄存器(ARI)接口

2.????? AXI-Stream或FIFO流式數(shù)據(jù)總線

3.????? RAM塊式數(shù)據(jù)總線? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

?

?

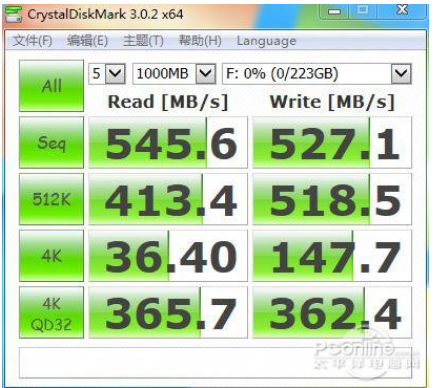

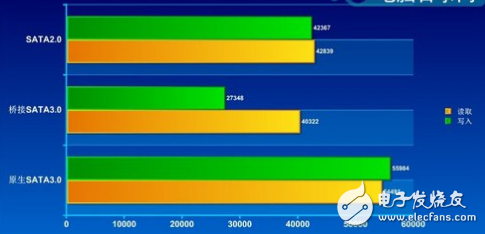

性能指標(biāo):

1.????? SATA 3.0 Core:連續(xù)寫入速度大于530MB/s,連續(xù)讀取速度大于550MB/s

2.????? SATA 2.0 Core:連續(xù)寫入速度大于240MB/s,連續(xù)讀取速度大于250MB/s s

1通道(連接1個(gè)SATA存儲(chǔ)設(shè)備)SATA3.0 IP資源使用(XC7K325為例):

1.????? LUTs:3850,F(xiàn)Fs:4630,BRAM:16,GT:1

4通道(連接4個(gè)SATA存儲(chǔ)設(shè)備)SATA3.0 IP資源使用(XC7K325為例):

1.????? LUTs:15363,F(xiàn)Fs:18468,BRAM:64,GT:4

8通道(連接8個(gè)SATA存儲(chǔ)設(shè)備)SATA3.0 IP資源使用(XC7K325為例):

1.????? LUTs:30763,F(xiàn)Fs:37011,BRAM:128,GT:8

可交付資料:

1.????? 詳細(xì)的用戶手冊(cè)

2.????? Design File:Post-synthesis EDIF netlist or RTL Source

3.????? Timing and layout constraints,Test or Design Example Project

4.????? 技術(shù)支持:郵件,電話,現(xiàn)場(chǎng),培訓(xùn)服務(wù)

責(zé)任編輯:tzh

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論