STM8S003F3能否輸出2路可調的相位相差180度的獨立PWM波形?

兩路pwm波形有死區時間可控制

2024-03-22 06:34:43

,現貨庫存CYV15G0203TB-BGXCCYV15G0101DXB-BBXCCYV15G0204TRB-BGXCCYV15G0401DXB-BGXCCYV15G0104TRB-BGXC如需其他型號,歡迎點擊右側客服咨詢!!!

2024-02-26 10:08:43

(如i2c1)。因為例程中的時鐘初始化,只有機器定時器1是分到group1和core1的,所以不太確定。

3-只有共享內存(linker文件中已配好16k)是雙核都能訪問的,且該ram區只能

2024-02-06 21:14:30

使用兩片LTM4630可以實現三路并聯(電壓為1.0),另一路獨立輸出嗎(電壓為1.2V).

2024-01-04 07:00:37

FIFO方案,則無法正常工作。

該問題的一種解決方案是讓雙通道轉換器使用多點鏈路JESD204B接口,其中每個轉換器都使用各自獨立的串行鏈路輸出。然后便可針對每個ADC使用非相干時鐘,且每個串行鏈路

2024-01-03 06:35:04

電子發燒友網站提供《具有串行I2C接口的實時時鐘1339 數據表.pdf》資料免費下載

2023-12-21 10:45:31 0

0 請問,AD9788芯片,能否兩路DA輸出完全獨立的兩路信號分別去混頻,而不是分IQ輸出進解調器?謝謝

2023-12-18 06:49:29

您好:

使用AD9690時,想知道數據具體是怎樣映射到串行鏈路上的。

我打算不使用AD9690內置的DDC,直接將采樣后的一路數據通過串行鏈路傳遞到FPGA;在手冊中看到一幅圖描述著,一個采樣點的高

2023-12-12 08:22:45

請問,要搭一個傳輸鏈路,鏈路中的ADC和DAC的參數,比如:采樣率和分辨率一定要一樣嗎?

中頻模擬信號,先模數轉換數字化進行傳輸,之后需要數模轉換,前后的ADC和DAC采樣率和位數是否要完全相等?完全符合指標的器件不太好找。

2023-12-12 06:21:04

稱48位或48bit LVDS接口。

單路和雙路:單路就是只有一路 R、G、B 三色和HS、VS、DE控制信號; 雙路就是有兩路 R、G、B 三色和HS、VS、DE控制信號。

經常碰到什么單6,雙6

2023-12-11 13:21:58

假設我有4個AD5422采用菊花鏈方式連接,當前狀態輸出電流都為10mA,現在想改變第3個的電流輸出為5mA,不改變其他路的輸出電流值。

問題1:那前24個時鐘(即操作第4個AD5422的時鐘

2023-12-11 07:56:50

描述 MAX9275/MAX9279是3.12Gbps千兆位多媒體串行鏈路(GMSL)串行器,具有并行LVCMOS輸入和CML串行輸出,可編程用于50ω同軸電纜或100ω屏蔽雙絞線(STP

2023-12-07 10:30:47

使用內部PLL,輸入參考頻率為100MHz。在采樣率時鐘設置為1GHz時,DAC的JESD204B鏈路能建立,但是當頻率改為1.5GHz時,SYNC一直為低。其他相關寄存器都已經修改,serdes

2023-12-05 08:17:30

我理解這個D觸發正常運轉要滿足四個約束,第一個是建立時間,第二個是保持時間,第三個是對于最后一個傳輸門的關斷時間的控制,第四個是[時鐘周期]() 約束。

2023-12-04 15:44:02 352

352

各音頻的時鐘不相同,因此用4個ASRC去進行同步,而SPDIF、ADC與I2S0共用一路ASRC。用PCG產生輸出給,AD/DA的主時鐘,SPORT 0-1,6-7的FS,CLK。基本上設計是這樣

2023-11-30 06:09:13

關于AD8221

1)熱偶方式為何要用單端偏置?可否也用雙端平衡偏置電阻

2)8221的差分輸入信號是否必須與8221共地?還是共不共都行?

歡迎討論

2023-11-27 07:45:59

的答案:

(1)總的建立時間就等于兩級運放的建立時間之和,即90 ns + 90 ns =180 ns

(2)總的建立時間還是90 ns

(3)認為兩級運放相互獨立,總的建立時間等于兩級運放建立時

2023-11-27 06:54:56

華創翼聯HC-G30是一款使用 Wi-Fi 6 協議的便攜式路由器。采用 MT7981B 主頻1.3GHz 雙核處理器,支持160MHz, 無線速率和信號強度都有卓越的提升。它可以滿足家庭多設備連接

2023-11-23 15:38:45

。

時鐘輸出蜂鳴器輸出控制電路的框圖如圖13-1所示。

最大輸出頻率

功能引腳

可以輸出兩路方波CLKBUZ0與CLKBUZ1

CLKBUZ0可選為P31、 P140。

CLKBUZ1可選為P15

2023-10-25 11:20:01

C語言或Matlab如何實現FF鏈路調度器仿真

2023-10-18 06:12:23

僅當存在待發送數據時串行時鐘波特發生器才產生對應數據位模式的時鐘脈沖嗎?如果緩沖區沒數據,串行時鐘就一直空閑嗎?

2023-10-17 08:20:06

C語言或matlab如何實現ff鏈路調速器仿真

2023-10-17 07:34:56

STM32的獨立看門狗用的時鐘是內部時鐘還是外部時鐘呢

2023-10-15 11:58:05

1. 產品簡介

USR-G808 是一款雙 4G 無線工業路由器,提供了一種用戶通過 WIFI 或是網口接入4G 網絡的解決方案。產品采用商業級高性能嵌入式 CPU,工作頻率高達 580MHz

2023-09-25 07:18:54

很多應用場合需要檢測系統時鐘是否在正常范圍內,以保證MCU能正常工作,CLASS B功能安全實現系統時鐘自檢的方法是采用兩個獨立時鐘源交叉檢查來進行測量

2023-09-14 17:30:49 945

945

耗電與頻率成正比最低為1.5μA。如果有32.768kHz的振蕩器連接到LSE精度可達0.5% 復位和從停止/待機模式退出后MSI將作為默認的系統時鐘其建立時間的最大值為2us。 低速內部振蕩器

2023-09-12 08:25:02

功能

?60 GHz V波段收發器,可實現高達

480 Mbit/s

?集成全射頻收發器和天線的緊湊型解決方案,在半雙工模式下運行

?44 dB典型的總鏈路預算,高達6 cm的自由空間傳播損耗

2023-09-07 06:49:02

信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們表征了時鐘邊沿觸發前后數據需要在鎖存器的輸入持續時間,是接收器本身的特性。簡而言之,時鐘邊沿觸發前,要求數據必須存在一段時間,這就是器件需要的建立時間;

2023-09-04 15:16:19 391

391

應用:此示例代碼使用 M030G I2C 讀取 NCT7712Y 熱感應器。

BSP 版本: M030G_Series_BSP_CMSIS_V3.02.000

硬件:NuMaker-M030GTD

2023-08-29 08:05:00

打印機的工作原理是打印頭上安裝有半導體加熱組件,熱打印機有選擇地在熱敏紙的確定位置上加熱,由此就產生了相應的圖形。加熱是由與熱敏材料相接觸的打印頭上的一個小電子加熱器提供的。加熱器排成方點或條的形式由

2023-08-25 08:02:25

產品介紹PXIe7301雙路萬兆網卡具有局域網性能加速、網絡安全、網絡融合、網絡虛擬化、數據中心橋接等多項功能,通訊帶寬為雙口10Gbps,芯片的邏輯門數量達到一千八百萬,片上SRAM容量達到

2023-08-22 11:53:18

那個有M0518系統時鐘寄存器版本的初始化程序,庫函數的太大了,

系統時鐘實現的功能是使用外部晶振而不是內部

2023-08-22 07:00:34

安路CPLD可否提供內部時鐘

2023-08-11 09:14:56

使用,可通過經濟高效的 50Ω 單端同軸電纜或 100Ω 差分屏蔽雙絞線 (STP) 電纜提供單通道或雙通道高速串行流。它對 OpenLDI 輸入進行串行化處理,支持

2023-08-08 14:22:50

74HCT165是符合JEDEC標準7A的高速Si柵極CMOS器件。它們與低功率肖特基TTL(LSTL)引腳兼容。

74HCT165是8位并行加載或串行移位寄存器,具有可從最后一級獲得的互補串行輸出

2023-08-04 17:39:53

MAX9209/MAX9213將21位的LVTTL/LVCMOS并行輸入數據串行化為三路LVDS輸出。第四路LVDS輸出為并行速率時鐘,為解串器提供時鐘。MAX9209/MAX9213具有可編程直流

2023-07-11 10:25:35

。MAX9217與MAX9218解串器組成一個完整的數字視頻串行鏈路。可通過阻抗受控的PCB走線或雙絞線實現互連。專用數據編碼降低EMI并提供DC平衡。DC平衡允許使用

2023-07-11 10:14:49

。MAX9247與MAX9248/MAX9250解串器配合使用,組成一個完整的數字視頻串行鏈路。可通過阻抗受控的PCB走線或雙絞線實現互連。專用數據編碼降低EMI并提供

2023-07-11 10:08:09

MAX9257A串行器與MAX9258A解串器配對形成完整的數字視頻串行鏈路。MAX9257A/MAX9258A具有可編程并行數據寬度、并行時鐘頻率范圍、擴頻和預加重功能。在上電時,集成控制通道會在

2023-07-11 09:24:33

MAX9257A串行器與MAX9258A解串器配對形成完整的數字視頻串行鏈路。MAX9257A/MAX9258A具有可編程并行數據寬度、并行時鐘頻率范圍、擴頻和預加重功能。在上電時,集成

2023-07-11 09:22:05

–60V,–1.5APちャネルさーマルFET電力スイッチング(R07DS1070JJ0401)

2023-07-05 19:11:48 0

0 H7N0401LD H7N0401LS H7N0401LM 數據表

2023-06-27 18:53:48 0

0 ??本文主要介紹了建立時間和保持時間。

2023-06-21 14:38:26 1079

1079

建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序分析的基礎。

2023-06-21 10:44:01 881

881

運算放大器建立時間是保證數據采集系統性能的關鍵參數。為了實現精確的數據采集,運算放大器輸出必須在A/D轉換器能夠準確數字化數據之前建立。然而,建立時間通常不是一個容易測量的參數。

2023-06-17 10:37:54 366

366

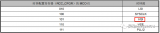

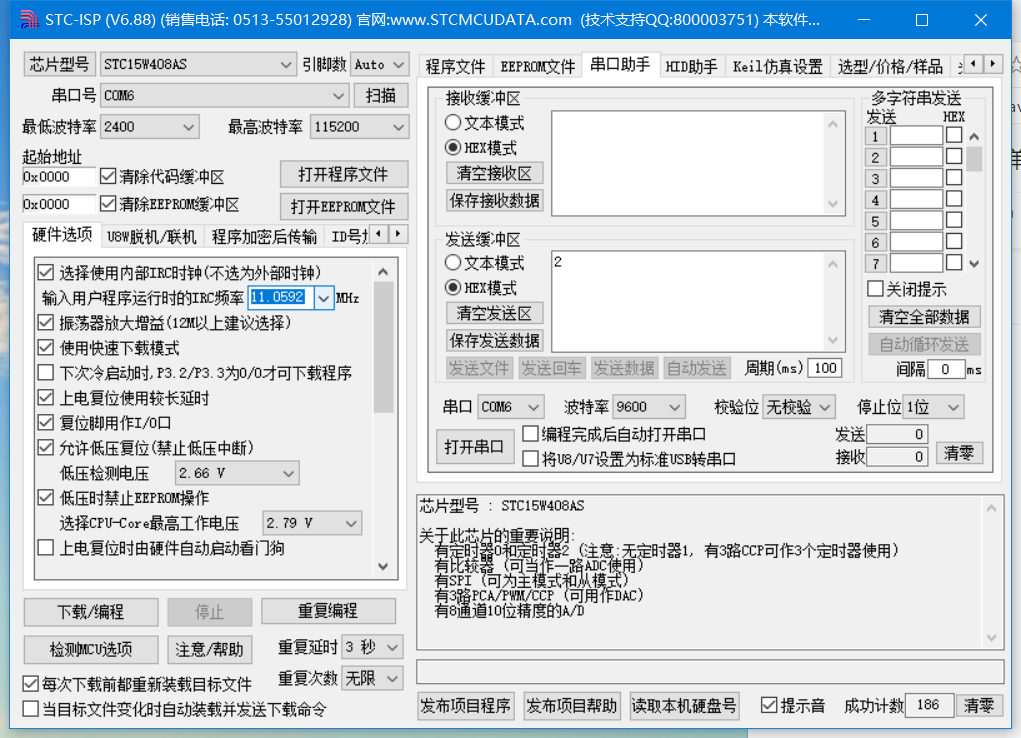

STC15W408AS單片機有兩個時鐘源:內部高精度R/C時鐘和外部時鐘(外部輸入時鐘或外部晶體振蕩器產生的時鐘)。內部高精度R/C時鐘(±0.3%),±1%溫漂,常溫下溫漂±0.6%(-20℃~+65℃)。

2023-06-15 14:45:08 1211

1211

振蕩器

--時鐘監測系統

--允許獨立關斷各外設時鐘

?支持最多 39 路 I/O 接口

--所有 I/O 口支持中斷功能

--所有 I/O 支持中斷輸入濾波功能

?五通道 DMA 控制器

2023-06-07 11:04:28

flexcan在QSPI啟動模式下無法初始化OK ,但在串行啟動模式下可以初始化OK;

在qspi啟動模式和串行啟動模式下比較flexcan init之后的所有flexcan寄存器,只有兩個寄存器的位不同。

2023-06-06 07:18:53

首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

。

我們希望所有這些實例都可以獨立運行,因此它們都配置了時鐘模塊。而且它們獨立運行時沒有問題。但是當我們使用Bootloader來加載和運行所有這些實例時,有些功能就無法工作,甚至會出現系統復位的情況。

以上案例如何配置時鐘模塊,所有實例一起工作時都需要配置時鐘且不沖突。

2023-05-30 08:12:04

大家好,

請幫助我了解 S32G2 是否支持雙內存進行 OTA 更新。基本上在這里我們期待雙分區。

2023-05-29 08:51:39

基站的內部,都有自己獨立的時鐘模塊:晶振(晶體振蕩器),在沒有外部時鐘源時,就處于自由震蕩狀態。

可想而知,在自由震蕩狀態的各個基站間的時鐘沒有同步,每個基站都只是一個孤島,只能獨立運行無法協同

2023-05-10 17:09:50

和8K@30fps H265/H264視頻編碼。

核心板

核心板+底板結構,拆卸方便,核心板引腳320PIN全部引出滿足擴展需求助力產品開發。

接口豐富

雙路千兆以太網、5G/4G模塊、HDMI輸入、HDMI輸出

2023-05-09 10:31:24

H7N0401LD H7N0401LS H7N0401LM 數據表

2023-05-08 19:12:56 0

0 變得不合適時

定時器超期后的行為: 返回RRC_IDLE模式

RRC reestablish建立過程如圖所示:

3 RLF 無線鏈路恢復

Timer:T311

起始點: 初始化

2023-05-08 15:10:10

采用modbus的串口鏈路,這3個設備公用一條鏈路,該如何設設置?有一個主控屏,一臺pc上位機,和一個受控設備.PC遠控端,屏近地控制

2023-05-05 16:17:00

1.前言

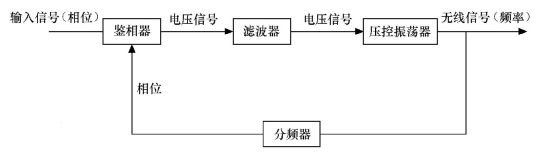

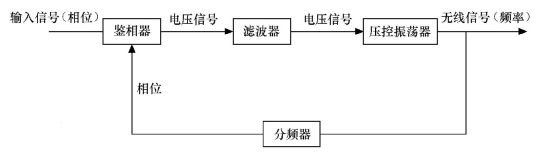

同步是通信系統最關鍵的功能之一。然而,在5G的環境中,特別是對于上行鏈路和下行鏈路傳輸在同一頻率上的時分雙工(TDD),干擾的可能性要大得多。因此,我們看到了TDD-LTE

2023-05-05 10:36:02

備件轉生產的物資信息轉換、工程文檔整理等文檔類工作耗時耗力,工程余料盤點難。

數字化助力工程物資供應鏈管理價值提升為了最大限度發揮物資供應鏈管理的實效,釋放供應鏈管理價值,可借力數字化技術,強化

2023-04-25 11:28:10

78K0/Kx2 用戶手冊: 硬件 (R01UH0008EJ0401_78K0Kx2)

2023-04-18 19:35:04 0

0 KL05,30 個 K10。我們檢查了 K10 和 K20 uc 它不起作用。我通過 SWD 連接器 J6 對 FRDM-KL46Z 板進行編程來檢查 PE 多鏈路,它對板進行編程沒有任何問題。我

2023-04-04 06:52:58

44769-0401

2023-04-03 15:36:22

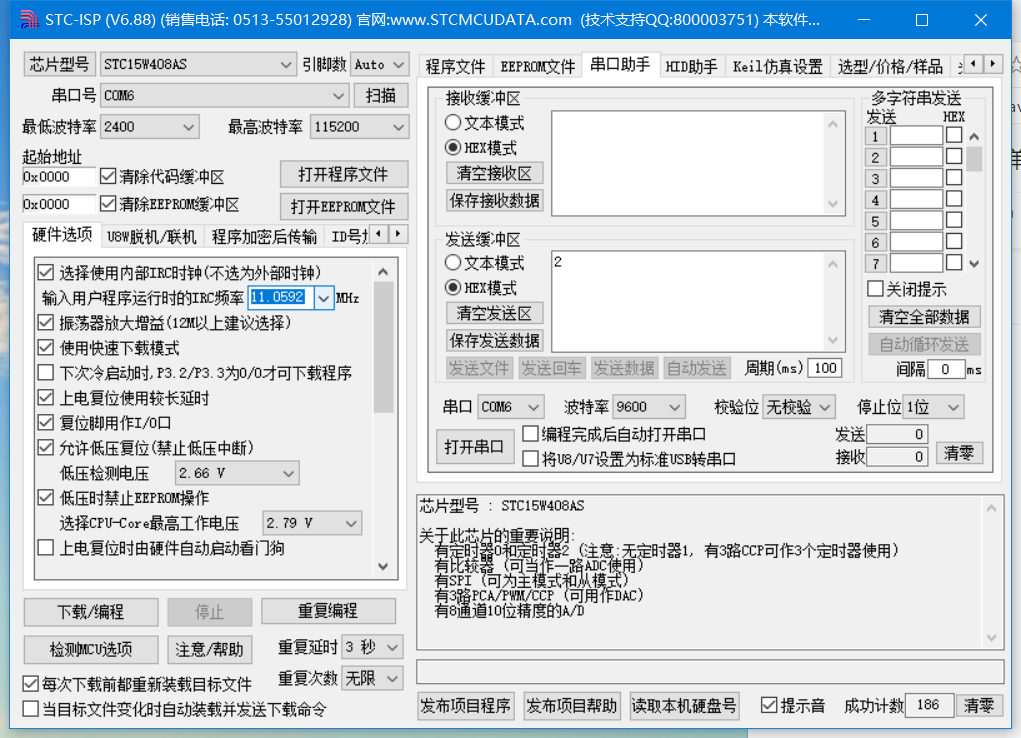

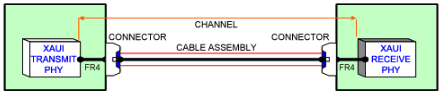

高速串行鏈路的表征取決于SI工程師發現、理解和解決嚴重抖動問題的能力。在本討論中,我們假設 PHY(物理層)或 SerDes(串行器-解串器)設備的時鐘和數據恢復 (CDR) 模塊符合適用于該設備

2023-04-03 11:27:21 995

995

[0x0000004EB: cpsid i]。請告訴我是否需要在啟動時初始化 PC、MSP 和更多寄存器,以及如果需要該怎么做。此外,為什么當我使用 PE 多鏈路通用探針進行調試時,它沒有初始化就可以工作?

2023-03-31 06:17:11

TPL0401 - Digital Potentiometer Evaluation Board

2023-03-29 22:54:15

502352-0401

2023-03-29 22:00:15

505565-0401

2023-03-29 21:56:35

GC0401K

2023-03-29 21:55:33

560123-0401

2023-03-29 21:52:48

43650-0401

2023-03-29 21:45:23

DA-15S-II

2023-03-29 17:52:56

74540-0401

2023-03-29 17:52:29

505151-0401

2023-03-28 14:47:18

172953-0401

2023-03-28 14:46:22

172952-0401

2023-03-28 14:45:34

幾乎稍微復雜的數字設計都離不開時鐘。時鐘也是所有時序邏輯建立的基礎。前面介紹建立時間和保持時間時也涉及過時鐘偏移的概念。下面將總結下時鐘的相關知識,以便更好的進行數字設計。

2023-03-28 13:56:41 978

978

ETHERNET TRANSCEIVER, PBGA256

2023-03-27 14:13:21

QUAD HOTLINK II RECEIVER

2023-03-27 14:12:56

和2024年,隨著AI大數據領域、以及超級計算機或者超級計算單元等應用的迅猛發展,大電流和高功率密度模塊、以及高能量密度的Power Block模塊也將會迎來爆發式的需求增長。MPS最新推出的雙路輸出系列

2023-03-24 15:42:26

64 x 8,串行,I2C實時時鐘

2023-03-24 14:48:57

64 x 8,串行,I2C實時時鐘

2023-03-24 14:01:39

根據參考手冊,NXP S32K144HAMLL 具有 3 個低功耗串行外設接口,使用 SIRC 時鐘源運行。 我想知道 3 LPSPI 是否與時鐘源一起獨立運行。我找不到顯示時鐘源如何連接到所有三個 SPI 的完整總線圖。如果有人能澄清這一點,那將非常有幫助。

2023-03-24 06:27:34

I2C 串行實時時鐘

2023-03-23 05:01:01

1 Kbit 串行 SPI 總線 EEPROM,帶高速時鐘

2023-03-23 04:56:22

電子發燒友App

電子發燒友App

評論