數(shù)據(jù)采集中毛刺的處理方法

2012年11月13日 15:56 來源:本站整理 作者:灰色天空 我要評論(0)

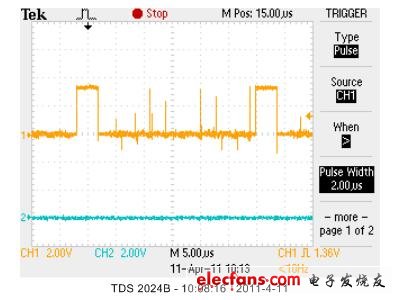

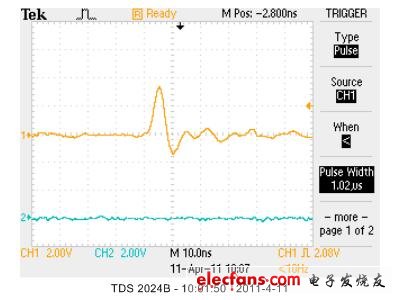

在采集一組并行接口信號時,發(fā)現(xiàn)接收到的數(shù)據(jù)非常不穩(wěn)定。用示波器測量幾個用于同步的控制信號,發(fā)現(xiàn)時不時的有毛刺產(chǎn)生。因?yàn)檫@些數(shù)據(jù)最終都是要顯示在液晶屏上的,當(dāng)示波器同時測量兩個同步信號時,液晶屏的顯示錯位現(xiàn)象得到明顯好轉(zhuǎn)。示波器探頭測量信號時相當(dāng)于并聯(lián)上一個pF級的電容,也能夠一定程度上起到濾波的效果,因此可以斷定同步信號的毛刺影響了數(shù)據(jù)的采集。其中一個同步信號如圖1,兩個有效高脈沖之間有很多毛刺,放大毛刺后如圖2所示,大約維持10ns的高電平。

圖1

圖2

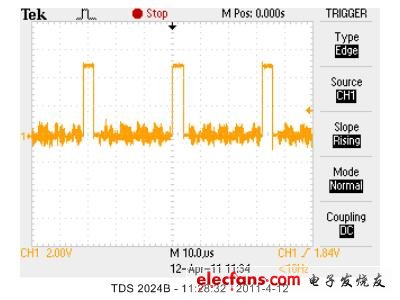

如何濾除這些毛刺呢?辦法有兩個,其一就是用純粹硬件的辦法,在信號進(jìn)入FPGA之前進(jìn)行濾波處理,串個電阻并個電容都可以,特權(quán)同學(xué)并了一個20pF電容后就能夠把這些毛刺徹底濾干凈,如圖3所示。

圖3

而還有一種“軟”硬件濾波的方法。就如特權(quán)同學(xué)收錄進(jìn)<深入淺出玩轉(zhuǎn)FPGA>一書中的博文<基于FPGA的跨時鐘域信號處理——亞穩(wěn)態(tài)>所談到的,降低數(shù)據(jù)采集頻率以及多次采集后邏輯處理都是一種思路。那這里特權(quán)同學(xué)給出一種多次采集處理的濾波方法和大家分享。

input ain; //輸入信號

reg[3:0] ainr; //輸入信號緩存

//輸入信號打4拍

always @(posedge clk or negedge rst_n)

if(!rst_n) ainr <= 4‘d0;

else ainr <= {ainr[2:0],ain};

//輸入信號上升沿檢測,高電平有效

wire pos_ain = ~ainr[3] & ~ainr[2] & ainr[1] & ainr[0];

//通常只要兩個信號就行,即wire pos_ain = ~ainr[2] & ainr[1] ;。

//這里用了4個信號就是多次采樣濾波的效果

//輸入信號下降沿檢測,高電平有效

wire neg_ain = ainr[3] & ainr[2] & ~ainr[1] & ~ainr[0];

//通常只要兩個信號就行,即wire neg_ain = ainr[2] & ~ainr[1] ;。

//這里用了4個信號就是多次采樣濾波的效果

//若該輸入信號主要關(guān)注其高脈沖,那么可以做以下濾波

wire high_ain = ainr[1] & ainr[0];

//兩個信號相與通常可以濾除1個clk的毛刺,相應(yīng)的,3個信號相與可以濾除2個clk的毛刺

//若該輸入信號主要關(guān)注其低脈沖,那么可以做以下濾波

wire low_ain = ainr[1] | ainr[0];

上周熱點(diǎn)文章排行榜

上周資料下載排行榜

論壇熱帖

熱門博文

創(chuàng)新實(shí)用技術(shù)專題

大家談:華為能否撬開美國市場?

數(shù)據(jù)采集技術(shù)應(yīng)用

數(shù)據(jù)采集資料下載

- 智能環(huán)境數(shù)據(jù)采集小車

- 基于Android 平臺的智能手持終端Camera模組驅(qū)動設(shè)計

- 基于單片機(jī)的多路數(shù)據(jù)采集系統(tǒng)設(shè)計畢業(yè)論文

- 基于Web的高校項目評審系統(tǒng)的設(shè)計

- 一種多通道數(shù)據(jù)采集系統(tǒng)設(shè)計研究

- 基于USB2.0與LabVIEW的高速數(shù)據(jù)采集系統(tǒng)設(shè)計

- 摩擦試驗(yàn)機(jī)數(shù)據(jù)采集與處理系統(tǒng)設(shè)計

- MAX1204數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)資料

- 基于FPGA和UART的MCU總線數(shù)據(jù)采集系統(tǒng)設(shè)計

- Labview在單片機(jī)數(shù)據(jù)采集系統(tǒng)的應(yīng)用

熱評

- LM3S9B96開發(fā)板手冊及原理圖

- NI推出Single-Board RIO嵌入式介面

- STM32F103ZET6紅牛電路圖

- 高通發(fā)布全新設(shè)計DragonBoard板

- 3.15投訴:揭開天翼3G手機(jī)的“欺騙”

- 小米手機(jī)2工程機(jī)月底將上市

- 新款 Apple TV 將在3月8日出貨

- protel99se正式漢化版免費(fèi)下載

- matlab 7.0軟件下載(免費(fèi)破解版)

- hi3515海思原版原理圖

博文

- 新學(xué)習(xí)單片機(jī),決心轉(zhuǎn)型技術(shù)宅

- 白巖松:青春該怎么過?不計后果的過

- 破解大學(xué)寢室的智能限電

- 關(guān)于學(xué)電子的女生那點(diǎn)事

- 當(dāng)你累了,準(zhǔn)備放棄時,看看這個吧!!!

- 十個學(xué)嵌入式的禁忌

- 電子信息專業(yè)到底該做些什么

- 大學(xué)那點(diǎn)事兒第二波:文科女生PK理科女生

- 菜鳥STM32初次制版

- iPhone5數(shù)據(jù)線芯片IC

帖子

- 做了幾個光立方,做作了幾塊板子,誰要的pm我一下,送大家了 wishriver1

- 成功的作品卻追不到我心愛的她 hao10086

- 手工打造功能超強(qiáng)的MP3 hukaipanwenjing

- 關(guān)于學(xué)電子的女生那點(diǎn)事 cherr番茄

- 三年積累的硬件資料-硬件基礎(chǔ)+原理設(shè)計+pcb設(shè)計+測試,全! joujoulian

- 自己家的密碼門鎖 屌絲

- 好看的32*64雙色點(diǎn)陣屏 yuhonglong

- 電子發(fā)燒友電子雜志上線啦,誠征雜志稿件 xiaoliu241

- 不能不知道的常用電路設(shè)計 風(fēng)之谷MF

- 最強(qiáng)單片機(jī)點(diǎn)陣實(shí)例和學(xué)習(xí)攻略 zhihuizhou

用戶評論

查看全部 條評論

查看全部 條評論>>