隨著數(shù)字系統(tǒng)性能的提高,設(shè)計(jì)人員需要越來(lái)越細(xì)心地關(guān)注時(shí)鐘發(fā)生和分配電路的設(shè)計(jì),以避免時(shí)鐘分配時(shí)序出現(xiàn)差異或不確定性。此類問(wèn)題會(huì)降低系統(tǒng)性能,減少時(shí)序余裕,或?qū)е鹿δ苠e(cuò)誤。為了避免時(shí)序偏移相關(guān)的問(wèn)題,設(shè)計(jì)人員可以使用零延遲時(shí)鐘緩沖器。

典型同步數(shù)字系統(tǒng)使用公共時(shí)鐘來(lái)讓操作按順序執(zhí)行。此時(shí)鐘必須分配給所有順序元件,使系統(tǒng)以期望的速率運(yùn)行,并通常使用閉環(huán)控制來(lái)減小時(shí)序偏移。零延遲時(shí)鐘緩沖器使用鎖相環(huán) (PLL) 來(lái)保證緩沖的時(shí)鐘輸出與參考時(shí)鐘輸入保持一致,從而確保時(shí)鐘時(shí)序近乎完美。

本文介紹零延遲時(shí)鐘緩沖器,利用 Cypress Semiconductor、Integrated Device Technology Inc. (IDT) 和 ON Semiconductor 的示例解決方案解釋其工作原理,并詳細(xì)說(shuō)明如何控制時(shí)鐘偏移。本文還會(huì)探究測(cè)試方法,以確保這些器件的穩(wěn)定性。

時(shí)鐘偏移

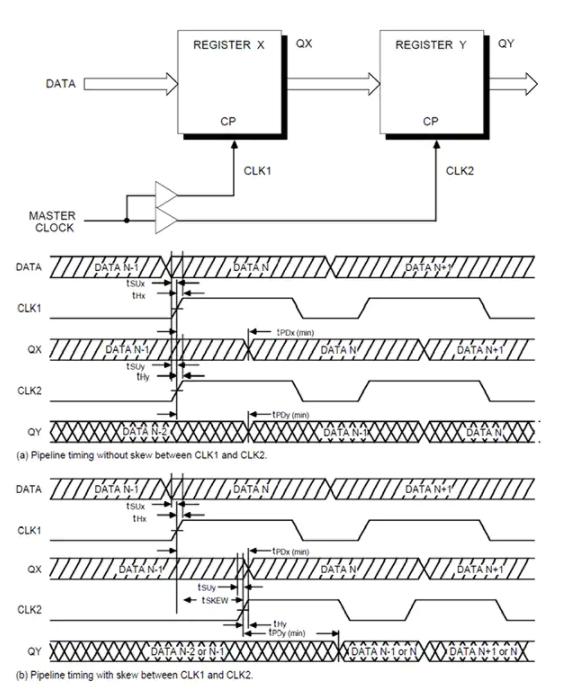

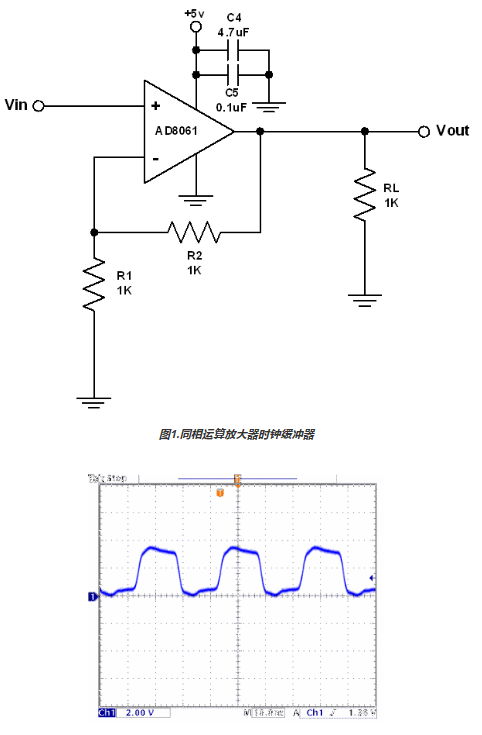

在同步數(shù)字系統(tǒng)中,時(shí)鐘可能在不同時(shí)間到達(dá)電路的不同部分,從而導(dǎo)致時(shí)鐘偏移。時(shí)鐘偏移可能會(huì)減小時(shí)序余裕,并導(dǎo)致系統(tǒng)出現(xiàn)故障(圖 1)。

圖 1:時(shí)鐘時(shí)間偏移可能影響流水線寄存器操作的簡(jiǎn)單示例。偏移的時(shí)鐘可能會(huì)違反建立和/或保持時(shí)間要求,導(dǎo)致輸出狀態(tài)不確定。(圖片來(lái)源:IDT)

考慮一個(gè)由兩個(gè)寄存器組成的簡(jiǎn)單同步系統(tǒng)。數(shù)據(jù)以流水線方式通過(guò)寄存器,使得寄存器 X 的輸出 QX 成為寄存器 Y 的輸入。時(shí)鐘通過(guò)獨(dú)立緩沖器饋入寄存器,分別指定為 CLK1 和 CLK2。如果時(shí)鐘之間沒(méi)有偏移,如圖 (a) 所示,那么滿足寄存器建立 (tSUx) 和保持 (tHx) 時(shí)間要求的數(shù)據(jù)狀態(tài) N,會(huì)在寄存器 X 傳播延遲后的第一個(gè)時(shí)鐘邊沿,鎖定到該寄存器的輸出 QX 中。CLK2 上的相同時(shí)鐘邊沿導(dǎo)致 QX 的前一狀態(tài) N-1 被該寄存器 Y 讀取,并在該寄存器的傳播延遲后出現(xiàn)在輸出 QY 中。

如果 CLK1 和 CLK2 之間存在時(shí)間偏移,如圖 (b) 所示,那么當(dāng) CLK2 出現(xiàn)時(shí),QX 可能處于轉(zhuǎn)換狀態(tài)。寄存器 Y 的輸入可能不滿足寄存器建立或保持時(shí)間要求;輸出可能不確定,從而導(dǎo)致錯(cuò)誤。

為確保時(shí)鐘偏移最小,設(shè)計(jì)人員應(yīng)讓印刷電路的印制線長(zhǎng)度匹配,選擇具有相似傳播延遲的緩沖器和其他時(shí)鐘元件,并且平衡多個(gè)時(shí)鐘源的負(fù)載。雖然這些技術(shù)有所幫助,但一般需要使用零延遲時(shí)鐘緩沖器才能獲得對(duì)時(shí)鐘偏移的良好控制。

控制時(shí)鐘偏移

引起時(shí)鐘偏移的可能原因有很多。最明顯的原因是時(shí)鐘信號(hào)在印刷電路上通過(guò)的路線長(zhǎng)度是不同的。其他偏移來(lái)源包括:時(shí)鐘通過(guò)的有源器件傳播延遲各不相同,時(shí)鐘緩沖器的負(fù)載不同,或者緩沖器存在溫度差異。雖然可以控制其中一些影響,但設(shè)計(jì)人員經(jīng)常使用有源器件和 PLL 來(lái)將時(shí)鐘重新與參考時(shí)鐘同步。

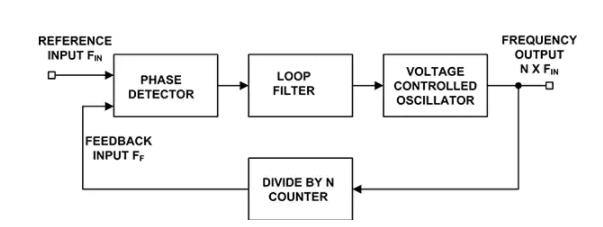

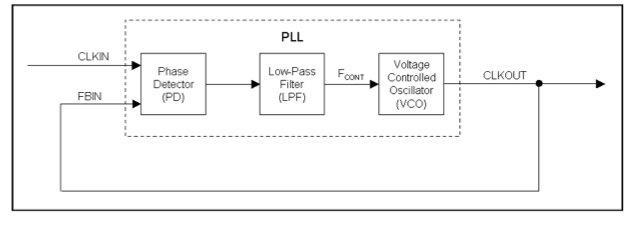

PLL 電路用于控制頻率和相位。可以配置為倍頻器、解調(diào)器、跟蹤發(fā)生器或時(shí)鐘恢復(fù)電路。每種應(yīng)用需要不同的特性,但它們都使用圖 2 所示的同一基本電路概念。

圖 2:配置為倍頻器的 PLL 框圖。它基本上是一個(gè)反饋控制系統(tǒng),控制壓控振蕩器 (VCO) 的相位。(圖片來(lái)源:Digi-Key Electronics)

圖 2 顯示了一個(gè)配置為倍頻器的基本 PLL 框圖。該電路的操作是所有 PLL 的典型操作。它基本上是一個(gè)反饋控制系統(tǒng),控制 VCO 的相位。輸入信號(hào)施加到相位檢測(cè)器的一個(gè)輸入。另一個(gè)輸入是來(lái)自 N 分頻計(jì)數(shù)器輸出的反饋信號(hào)。通常,兩個(gè)信號(hào)的頻率幾乎相同。

相位檢測(cè)器的輸出是一個(gè)與兩個(gè)輸入的相位差成比例的電壓。此信號(hào)施加于環(huán)路濾波器。該環(huán)路濾波器決定了 PLL 的動(dòng)態(tài)特性。濾波后的信號(hào)用于控制 VCO。請(qǐng)注意,VCO 的輸出頻率是提供給頻率基準(zhǔn)輸入 (FIN) 的輸入頻率的 N 倍。該輸出信號(hào)通過(guò) N 分頻計(jì)數(shù)器返回至相位檢測(cè)器。

通常,環(huán)路濾波器設(shè)計(jì)為與 PLL 應(yīng)用所需的特性匹配。如果 PLL 要采集和跟蹤信號(hào),則環(huán)路濾波器的帶寬將大于固定輸入頻率情況下的預(yù)期帶寬。PLL 接受并鎖定的頻率范圍稱為捕獲范圍。PLL 鎖定并跟蹤信號(hào)之后,PLL 所遵循的頻率范圍稱為跟蹤范圍。一般來(lái)說(shuō),跟蹤范圍大于捕獲范圍。PLL 環(huán)路濾波器還決定了信號(hào)頻率能以多快的速度改變,同時(shí)仍保持鎖定。這就是最大壓擺率。環(huán)路濾波器帶寬越窄,可實(shí)現(xiàn)的相位誤差越小。其代價(jià)是響應(yīng)速度變慢,捕獲范圍縮小。時(shí)鐘應(yīng)用中使用的 PLL 主要在固定頻率下工作。

零延遲時(shí)鐘緩沖器

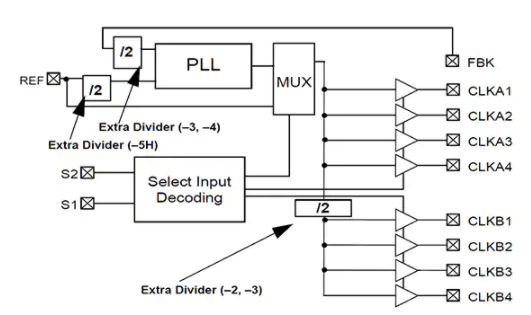

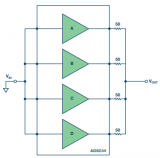

零延遲緩沖器是一種可以緩沖時(shí)鐘信號(hào)的器件,從單個(gè)參考時(shí)鐘輸入產(chǎn)生多個(gè)時(shí)鐘輸出。多個(gè)緩沖時(shí)鐘輸出相對(duì)于參考時(shí)鐘輸入的延遲很小或沒(méi)有延遲,并且輸出之間的偏移很小。Cypress Semiconductor 的 CY2308SXC-3T 零延遲緩沖器的簡(jiǎn)化框圖如圖 3 所示。

圖 3:CY2308SXC-3T 八輸出零延遲緩沖器使用 PLL 來(lái)同步所有輸出,使輸出之間的時(shí)間偏移接近零。(圖片來(lái)源:Cypress Semiconductor)

零延遲緩沖器采用積分 PLL 構(gòu)建,接受參考輸入 (REF) 和反饋輸入 (FBK) 作為其相位檢測(cè)器的輸入。反饋輸入由用戶選擇的輸出之一驅(qū)動(dòng)。PLL 的內(nèi)部相位檢測(cè)器調(diào)節(jié) VCO 的輸出相位,使其兩個(gè)輸入沒(méi)有相位差或頻率差。其中一個(gè)緩沖的時(shí)鐘輸出及其負(fù)載選擇為反饋信號(hào),通過(guò)相位檢測(cè)器反饋給 PLL。無(wú)論該輸出端的負(fù)載如何變化,PLL 都會(huì)動(dòng)態(tài)補(bǔ)償這些輸出負(fù)載變化,使得從輸入到驅(qū)動(dòng)反饋的輸出延遲為零,而不論其輸出負(fù)載有多大。

CY2308 系列有兩組四路輸出,工作頻率范圍為 10 至 133 MHz。輸入到輸出時(shí)間偏移小于 250 ps,輸出之間的時(shí)鐘偏移小于 200 ps。通過(guò)改變用于反饋輸入的輸出端負(fù)載電容,可以調(diào)整輸入到輸出時(shí)間偏移。

該產(chǎn)品系列提供多種二分頻分頻器配置。選擇的器件是帶“-3”的變型,如框圖所示,它有兩個(gè)這樣的分頻器。此配置允許用戶獲得兩倍于或四倍于參考時(shí)鐘輸入頻率的輸出。

最常用的零延遲緩沖器配置有五個(gè)輸出,有多家制造商的產(chǎn)品可供選擇。Cypress Semiconductor 的 CY2305SXI-1HT、IDT 的 2305-1DCGI8 和 ON Semiconductor 的 NB2305AI1HDR2G 是非常類似的器件。它們都有五個(gè)緩沖的時(shí)鐘輸出、一個(gè) CLKOUT 端口,以及四組時(shí)鐘輸出。與 CY2308 不同,PLL 反饋點(diǎn)固定在單個(gè) CLKOUT 信號(hào)上。

零延遲緩沖器動(dòng)態(tài)特性

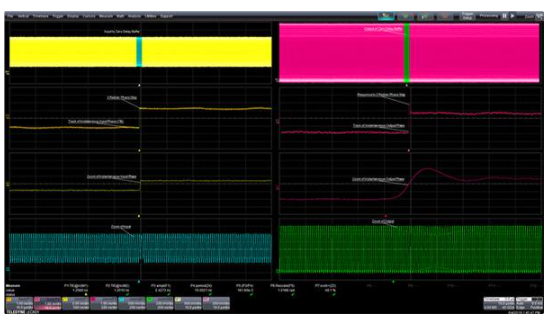

零延遲緩沖器中的 PLL 基本上是反饋控制系統(tǒng)。動(dòng)態(tài)特性由 PLL 環(huán)路濾波器控制。同任何控制系統(tǒng)一樣,重要的是評(píng)估反饋環(huán)路響應(yīng)瞬態(tài)輸入的動(dòng)態(tài)特性。一種評(píng)估方法是,施加一個(gè)含階躍變化的輸入來(lái)評(píng)估階躍響應(yīng)(圖 4)。

圖 4:在 66.67 MHz 使用 1 弧度相位階躍評(píng)估 CY2305 零延遲緩沖器的階躍響應(yīng)。左上方網(wǎng)格為輸入信號(hào),右上方網(wǎng)格為輸出信號(hào)。(圖片來(lái)源:Digi-Key Electronics)

輸入信號(hào)是 66.67 MHz 正弦波,在所采集信號(hào)窗口的中心有一個(gè) 1 弧度的階躍。此波形由任意波形發(fā)生器 (AWG) 產(chǎn)生。CY2305 零延遲緩沖器的輸入和輸出均使用示波器采集,時(shí)基設(shè)置為每格 10 μs。

圖 4 左上方網(wǎng)格為輸入信號(hào),右上方網(wǎng)格為輸出信號(hào)。時(shí)間間隔誤差 (TIE) 是實(shí)測(cè)時(shí)鐘邊沿與其理想位置的時(shí)間差,并且是針對(duì)每個(gè)波形測(cè)量的。實(shí)際上,它是以一個(gè)固定時(shí)鐘速率(本例為 66.67 MHz)為基準(zhǔn)的信號(hào)的瞬時(shí)相位。輸入和輸出的每個(gè)時(shí)鐘周期的 TIE 值繪制為一個(gè)波形,稱為 TIE 軌跡。輸入軌跡是左上方起的第二個(gè)網(wǎng)格。這里,相位的階躍是可見(jiàn)的,幅度為 2.4 ns。該值表示 66.67 MHz 時(shí)鐘頻率的 1 弧度相移。

右上方起的第二條跡線是輸出的 TIE 軌跡。輸出軌跡顯示了一些過(guò)沖,并穩(wěn)定在新的平均值以匹配輸入變化。從上往下數(shù)的第三條跡線顯示了左側(cè)輸入和右側(cè)輸出的水平擴(kuò)展縮放跡線。輸入階躍的細(xì)節(jié)顯示躍變很干凈。

放大輸出可以看出一些過(guò)沖,然后在一個(gè)大約 500 ns 持續(xù)時(shí)間的周期內(nèi)快速穩(wěn)定到新的平均值。對(duì)于如此大的相位階躍,這是一種表現(xiàn)良好的階躍響應(yīng)。它迅速穩(wěn)定下來(lái),沒(méi)有不穩(wěn)定振蕩響應(yīng)的跡象。

下方兩條跡線是對(duì)輸入(左)和輸出(右)的水平擴(kuò)充展示。在輸入中可以清楚地看到相位階躍很大,但在此時(shí)間尺度上,慢速輸出響應(yīng)不是那么顯而易見(jiàn)。

結(jié)語(yǔ)

高性能數(shù)字系統(tǒng)的設(shè)計(jì)人員需要不斷地細(xì)心關(guān)注時(shí)鐘發(fā)生和分配電路的設(shè)計(jì),以避免時(shí)鐘分配時(shí)序的差異或不確定性。此類問(wèn)題會(huì)降低系統(tǒng)性能,減少時(shí)序余裕,或?qū)е鹿δ苠e(cuò)誤。

如上所述,當(dāng)傳播多個(gè)時(shí)鐘信號(hào)并與主時(shí)鐘信號(hào)保持同步時(shí),零延遲緩沖器是實(shí)現(xiàn)主動(dòng)控制的好工具。即使檢測(cè)到輸出端發(fā)生明顯的負(fù)載變化,也能出色地執(zhí)行跟蹤。但是,如本文所述,設(shè)計(jì)人員需要仔細(xì)評(píng)估零延遲緩沖器的反饋環(huán)路動(dòng)態(tài)特性,以確保其滿足應(yīng)用要求。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論