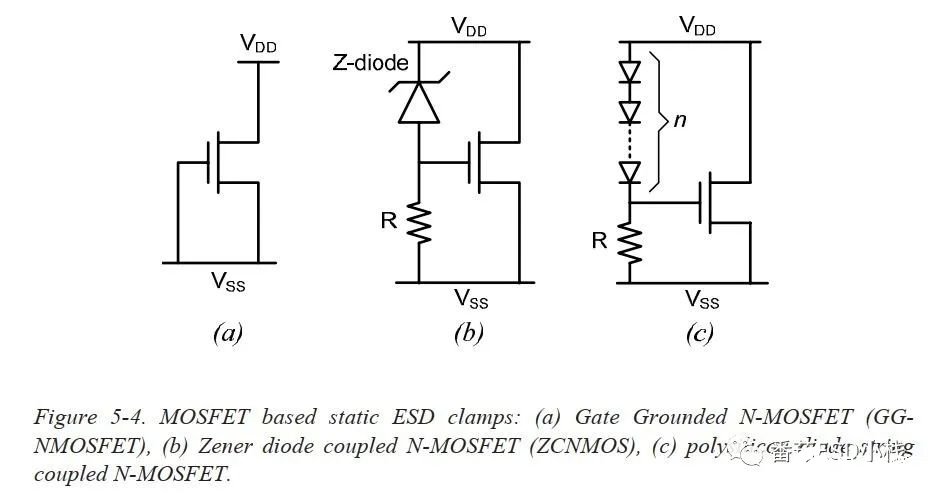

NMOS主要有兩種ESD防護(hù)應(yīng)用:一種是之前講的GGNMOS,另一種是GCNMOS(Gate Coupling NMOS)。現(xiàn)階段也已經(jīng)出現(xiàn)了(Bulk Coupling NMOS),接下來這兩種ESD防護(hù)器件都會(huì)進(jìn)行講解。

GCNMOS的工作原理與GGNMOS不同,GGNMOS是利用體寄生三極管的開啟進(jìn)行ESD靜電流的泄放通路,而GCNMOS則利用了NMOS器件的溝道作為泄放通道。GCNMOS開啟NMOS管的途徑有兩種:一種是利用靜電頻率作為觸發(fā)條件,一種是利用靜電壓作為觸發(fā)條件,如圖所示。

圖一.電壓觸發(fā)GCNMOS。

圖二.頻率觸發(fā)GCNMOS。

針對(duì)component的ESD設(shè)計(jì)是關(guān)注芯片在非正常工作狀態(tài)下的防護(hù)能力。所以片上ESD設(shè)計(jì)是防止ESD器件對(duì)正常工作產(chǎn)生干擾的同時(shí)確保在靜電來臨時(shí)能產(chǎn)生ESD靜電泄放通道,基于這個(gè)核心思想產(chǎn)生了兩者耦合方式。

電壓觸發(fā):

正常工作情況下VDD—VSS的壓差小于齊納或二極管串的導(dǎo)通電壓,此時(shí)NMOS的柵壓為低壓,NMOS關(guān)斷。而當(dāng)VDD上有ESD電流產(chǎn)生后,這部分電流會(huì)集聚在二極管串的陽(yáng)極或齊納管的陰極,直到電壓足夠?qū)ㄆ骷?梢园袳SD電流類比為水流,ESD電流始終要完成泄流,在泄流前會(huì)一直聚集產(chǎn)生電壓,直到內(nèi)部器件擊穿產(chǎn)生通路或者ESD防護(hù)器件開啟產(chǎn)生通路。利用這一特性調(diào)整齊納管或二極管串的導(dǎo)通電壓Von,使得VDD

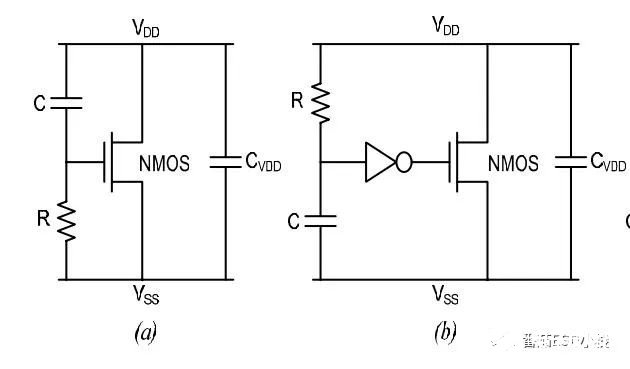

頻率觸發(fā):

通過RC電路的頻率特性,將高頻的ESD電流與普通上電的波形進(jìn)行區(qū)分。ESD的波形如圖所示,

圖三.HBM波形。

HBM的波形中0~10nm內(nèi)會(huì)存在一個(gè)上升沿,到達(dá)峰值后,在150ns的時(shí)間內(nèi)衰減至峰值的20%左右,整個(gè)ESD脈沖的持續(xù)時(shí)間大概為1us。為了便于理解及方便系統(tǒng)化設(shè)計(jì),將HBM的時(shí)域波形轉(zhuǎn)化為頻域波形,如圖四所示。

圖四.HBM波形的頻域。

(這里只是為了便于下文敘述舉個(gè)例子,真正的變換遠(yuǎn)比這復(fù)雜得多)。HBM波形中能量主要集中在前20ns內(nèi),在這個(gè)頻域范圍內(nèi)變換的正弦波也是我們需要重點(diǎn)關(guān)注的,設(shè)這個(gè)頻率范圍為ωESD。頻率觸發(fā)的GCNMOS的工作原理是利用RC電路的頻率響應(yīng)特性對(duì)ESD波形產(chǎn)生響應(yīng)。當(dāng)VDD軌上產(chǎn)生靜電波形后,RC部分的等效電路如圖五。

圖五.ESD-RC等效電路。

電容的阻抗為1/jωC,則HBM的主要能量集中在高頻部分,其等效阻抗較小,電壓降主要集中在電阻上,A點(diǎn)電位為高,當(dāng)電壓大于NMOS的閾值電壓后,溝道開啟,出現(xiàn)從VDD到GND的靜電流泄放通道。而當(dāng)ESD主頻結(jié)束后,RC的固有響應(yīng)也會(huì)使得NMOS持續(xù)開啟一段時(shí)間,確保NMOS在整個(gè)ESD事件中維持開啟狀態(tài)。而當(dāng)正常上電時(shí),等效電路如圖六。

圖六.POWER-ON-RC等效電路。

一般電路的上電速度遠(yuǎn)低于ESD放電頻率,此時(shí)電容阻抗較大,電壓集中在電容上,A點(diǎn)電位為低,NMOS關(guān)斷,不會(huì)對(duì)正常工作產(chǎn)生影響。??目前的設(shè)計(jì)也有如圖二(b)中所示將電容電阻位置對(duì)調(diào)的,其基本原理與CR相同,不過需要在電路中加一個(gè)反相器,而這個(gè)反相器不僅能改變電位,同時(shí)還能通過改變其結(jié)構(gòu),提高后一級(jí)NMOS的柵壓,縮減R和C的面積。

舉個(gè)例子:

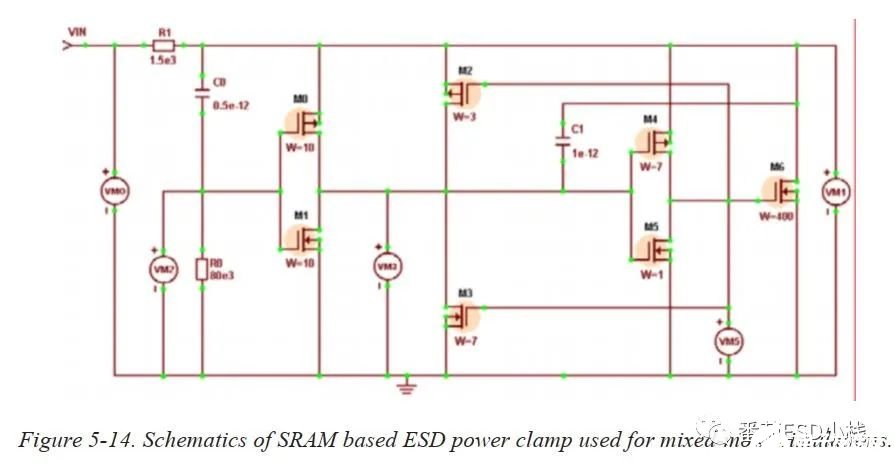

圖七. SRAM ESD power clamp電路圖

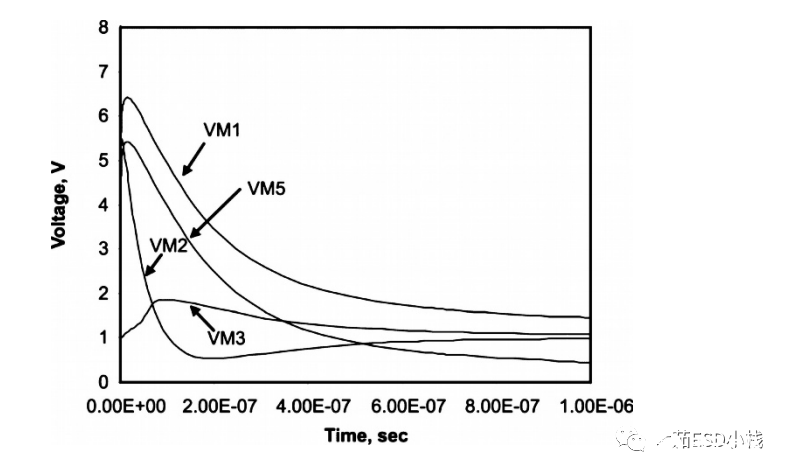

圖八. SRAM?ESD?power clamp仿真結(jié)果。

這是一種通過SRAM結(jié)果實(shí)現(xiàn)CR電壓修調(diào)的例子,其電路圖和仿真結(jié)果如圖7,8所示。可以看出因?yàn)镾RAM結(jié)果的存在,VM2不需要一直維持很高,CR的時(shí)間常數(shù)τ很低,說明C與R的面積也不需要很大。

目前的GCNMOS電路中也會(huì)添加一個(gè)shut-down control電路,實(shí)現(xiàn)芯片上電后斷路或短路GCNMOS的作用。這也是和component ESD的設(shè)計(jì)思路相關(guān),component ESD的防護(hù)場(chǎng)景也只是針對(duì)芯片在非使用下的靜電。而沒有shut-down control可能存在芯片上電后面對(duì)system ESD時(shí)GCNMOS開啟的誤觸發(fā)情況。

GCNMOS相較于GGNMOS的優(yōu)點(diǎn)是可以有效減低寄生參數(shù)的影響,廣泛應(yīng)用于高速場(chǎng)合,但是其面積需求也大,并且不能應(yīng)用于高壓,負(fù)壓等復(fù)雜場(chǎng)合。同時(shí)關(guān)于GCNMOS的布局布線也有相對(duì)應(yīng)的要求,其實(shí)ESD電路的關(guān)鍵點(diǎn)還是在版圖上(有機(jī)會(huì)了再展開講講)。

這期也只是講解了GCNMOS的基本原理,現(xiàn)階段GCNMOS已經(jīng)開始利用柵體雙耦合的效應(yīng)以實(shí)現(xiàn)面積最大利用率,甚至出現(xiàn)了多米諾鏈?zhǔn)紼SD防護(hù)結(jié)構(gòu)(有機(jī)會(huì)了可以講講(?ω?))。

上期講了最基本的GCNMOS的工作原理,這期作為一個(gè)補(bǔ)充,拓展一下現(xiàn)階段一些先進(jìn)的GCNMOS設(shè)計(jì)和GCNMOS在設(shè)計(jì)中需要注意的地方。

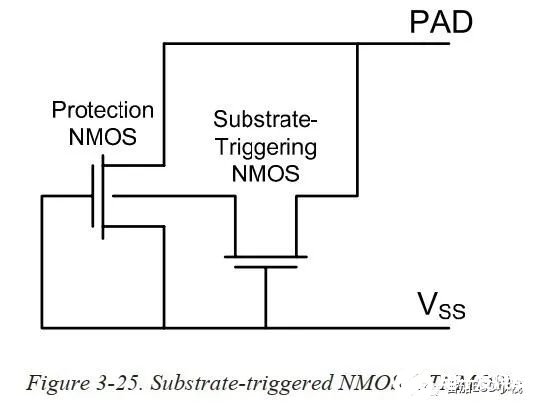

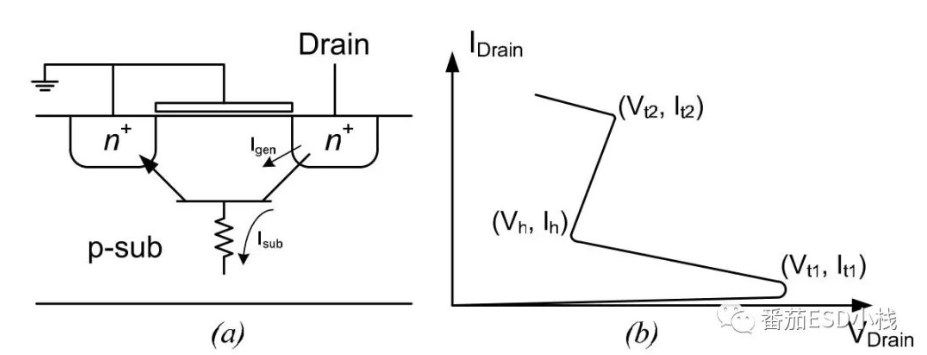

上期講解的主要是柵觸發(fā)GCNMOS,還可以通過體觸發(fā)實(shí)現(xiàn)ESD防護(hù)。這類NMOS被稱為STNMOS(Sub-strate triggering NMOS),如圖一所示。

圖一.STNMOS示意圖。

這類NMOS是將部分電流注入到Protection NMOS的襯底中,協(xié)助開啟Protection NMOS中的寄生NPN三極管(前面的章節(jié)已經(jīng)講過NMOS中存在的NPN三極管)。體觸發(fā)便是將維持電流Ih注入寄生三極管的基級(jí),這樣不需要Drain與substrate間形成雪崩擊穿便可將三極管導(dǎo)通,同樣能降低trigger voltage 同時(shí)因?yàn)槠溥€是利用三極管形成泄放通道,STNMOS的TLP曲線還是會(huì)表現(xiàn)出微弱的snap-back特性。又因?yàn)椴恍枰獜臏系佬狗臙SD電流,STNMOS本身的魯棒性要強(qiáng)于GCNMOS。

相對(duì)于Protection NMOS而言,Substrate Triggering NMOS的尺寸要小很多,這樣確保了兩者的開啟先后順序。兩者的一次擊穿電壓相同,但是Substrate?Triggering?NMOS的trigger voltage要小于Protection NMOS的trigger?voltage,確保先于Protection NMOS開啟。然后進(jìn)入holding狀態(tài)將維持電流Ih注入Protection NMOS的襯底中,促使其直接進(jìn)入導(dǎo)通狀態(tài)。Substrate?Triggering?NMOS的TLP特性決定了Protection NMOS的TLP特性。

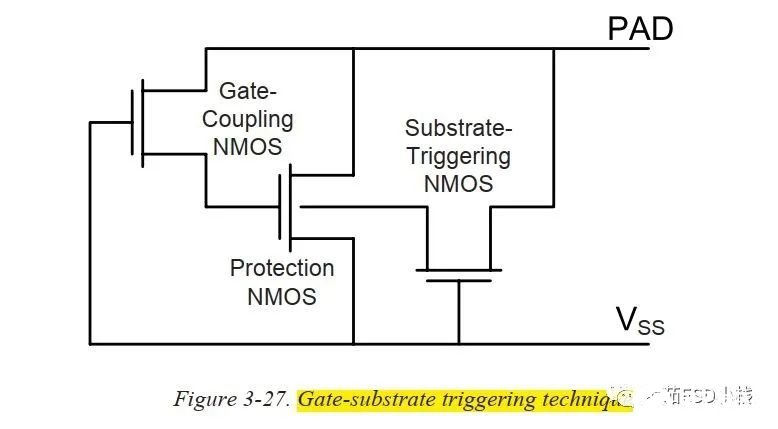

因?yàn)轶w寄生三極管與溝道并不沖突,將體觸發(fā)與溝道導(dǎo)通進(jìn)行結(jié)合。便有了Gate substrate triggering NMOS,如圖二所示。

圖二.Gate-Substrate triggering?NMOS

這種ESD保護(hù)電路的原理便是同時(shí)利用了溝道與寄生三極管作為泄放通道。GCNMOS的維持電壓Vh開啟Protection NMOS的溝道,Substrate Triggering NMOS將維持電流Ih,注入襯底開啟三極管。這樣能大大提高Protection NMOS的導(dǎo)通效率。相當(dāng)于一個(gè)NMOS與一個(gè)NPN同時(shí)進(jìn)行ESD泄放。同時(shí)襯底的電位還能降低NMOS的閾值電壓,更利于開啟。

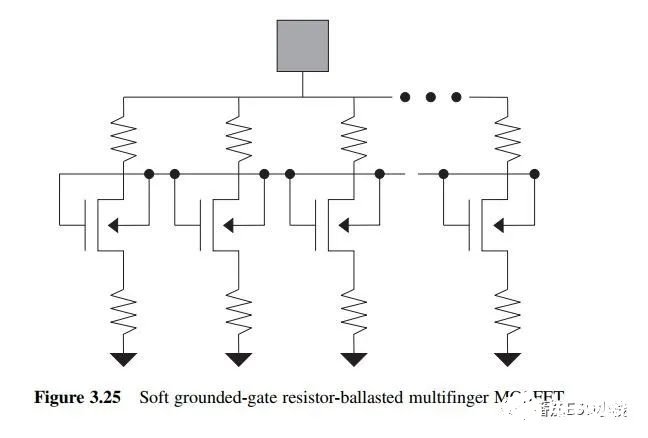

圖三.多指“軟”鎮(zhèn)流電阻GGNMOS。

該結(jié)構(gòu)是利用了GGNMOS發(fā)生snap-back后的維持電壓vh作為下一級(jí)NMOS的溝道開啟電壓。當(dāng)最外側(cè)的GGNMOS優(yōu)先開啟后,維持電壓開啟后一極的NMOS溝道,以此類推形成鏈?zhǔn)紼SD防護(hù)結(jié)構(gòu),而該結(jié)構(gòu)中的電阻為鎮(zhèn)流電阻,能使得電流均勻分布(這里面的技術(shù)細(xì)節(jié)有機(jī)會(huì)再講 (*?▽?*))。

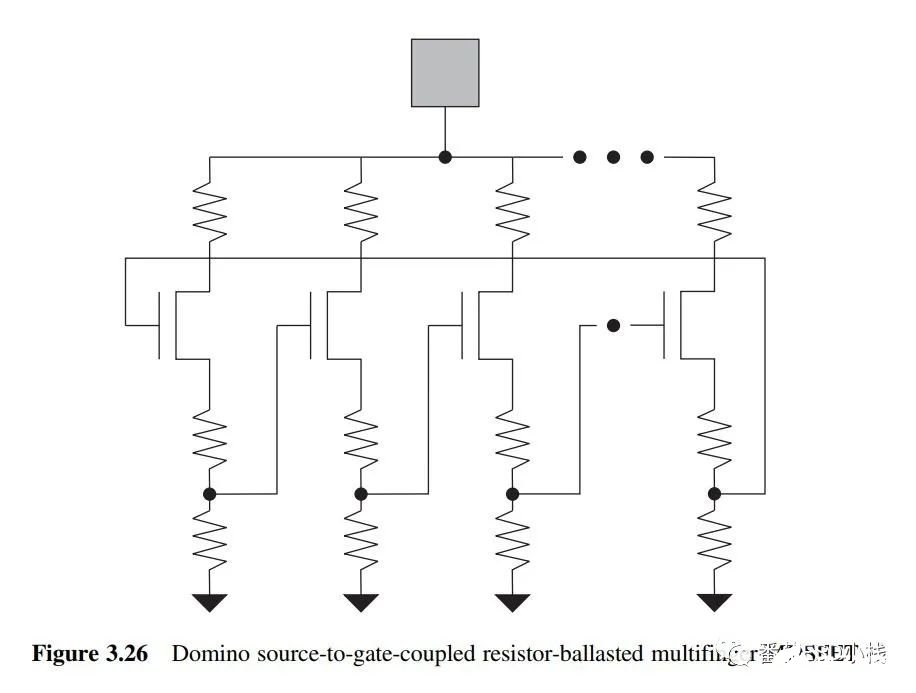

圖四.多米諾ESD防護(hù)結(jié)構(gòu)。

該結(jié)構(gòu)也是鏈?zhǔn)紼SD防護(hù)中的一種,利用source的壓差開啟下一級(jí)的GCNMOS。因?yàn)殡娐返内吥w效應(yīng),這種鏈?zhǔn)浇Y(jié)構(gòu)一定是最外側(cè)的NMOS先開啟,然后最外側(cè)NMOS產(chǎn)生電壓,由外及內(nèi)鏈?zhǔn)介_啟,就和多米洛骨牌一樣,被開啟后繼續(xù)開啟下一個(gè)。而source端的電阻起到了分壓的作用,將ESD電流轉(zhuǎn)換為電壓,形成GCNMOS。

雖然GCNMOS的電路結(jié)構(gòu)比較簡(jiǎn)單,但是針對(duì)不同的應(yīng)用場(chǎng)合會(huì)有不同的lay out方式,而且針對(duì)ESD防護(hù)的布軌問題也要針對(duì)不同應(yīng)用場(chǎng)景進(jìn)行單獨(dú)設(shè)計(jì)。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論