802.11應用架構根據IEEE 802.11無線標準,提供了立即可用、方便修改的實時正交頻分復用(OFDM)物理層(PHY)和底層媒體訪問控制層(MAC)參考設計。 802.11應用架構包含于LabVIEW Communications系統設計套件(簡稱 LabVIEW Communications)中。

這個架構提供了良好的開發起點,幫助研究人員探索全新的算法和架構來支持大幅增長的端點數量、發明新波形來調制/解調信號或尋找全新的多天線架構來充分運用無線媒介的自由度,進而找到改良802.11標準的方式。

802.11應用架構包含了使用LabVIEW Communications開發的PHY塊和MAC塊。 該框架搭載了強大的Xilinx Kintex-7 FPGA平臺與Intel x64通用處理器,這兩者皆可緊密集成NI軟件無線電(SDR)硬件的RF和模擬前端裝置。

我們完全重新設計了這個框架,使用戶可以輕松對其進行修改,同時遵循802.11標準的主要規范。 這種設計可讓無線研究人員根據802.11標準快速搭建實時原型開發實驗室并開始運行。 他們還可以專心改良特定的系統項目、輕松修改設計以及將其創新與現有標準進行比較。

1. 范圍和標準遵循

802.11應用架構提供了單個站點的功能,包含接收(RX)與發射(TX)功能,并使用OFDM作為核心數字調制機制。 OFDM適用于復雜度低的多功能PHY實現,并且可減緩寬頻無線信道的離散效應。 OFDM采用快速傅立葉變換(FFT)和快速傅立葉逆變換(IFFT)來實現發射機與接收機的頻域PHY處理。 通過在頻域上處理數據,OFDM可有效地讓PHY通過通信頻譜的平行窄頻區段來傳輸數據。 由于減緩信道離散只需要針對每個區段進行一次數學運算,所以通過窄頻區段來執行數據傳輸是相當理想的做法。

以下各部分介紹了所提供的PHY與底層MAC功能以及所遵循的802.11標準。

1.1

PHY層

802.11應用架構提供了下列PHY發射機功能:

加密

卷積編碼和位交織

導頻序列生成

BPSK/QAM星座映射器

信號字段生成

通過IFFT生成OFDM碼元

循環前綴(CP)插入

前導碼字段補充

為接收機端提供了特定函數對應的補充功能:

數據包檢測

時間和頻率同步

自動增益控制

信號字段檢測

循環前綴去除

通過FFT解調OFDM碼元

信道估算和迫零均衡

BPSK/QAM解調

基于維特比譯碼器的卷積譯碼(包括分選)

解密

802.11應用架構可支持IEEE標準所規定的不同OFDM配置。 版本1.0可支持20 MHz a/g和20 MHz n/ac這兩種副載波格式,具體特性如下:

系統帶寬: 20 MHz

副載波頻寬: 每個副載波(窄頻區段)占用312.5 kHz

副載波分配

. 20 MHz a/g: 分配53個連續副載波(載波頻率的中央(第27個)副載波)

. 20 MHz n/ac: 分配57個連續副載波(載波頻率的中央(第29)副載波)

零位中央副載波: 中央副載波通過歸零可避免本地振蕩器出現基帶饋通。

導頻副載波可允許接收機補償殘留的頻率同步失配和相位漂移:

. 20 MHz a/g: 53個副載波中有4個是導頻副載波

. 20 MHz n/ac: 57個副載波中有4個是導頻副載波

發射機每個IFFT輸出字段前面都會有800 ns的循環前綴,可保留接收器端的循環卷積,避免碼元之間相互干擾。所以每個OFDM碼元可用來傳輸數據的副載波數量如下:

. 20 MHz a/g: 48個副載波

. 20 MHz n/ac: 52個副載波

這樣一來,對于20 MHz的信道分配而言,48 * 312.5 kHz = 15 MHz,52 * 312.5 kHz = 16.25 MHz。 這兩個頻譜數量分別對應20 MHz a/g和20 MHz n/ac模式的數據。

802.11應用架構采用簡化的PHY幀格式。 圖1為已實現的格式。

圖1. 一般的PHY架構格式

PHY架構包含以下字段:

傳統模式的短訓練字段(Legacy mode short training field, L-STF) - 用于接收機端的增益控制、數據包檢測、頻率同步的靜態字段。 字段時間長度為8 ?s。

傳統模式的長訓導字段( Legacy mode long training field,L-LTF) - 用于時間同步與信道估算的靜態字段。 字段時間長度為8 ?s。

傳統模式的信號字段(Legacy mode signal field, L-SIG)- 包含已應用的調制編碼機制(MCS)和框架長度等信息的動態字段。

超高吞吐量短訓練字段(Very high throughput short training field, VHT-STF):用于超高吞吐量模式802.11ac的靜態字段。 目前的接收機實現方案往往忽視了VHT-STF字段,僅評估L-LTF字段。

超高吞吐量長訓練字段(Very high throughput long training field, VHT-LTF):用于超高吞吐量模式802.11ac的靜態字段。 目前的接收機實現方案往往忽視了VHT-LTF字段,僅評估L-LTF字段。

負載(PAYLOAD)屬于動態字段,僅由MAC消息定義。 負載的長度取決于信號傳輸調制機制。 最長的負載采用二進制相位位移鍵控(BPSK)機制。 最短的負載則采用64-QAM機制。

上述的框架格式符合IEEE 802.11ac規范,但是并未提供超高吞吐量信號字段(High Throughput Signal Field,VHT-SIG-A 或 VHT-SIG-B)。

1.2

媒體訪問控制(MAC)層

802.11應用架構提供了下列MAC發射機功能:

. DATA PDU生成,包括添加地址信息

. 幀檢驗序列(Frame check sequence, FCS)生成

. ACK PDU生成

以下功能適用于接收機端:

. 幀檢驗序列(Frame check sequence, FCS)檢驗

. ACK PDU傳輸的地址檢驗和觸發

. MAC SDU提取

802.11應用架構針對MAC PDU采用了一個簡化的框架結構。 圖2顯示的是用于數據和ACK幀的數據包結構。

圖2.MAC PDU幀結構

MAC PDU幀的第一個字段是TYPE字段,占用了一個字節。 接收機根據該字段判斷要解碼的MAC PDU幀。 802.11應用架構中,TYPE只有兩種類型: DATA(0x08)和ACK(0xD4)。 未來應用架構可能會包含更多類型。 MAC數據包中第二和第三個字段長度均是6個字節,分別代表目標的MAC位址和來源的MAC位址。 MAC數據包的第四個字段是MESSAGE字段, 其中包含來自更高層協議的所有數據,通過無線鏈路進行傳輸。 MAC數據包的第五個字段是CRC32字段, 長度為4個字節,由FPGA的CRC32模塊生成,附加到每個信息上以便檢錯。

1.3 遵循IEEE 802.11標準

802.11應用架構遵循一部分特定的IEEE 802.11標準。選擇特定支持功能的原因在于盡可能簡化代碼以便修改,同時遵循802.11標準的主要架構。

除了上述的簡化數據包格式之外,以下是其他固定或簡化的設置和步驟,有助于降低應用架構的復雜度:

僅支持單一輸入/輸出(SISO)傳輸模式

僅限BPSK、QPSK、16 QAM和64 QAM調制與編碼機制(MCS)

專用交錯復用器

專用SIFS時序

簡化的自動增益控制(AGC):802.11應用架構提供簡化的AGC機制。 其中一部分在主機上實現,所以需要較長的調整時間。 AGC循環必須接收多個數據包才能計算并設置正確的增益值。

2. 實現概述

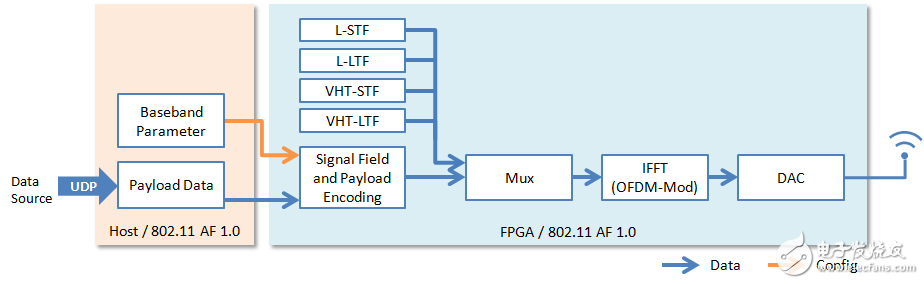

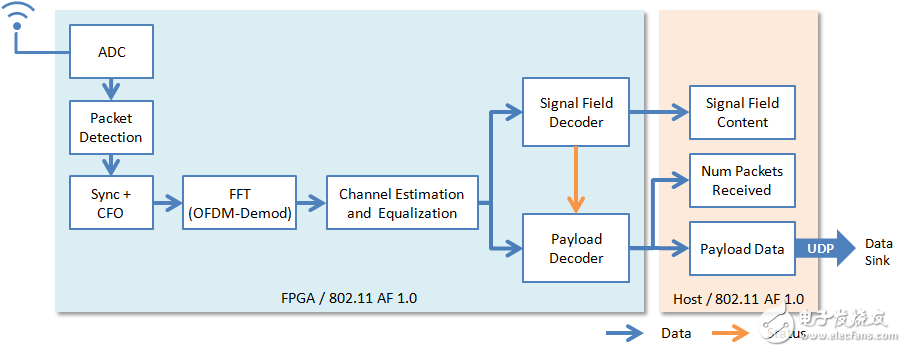

由于802.11系統的延遲要求,大多數區塊都會在FPGA上實現。 不需要實時執行功能和FPGA初始化與控制功能的特性都在主機處理器上實現。 發射器和接收器實現方式分別如圖3和圖4所示,其中顯示了主機-FPGA的分區。

圖3.發射器示意圖

就發射器端而言,主機會把讀取自UDP插槽的用戶數據傳輸至FPGA。 也可選擇使用隨機產生的數據包。 主機代碼會顯示輸入控件,以便設置參數,例如調制和編碼機制。 然后在FPGA上應用這些參數來執行基帶與RF處理。 FPGA上的信號處理還包含了PHY幀合成、OFDM調制和轉換至模擬信號。

圖4.接收器示意圖

在接收器端,FPGA會執行所有的基帶運算以便接收并解碼信號,例如數據包檢測和同步化、OFDM解調制、信道估算和均衡以及解碼等。 解碼后的數據傳輸至主機。 主機可能會隨意把接收到的數據寫入UDP socket。 此外,FPGA會把額外的數據(例如所接收的I/Q樣本和所檢測的數據包解調后的I/Q星座圖)傳輸至主機。 額外數據可用于記錄調試日志,也可用于顯示頻譜或接收到的星座圖。

第三小節提供更多FPGA的實現信息,第四小節則闡述了主機實現。

3. FPGA實現

3.1 概述

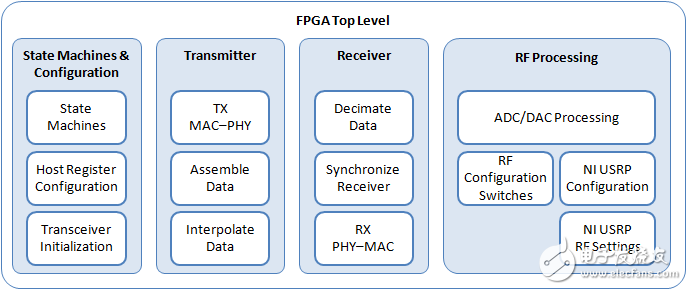

FPGA頂層實現了下列功能:

狀態機和常規配置

發送處理

接收處理

射頻處理

代表這些功能的元素會放在FPGA頂層架構圖中,分成四欄,如圖5所示。 每欄皆包含多個循環;所以舉例來說,最左欄是一個狀態機器處理循環、一個主機寄存器配置循環和一個收發器初始化循環。

圖 5. FPGA頂層示意圖

3.2小節會進一步解釋狀態機。 3.3和3.5小節會分別闡述發射器和接收器。 如需了解更多射頻處理細節,請查看3.4小節。

主機寄存器配置(Host Register Configuration)循環負責執行過程中主機的配置參數更改。 這些更改可能包含調制和編碼機制、設備MAC位址和副載波格式等信息。 該循環會生成FPGA的相關配置,例如數據副載波的數量和每個QAM碼元的比特數。

收發器初始化(Transceiver Initialization)循環是當前實現的一個占位(placeholder)符,可用于在整個收發器開始運行前進行常規配置和初始化。

3.2 狀態機

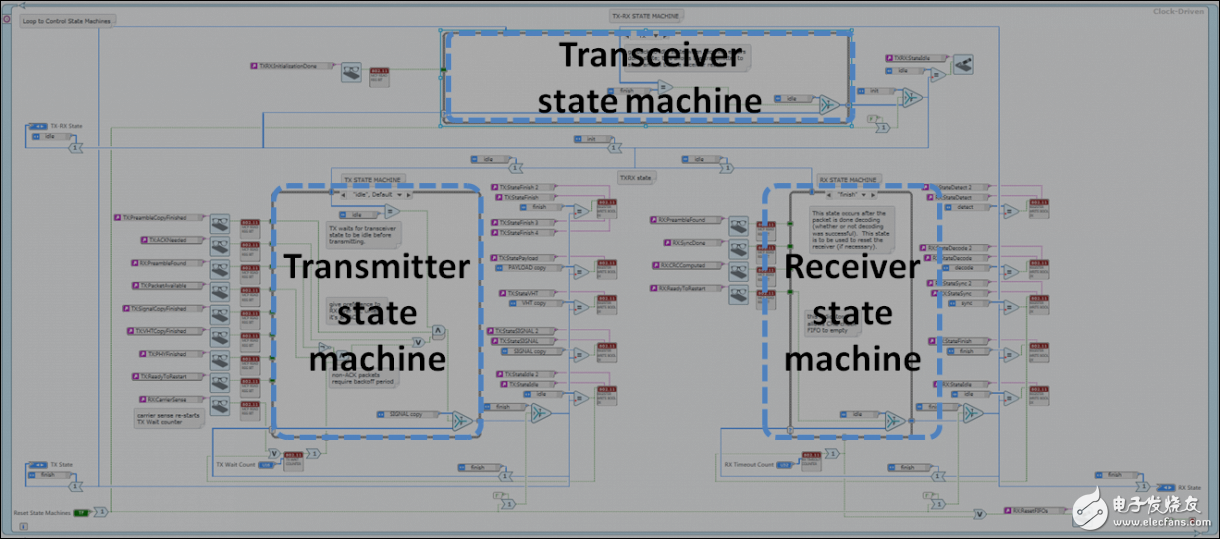

為了控制PHY處理功能以便收發數據包,FPGA上實現了下列三個狀態機:

收發器狀態機(Transceiver state machine):協調發射器與接收器狀態機的順序運行。

發射器狀態機(Transmitter state machine):協調發射器的運行。

接收器狀態機(Receiver state machine):協調接收器的運行,包含數據包檢測與同步。

圖6顯示了FPGA頂層狀態機循環內的狀態機位置。

圖6.狀態機循環內的狀態機位置

3.2.1 收發器狀態機

收發器狀態機有四個狀態,可在發射器和接收器之間進行協調。 請注意,802.11接收器的默認狀態是數據包偵聽。 因此,收發器默認的idle狀態對應至接收器的detect狀態。如果發現數據包前導碼,收發器就會變成rx狀態,直到數據包解碼完成為止。 一旦有能夠傳輸的數據包,同時狀態機處于idle狀態 (也就是接收器則處于detect狀態)時,收發器會迅速切換至發射狀態。

狀態

說明

備注

init

此狀態表示收發器首次啟動。

?

idle

接收器正在偵聽數據包。

?

tx

發射器正在生成數據包。

?

rx

接收器正在同步或解碼數據包。

?

3.2.2 發射器狀態機

發射器狀態機有五個狀態,如下表所示。

狀態

說明

備注

idle

發射器正在等待數據發送。

為了快速啟動發送操作,L-STF和L-LTF預先計算的樣本已經寫入重采樣FIFO。 如需更多信息,請查看3.3.3小節。

SIGNAL copy

生成信號字段并復制到重采樣FIFO。

收發器必須處于idle狀態才能進入此狀態。

?VHT copy

超高吞吐量(Very high throughput, VHT)前導碼會復制到重采樣FIFO。

?

PAYLOAD copy

生成數據負載字段并復制到重采樣FIFO。

?

finish

重新設置發射器。

3.2.3 接收器狀態機

接收器狀態機有五個狀態,如下表所示。

狀態

說明

備注

idle

接收器正在等待數據包檢測初始化。

?

detect

接收器正在偵聽數據包(數據包檢測模式)。

收發器必須處于idle狀態才能進入此狀態。

sync

接收器與檢測到的數據包進行同步。

收發器必須處于tx狀態才能進入此狀態。

decode

接收器正在處理接收到的數據包。

?

finish

接收器已完成數據包接收

?

3.3 發射器

3.3.1 概述

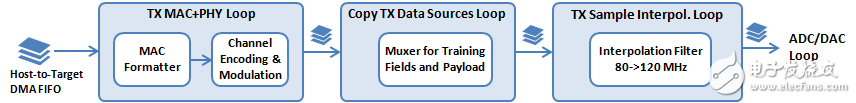

發射器會分成三個循環,如圖7所示。

TX MAC + PHY循環會讀取主機所提供的數據,并且構建MAC PDU數據包,如1.2節所述。 接著MAC PDU數據包的比特會經過信道編碼,并且以80 MS/s的采樣率生成復數值的基帶樣本。

Copy TX data sources循環會通過添加丟失的信號字段來構建PHY幀格式,如1.1節所述。

TX sample interpolation循環會把I/Q基帶樣本的采樣率從80 MS/s轉換為120 MS/s,以便滿足DAC的要求。

下面幾節將會進一步介紹這些循環。

圖 7. 發射器循環

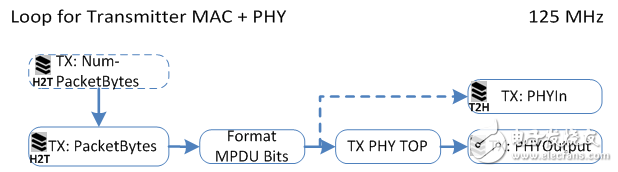

3.3.2 發射器MAC+PHY的循環

TX MAC+PHY Loop的輸入與輸出如8所示。主機數據通過一個稱為TX:PacketBytes的直接內存訪問Host-to-Target FIFO提供。 另一個Host-to-Target FIFO稱為TX:NumPacketBytes,可提供要讀取的字節數的控制信息。 TX:PacketBytes所提供的數據包含目標MAC位址和MAC SDU負載。

圖 8. 發射器MAC + PHY循環的輸入與輸出

Format MPDU Bits區塊會根據消息信息和設備配置生成剩余字段,主要是插入1個字節的TYPE字段和6個字節的SRC-MAC字段,并且附加一個4字節的CRC32字段。 所獲得的MAC PDU幀如圖2的結構所示。如果要進行調試,此幀也通過TX: PHYIn target-to-host FIFO寫入主機。

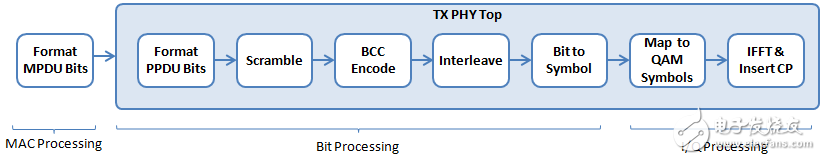

下一個區塊叫做TX PHY TOP,包含了信道編碼和基帶調制處理,如圖9所示。

圖 9. TX PHY Top的程序框圖

Format PPDU Bits區塊可執行兩項操作:

1、附加于L-SIG字段前方,L-SIG字段包含PSDU比特數量、每個數據副載波的比特(也就是調制機制)和編碼率。

2、補充填充位,這樣一來數據包就可以匹配特定QAM星座圖中OFDM碼元的比特位界限。 舉例來說,通過64-QAM編碼而成(每個碼元6位)且長度為168字節的消息(由MAC PDU、服務位和尾位組成)會以224QAM碼元來表示。 如果每個OFDM碼元有48個數據副載波并且使用a/g模式時,下一個可用的界限就是240 QAM碼元。 相差16個碼元意味著需要補充96個填充位。

MAC格式化區塊完成之后,PHY幀就可以準備執行信道編碼。 這些比特會進行加密,通過二進制卷積碼(Binary Convolutional Code, BCC)完成交錯編碼。 要使用的BCC速率取決于調制與編碼機制(MCS),這一機制由主機提供并用于傳輸數據數據包。 ACK數據包一律采用MCS 0來傳輸。

交錯的比特會映射至QAM U8碼元索引(而不是復合的基帶樣本)。 這些碼元索引可簡化QAM碼元的表示,有助于減少碼元映射器的內存占用。 生成碼元索引后,QAM碼元就會映射至副載波結構,如1.1小節所示。 副載波會根據每個OFDM碼元以正確的順序排列,零子載波則會在中心頻率下插入。 零子載波也會插入到頻帶邊緣,以確保有效的FFT變換。

完成子載波格式化之后,QAM碼元索引就會映射至復數基帶(同相和正交)樣本。 IFFT區塊會把頻域I/Q樣本轉換至時域I/Q樣本。 發射器和接收器的FFT大小都是256,有助于輕松擴展帶寬。 IFFT也會插入循環前綴,長度為64個樣本。 這樣一來,每個OFDM碼元就會有320個樣本,由于802.11標準的OFDM碼元持續時間為4ms,采樣率就等于80 MS/s。

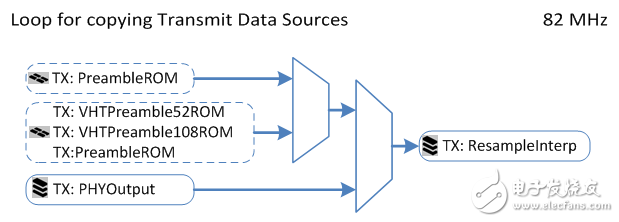

3.3.3 復制傳輸數據源(Copying Transmit Data Sources)循環

如圖10的循環所示,不同TX數據源的復數值基帶樣本會通過多個路徑進行傳輸,最終生成一個802.11 PHY幀,如1.1小節所述。 不同訓練字段的復數值基帶樣本,也就是L-STF、L-LTF、VHT-STF和VHT-LTF,都會經過預計算并儲存至ROM表格。

圖 10. 復制傳輸數據源循環的輸入與輸出

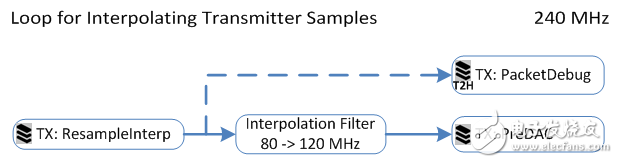

3.3.4 內插發射器樣本(Transmit Sample Interpolation)循環

圖11所示的循環把采樣率從80 MS/s轉換為120 MS/s,也就是NI USRP默認的DAC采樣率。 基本上,采樣率轉換是使用一個2:3內插器完成的。 如果要進行調試,可以使用目標至主機的DMA FIFO,也就是TX:PacketDebug,以80 MS/s的采樣率訪問802.11幀的復數值基帶樣本。

圖 11. 內插發射器樣本循環的輸入與輸出

3.4 RF處理

RF處理循環是從NI USRP Streaming Sample Project中截取出來的。 如需深入了解RF處理循環,請查看NI USRP Streaming Sample Project文檔。 ADC和DAC處理循環已針對802.11應用架構進行了簡化與調整。除了項目范例之外,RF0和RF1發射端口1與接收端口1和2的啟用/禁用是由主循環控制,而非RF配置開關(RF Configuration Switches)循環。

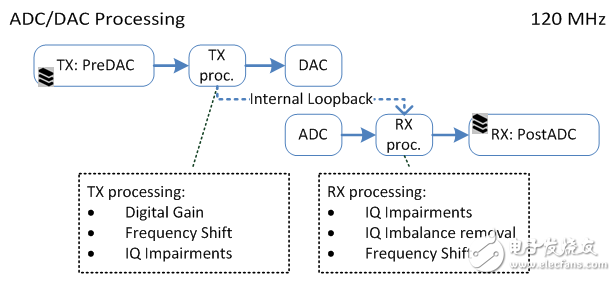

圖 12. FPGA頂層的ADC/DAC處理

圖12顯示了802.11應用架構FPGA頂層DAC/ADC界面循環的原理圖。 此循環包含DAC與ADC界面以及必要的處理功能,可用于接收基帶信號并將基帶信號進行轉換以便傳輸。

數字增益、頻移和I/Q減損補償都會在TX信號傳輸至NI USRP DAC之前應用到信號中。 發射信號的數字I/Q樣本會通過FIFO(TX:PreDAC)進入循環。

在接收器端,NI USRP ADC的數據經讀取之后進入接收信號處理程序,以修正I/Q減損與頻移。 然后I/Q樣本會通過FIFO (RX:PostADC)傳輸至下一個處理循環。

使用內部的環回模式可跳過RF處理程序。 一旦啟動RF處理,TX數據就會直接進入RX處理鏈。

3.5 接收器

3.5.1 概述

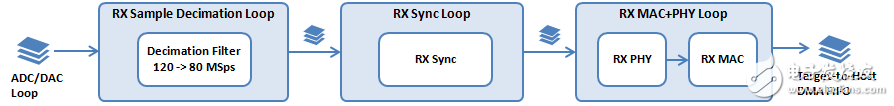

接收器分成三個循環,如圖13所示。

1、RX采樣抽取循環(RX Sample Decimation Loop)會抽取來自ADC的RX樣本,以盡量達到理想的I/Q采樣率,也就是80 MS/s。

2、RX同步循環(RX Sync Loop)負責完成數據包檢測、時間與頻率同步和循環前綴消除。

3、RX MAC + PHY循環則會執行PHY層的信道估算、均衡、OFDM解調與解碼以及MAC層的CRC與地址檢查。

圖13.接收器循環

下面將進一步討論上述三個循環。

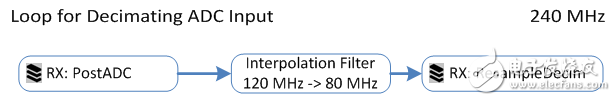

3.5.2 接收器采樣抽取(Receiver Sample Decimation)循環

圖14為接收器采樣抽取循環,用于轉換采樣率。 和DAC一樣,ADC的工作頻率為120 MS/s。和發射器一樣,接收器的處理頻率為80MS/s。所以需要使用一個3:2抽取器來連接ADC和FPGA上的接收器處理。

圖 14. RX采樣抽取循環的輸入和輸出

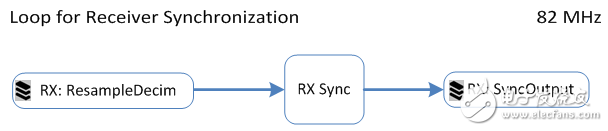

3.5.3 接收器同步(Receiver Synchronization)循環

圖15顯示了接收器同步循環的界面,圖16則是同步的程序框圖。

圖 15. 接收器同步循環的輸入與輸出

圖 16. TX PHY Top的程序框圖

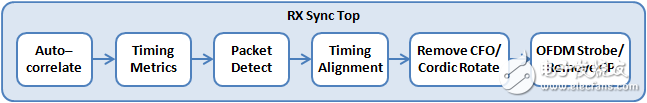

重采樣之后,開始進行基于L-STF架構的同步。 該過程以Schmidl-Cox算法為基礎。

同步單元內的第一個模塊會計算樣本的自動關聯。 計算自動關聯所使用的時間延遲以L-STF序列的周期性為基礎。 這個數據會進一步轉換成能量歸一化和平均的關聯指標。 輸出端處也會計算平均載波頻率偏置(Carrier Frequency Offset, CFO)估算序列。 后續模塊會使用這些輸出來生成和CFO估算值。

下一個模塊會完成L-STF同步的第二個步驟。 收到數據包后,第一個模塊輸出端的關聯指標就會在高數值(代表L-STF字段)和低數值(代表移至先前的L-STF字段)之間轉換。 該模塊實現了一個差分器,可以把向下斜率轉換至峰值。 所產生的信號就會成為代碼中的關聯差異指標,該值也就是時序同步的指標。

第三個模塊用于判定是否已檢測到某個數據包。 一旦收到一個結構完整的802.11數據包,第二個模塊算出的關聯差異指標就會顯示一個峰值,對應于L-STF和L-LTF之間的轉換值。 閾值檢測可以在L-STF結尾和L-LTF開頭估算此位置,從而實現粗同步(在一個循環前綴內完成)。如果峰值在超過特定數量的連續樣本內保持在特定的閾值以上,此模塊就會判定檢測到802.11前導碼,并通過STF Found指示控件表示。

檢測到數據包之后,下一個模塊就會補償所有算法與實現延遲,將基于傳統短訓練字段(L-STF)的同步信號與抽取的I/Q樣本與CFO估算序列(由第一個模塊計算而得)進行對齊。 CFO估算會根據CFO估算序列和STF Found指示控件進行鎖存。 LTF字段第一個(估算的)元素之前的數據樣本會標示為無效。 這些數據流會發送至下一個模塊,也就是信道頻率偏置(CFO)修正模塊,以消除相鄰樣本之間累積起來的相位差。

下一個模塊OFDM選通器(OFDM strober)從估算的L-LTF第一個碼元開始。在每個OFDM碼元中,循環前綴(CP)樣本會標示為無效,從而消除CP。 選通功能一直持續到數據包中估算的所有OFDM碼元完成CP消除為止。 請注意,OFDM碼元的數量在傳統信號(L-SIG)字段中進行編碼,之后L-SIG會在接收鏈中完成解碼。

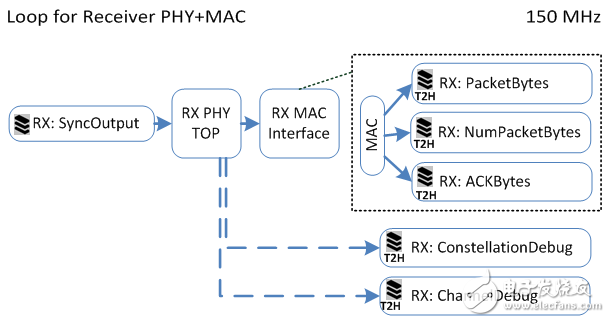

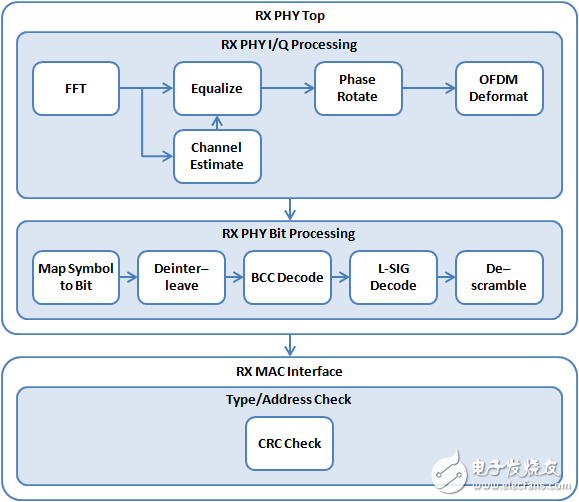

3.5.4 Receiver PHY+MAC循環

圖17顯示了Receiver PHY+MAC循環界面,圖18顯示了RX PHY Top和 RX MAC Top的程序框圖。

圖 17. Receiver PHY+MAC循環的輸入與輸出

處理鏈內第一個模塊就是FFT。 FFT會將所有有效的樣本轉換至頻域,逐個OFDM碼元地進行。

下一個模塊會處理副載波域的LTF碼元,以獲得信道響應的近似值來進行后續的迫零信道均衡。 該估算值會映射至兩個分量: 反向通道幅值和單位信道估算值。 使用這些分量即可降低均衡所需的位精確度。

基于信道估算,下一個模塊會通過迫零運算來均衡802.11 OFDM碼元。 完成均衡之后,即可通過導頻信號評估來消除每個OFDM碼元中的殘留CFO和相位漂移。

圖18: RX PHY Top和RX MAC Top程序框圖

完成相位修正之后,接收到的樣本就會進入OFDM反格式化器來移除所有的零子載波和導頻副載波,并在發射器的格式化器之前以相同的順序重新排列數據副載波。 這個反格式化器的輸出端提供了I/Q星座圖,可以傳輸至主機進行分析并調試。

進行反格式化之后,就會從QAM星座圖提取比特數據,并且去除交錯配置。 去交錯的比特流會進入Viterbi解碼器進行信道解碼。

下一個模塊會解碼并解讀L-SIG字段。 其中包含PHY參數,可能會隨著每個數據包而有所差異,例如調制與編碼機制(MCS)和數據包路徑。 接收器PHY區塊會在處理鏈的前幾個階段使用此信息,例如同步單元(如3.5.3小節所述)末端的OFDM選通模塊以及本小節的大部分區塊。 根據L-SIG估算的參數值可通過這些區塊的反饋路徑來提供。 代碼設計可確保參數會根據這些數值正確更新。 舉例來說,對于每個數據包,L-SIG會使用已知的MCS(BPSK,速率-1/2代碼)來發送。 參數必須根據L-SIG的估算值進行更新,并且應用至數據負載內的OFDM碼元。

最后,解碼后的比特經過解密轉送至MAC。

MAC端會根據MAC PDU所包含的四個FCS字節執行CRC檢查。 之后會檢查Type字段,以判斷是否接收到DATA數據包或ACK數據包。 然后將接收數據包的目標地址與站點的設備地址進行對比檢查。 如果CRC檢查和地址檢查通過的話,就會把接收到的數據包顯示給主機。 如果是DATA數據包的話,接收和提取的MAC SDU位字節加上源位址會通過target-to-host DMA FIFO RX: PacketBytes一同發送至主機。 接收到的數據包的大小也會通過target-to-host DMA FIFO RX: NumPacketBytes提供給主機。

4. 主機實現

802.11應用架構包含了一個頂層主機.gvi,用于配置FPGA、與FPGA交換負載數據以及監控系統狀態。

左上方的指示控件和輸入控件均已初始化。 之后就會生成一個會話,其中包含所有必要處理的參考信息。 所有循環在執行期間都會使用這個會話簇來交換數據或訪問FPGA資源。 只要按下停止(Stop)按鈕或出現錯誤,所有的While循環都會停止運行,會話中的所有處理操作都會關閉。

可能的參數設置請查看項目的文檔。

圖19. Host Top-Level VI程序框圖

4.1 主循環

此循環會根據主機前面板的當前設置來配置FPGA。 循環會將發射隊列(Transmit Queue)的數據傳輸至FPGA發射器,并把FPGA接收器的解碼數據放入接收隊列(Receive Queue)。 如果系統不是在RF環回模式運行,就會忽略發射或接收部分。 主循環還會進一步更新主機前面板的顯示項目,以反映當前的系統狀態。

4.2 自動增益控制

主循環會連續監控所收到的信號功率,并且相應地調整RX路徑的增益。

4.3 RF與802.11 IP配置

此循環用于設置頻率、功率電平和增益,可針對發射器和接收器配置NI USRP RF前端裝置。 此外還會更新前面板來顯示目前的RF狀態。

4.4 吞吐量測量

數據通過UDP送出去時,此循環就會監控接收器端的吞吐量。

4.5 UDP數據讀寫

一旦啟用上循環,即可處理接收隊列的數據,并且通過UDP將數據發送出去。 下循環可以把隨機數據的常數數據包(PN模式)或接收到的UDP數據包(UDP 模式)放入發射隊列。 主循環會使用這兩個隊列來與FPGA交換數據。

4.6 停止執行

執行主機VI時,所有循環都會并行運行。 只要按下停止(Stop)按鈕,該操作就會在最后一個循環被捕獲,同時通過其他隊列同步至所有其他循環。 每個循環都包含連接至循環條件終端的檢錯停止(check stop)模塊,如果按下停止按鈕或出現錯誤,就會退出該循環。

5. 結論

LabVIEW Communications 802.11應用架構1.0提供了兩個在NI SDR硬件上運行的站點之間的實時802.11鏈路。此應用架構通過利用現有鏈路和只需修改或添加所需部分,可幫助用戶專心于特定領域的研究。

基于LabVIEW的靈活性和該框架的模塊化特性,用戶可輕松互換設計的某些部分,以便針對未來的無線系統開發新的算法。除此之外,由于LabVIEW固有地連接了主機和FPGA,設計還可進行分區,以便充分利用FPGA的并行執行功能和主機的計算性能。

這個架構為無線研究和原型開發提供了豐富的起點。 立即下載LabVIEW Communications評估版: ,開始您的開發。

如有問題, 請發送電子郵件至 [email protected] 。

6. 縮略詞表

ACK

Acknowledge(確認)

AGC

Automatic Gain Control(自動增益控制)

BCC

Binary Convolutional Code(二進制卷積碼)

BPSK

Binary Phase Shift Keying(二進制相移鍵控)

CP

Cyclic Prefix(循環前綴)

CRC

Cyclic Redundancy Check(循環冗余校驗碼)

DMA

Direct Memory Access(直接內存訪問)

FCS

Frame Check Sequence(幀校驗序列)

FFT

Fast Fourier Transform(快速傅立葉變換)

FIFO

First In First Out(先進先出)

FPGA

Field Programmable Gate Arrays(現場可編程門陣列)

GVI

Graphical Virtual Instrument(圖形化虛擬儀器)

IEEE

Institute of Electrical and Electronics Engineers(電氣電子工程師協會)

IFFT

Inverse Fast Fourier Transform(快速傅立葉逆變換)

I/Q

Inphase/Quadrature(同相/正交)

ISI

Intersymbol Interference(碼間干擾)

L-LTF

Legacy Long Training Field(傳統長訓練字段)

LSB

Least Significant Bit(最低有效位)

LTF

Long Training Field(長訓練字段)

L-SIG

Legacy Signal Field(傳統信號字段)

L-STF

Legacy Short Training Field(傳統短訓練字段)

MAC

Medium Access Control(媒體訪問控制)

MCS

Modulation and Coding Scheme(調制和編碼機制)

MS/s

Mega Samples Per Second(每秒兆次采樣)

OFDM

Orthogonal Frequency Division Multiplexing(正交頻分復用)

PDU

Protocol Data Unit(協議數據單元)

PHY

Physical Layer(物理層)

QAM

Quadrature Amplitude Modulation(正交調幅)

QPSK

Quaternary Phase Shift Keying(四進制相移鍵控)

RX

Receiver(接收器)

SDR

Software Defined Radio(軟件無線電)

SDU

Service Data Unit(服務數據單元)

SIFS

Short Inter Frame Space(短幀幀間間隔)

SISO

Single Input Single Output(單輸入單輸出)

STF

Short Training Field(短訓練字段)

TX

Transmitter(發射器)

UDP

User Datagram Protocol(用戶數據報協議)

VHT

Very High Throughput(超高吞吐量)

查看802.11應用架構的價格信息

查看LabVIEW Communications系統設計套件的價格信息

電子發燒友App

電子發燒友App

評論